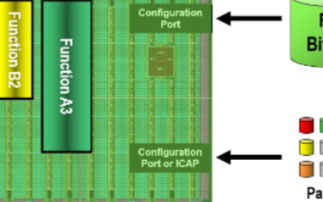

部分可重構(gòu)技術(shù)是Xilinx FPGA的一項(xiàng)重要開(kāi)發(fā)流程。本文結(jié)合Virtex5 FPGA,詳細(xì)講解在ISE + Planahead上完成部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)。

1.測(cè)試用例

本測(cè)試用例為驗(yàn)證 Xilinx FPGA部分可重構(gòu)功能而定制。

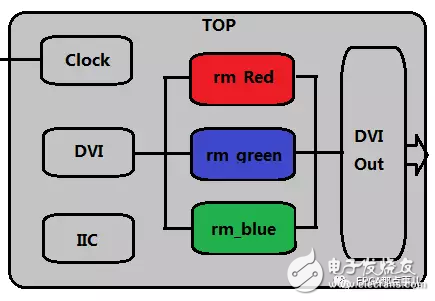

代碼整體結(jié)構(gòu)如下:

主要功能是,內(nèi)圖產(chǎn)生自測(cè)圖像,通過(guò)DVI接口輸出,并同時(shí)點(diǎn)亮3個(gè)LED燈。其中靜態(tài)邏輯(Static,灰色部分)負(fù)責(zé)頂層集成,時(shí)鐘處理,IIC輸出控制接口芯片,產(chǎn)生內(nèi)部測(cè)試圖像并輸出顯示。彩色的部分是可重構(gòu)邏輯,分別為Red,Blue,和Green三個(gè)模塊,代表對(duì)三個(gè)色彩通道分別進(jìn)行處理的邏輯。

2. ISE流程

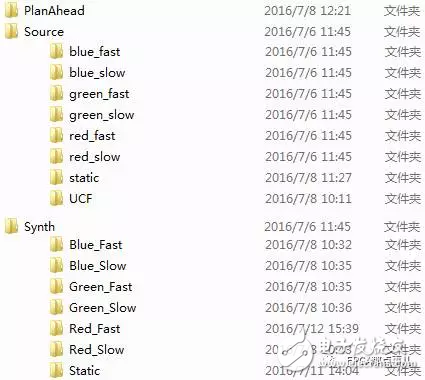

部分可重構(gòu)開(kāi)發(fā)流程會(huì)用到2個(gè)工具ISE和Planahead。其中ISE負(fù)責(zé)把靜態(tài)邏輯,和各個(gè)重構(gòu)模塊,分別獨(dú)立綜合成網(wǎng)標(biāo)文件,提供給Planahead使用。

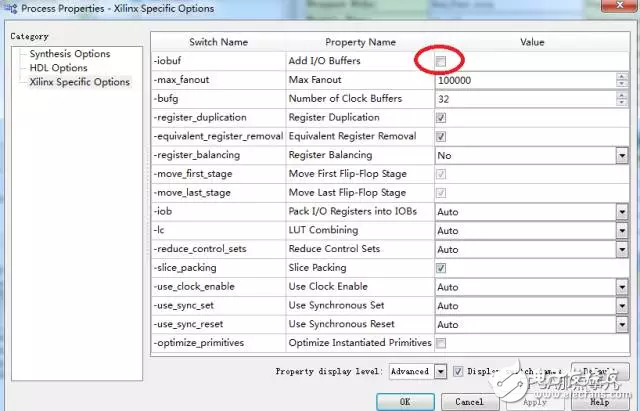

綜合的時(shí)候要尤其注意,靜態(tài)邏輯Static是可以加管腳約束的,各個(gè)重構(gòu)模塊邏輯綜合時(shí),要選擇不添加IO buffer,如下圖所示:

各個(gè)模塊的ISE工程已經(jīng)在Synth文件夾下組織好了,可以直接用ISE14.7打開(kāi)。

3.Planahead流程

部分可重構(gòu)的主要工作都在Planahead下完成,大體分成4個(gè)步驟:

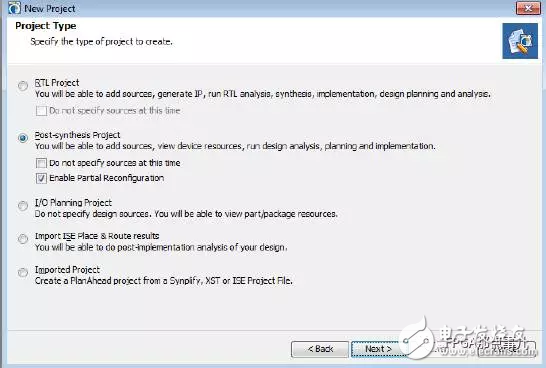

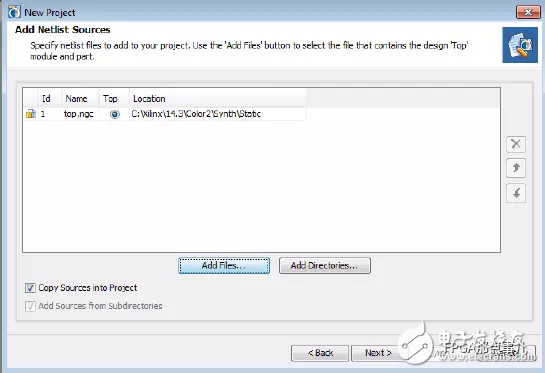

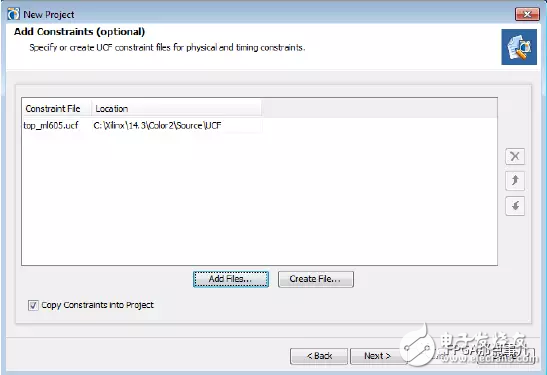

A.建立Planahead工程,導(dǎo)入Static靜態(tài)網(wǎng)表和約束文件

首先打開(kāi)Planahead,選擇建立新網(wǎng)表工程,確定Enable PartialReconfiguration功能打開(kāi)。

然后依次加入頂層Static網(wǎng)表和ucf約束文件:

B.導(dǎo)入Reconfiguration網(wǎng)表文件并設(shè)置Partition

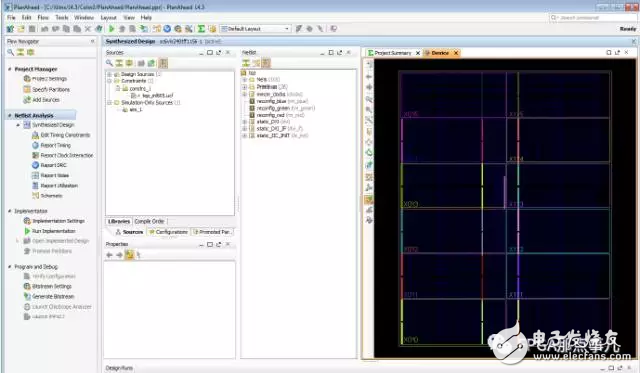

創(chuàng)建完成Planahead工程后,在Flow Manager中,選擇Open SynthesizedDesign打開(kāi)網(wǎng)表設(shè)計(jì):

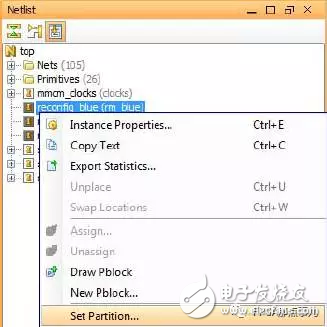

接下來(lái),我們要添加各個(gè)可重構(gòu)的網(wǎng)標(biāo)文件。選中netlist列表中的某個(gè)可重構(gòu)子Module(此時(shí)它是Black Box,什么都沒(méi)有),右鍵選擇Set Partition:

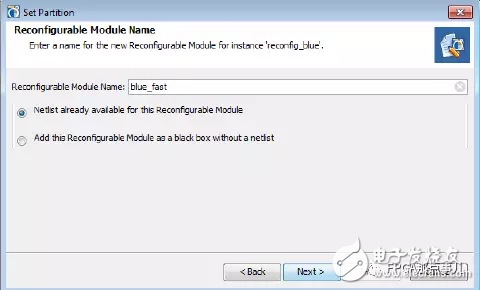

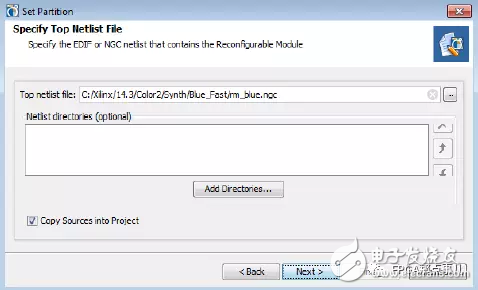

在彈出對(duì)話框中,設(shè)置比可重構(gòu)Module某個(gè)實(shí)現(xiàn)的名字,Next后選擇對(duì)應(yīng)網(wǎng)表:

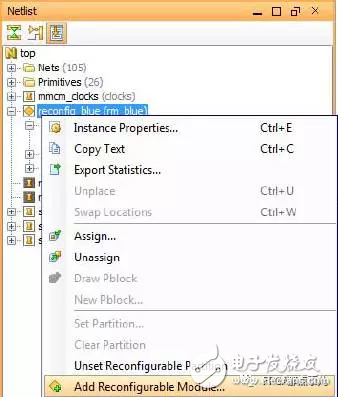

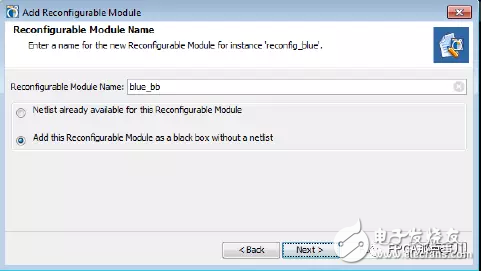

接下來(lái)我們還可以在同一個(gè)Module下面,繼續(xù)添加其它不同實(shí)現(xiàn)的網(wǎng)表文件,也可以添加Black Box網(wǎng)表(即空網(wǎng)表):

依次把所有的網(wǎng)表都添加完畢,最終,在Source窗口,視圖如下:

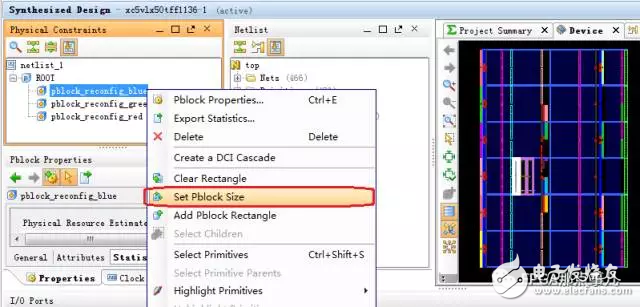

C.設(shè)置Partition

接下來(lái),我們給3個(gè)Partition,分別設(shè)置其物理區(qū)域。使用Set Pblock Size選項(xiàng),在Device視圖中,劃定合適的物理區(qū)域即可:

物理區(qū)域中會(huì)包含多種資源,不需要的我們可以不勾選,這樣能減小最終bit文件的大小:

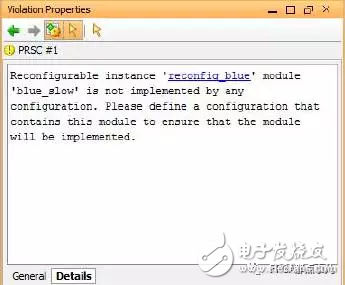

設(shè)置完所有的partition后,可以跑一下DRC檢查(Tools-》 ReportDRC),確保所有的設(shè)置都沒(méi)有問(wèn)題:

DRC檢查結(jié)果:

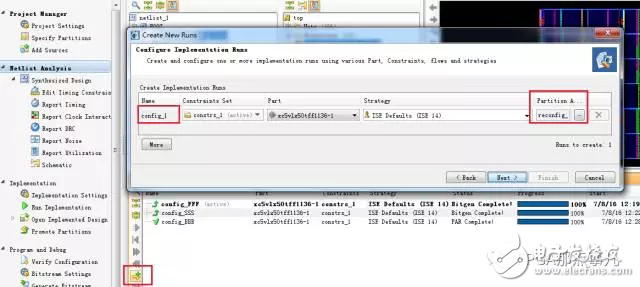

D.創(chuàng)建Implementation Runs

最后我們創(chuàng)建ImplementationRuns,在此處可以創(chuàng)建不同的組合。

創(chuàng)建完成后,就可以跑Implementation布局布線了,跑完后每個(gè)run下都會(huì)生成多個(gè)bit文件,其中之一是全局的配置bit,另外多個(gè)是部分重構(gòu)的bit文件。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22040瀏覽量

618172 -

Virtex5

+關(guān)注

關(guān)注

0文章

6瀏覽量

8779

發(fā)布評(píng)論請(qǐng)先 登錄

賽靈思發(fā)布ISE12.2強(qiáng)化部分可重配置FPGA技術(shù)

支持重構(gòu)的FPGA器件

誰(shuí)有Virtex5 FPGA到TI公司64系列的EMIF設(shè)計(jì)文檔??

求xilinx virtex5例程

使用ISE處理Virtex 5 LX110T FPGA為什么ISE WebPack中沒(méi)有可用的選項(xiàng)?

IDDR最大速度為virtex5 sx95t

請(qǐng)問(wèn)Xilinx FIFO支持virtex5嗎?

Virtex5無(wú)法正確讀取XCF32P是為什么?

數(shù)據(jù)是存儲(chǔ)在Virtex5部分還是存儲(chǔ)在板上的SRAM內(nèi)存中?

ML561如何使用ISE

在Virtex5中清除部分配置存儲(chǔ)器時(shí),請(qǐng)問(wèn)DONE引腳的行為是什么?

求virtex5與部分重新配置教程?

以Virtex5開(kāi)發(fā)板和SPI FLASH為基礎(chǔ)的FPGA多重配置分析

FPGA動(dòng)態(tài)可重構(gòu)技術(shù)是什么,局部動(dòng)態(tài)可重構(gòu)的時(shí)序問(wèn)題解決方案

Virtex5 FPGA在ISE + Planahead上部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)

Virtex5 FPGA在ISE + Planahead上部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)

評(píng)論