SDRAM的發展經歷

SDRAM(Synchronous Dynamic Random Access Memory),即同步動態隨機存取存儲器,是計算機系統中使用最廣泛的內存類型之一。它的發展歷程可以追溯到多個技術迭代,每個階段都帶來了性能上的顯著提升。

第一階段:SDR SDRAM

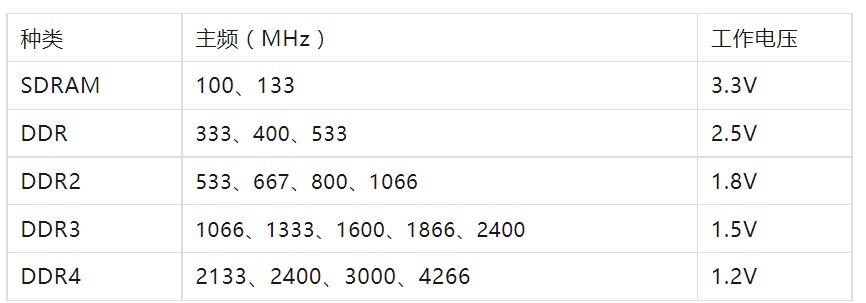

SDR SDRAM(Single Data Rate Synchronous Dynamic Random Access Memory)是SDRAM的最初形態,采用單端(Single-Ended)時鐘信號進行數據傳輸。SDR SDRAM的時鐘頻率直接決定了數據的讀寫速率,如PC100和PC133分別表示時鐘信號為100MHz和133MHz,數據讀寫速率也相應為100MB/s和133MB/s。SDR SDRAM的出現標志著內存技術向同步化方向發展的重要一步,但與后續的技術相比,其數據傳輸速率仍顯不足。

第二階段:DDR SDRAM

DDR(Double Data Rate)SDRAM的推出是內存技術的一次重大飛躍。DDR SDRAM采用了雙倍數據速率技術,即在時鐘信號的上升沿和下降沿都能傳輸數據,從而實現了數據傳輸速率的翻倍。DDR SDRAM的命名規則也發生了變化,如DDR200、DDR266等,表示的是等效數據傳輸速率(即實際工作頻率的兩倍)。DDR SDRAM的引入極大地提升了系統的整體性能,成為了當時的主流內存技術。

第三階段:DDR2 SDRAM

DDR2 SDRAM在DDR SDRAM的基礎上進行了進一步的優化和升級。它采用了更低的工作電壓(1.8V),減少了功耗和發熱量;同時,DDR2還引入了更先進的預取技術(Prefetch),提高了數據傳輸效率。DDR2 SDRAM的命名規則也延續了DDR的傳統,如DDR2-400、DDR2-667等,表示的是等效數據傳輸速率。DDR2 SDRAM的普及進一步推動了計算機系統的性能提升,成為了市場上的主流內存產品。

第四階段:DDR3 SDRAM

DDR3 SDRAM在DDR2的基礎上再次進行了技術革新。它采用了更先進的8-bit Prefetch技術,進一步提高了數據傳輸效率;同時,DDR3還降低了工作電壓(通常為1.5V),進一步減少了功耗和發熱量。DDR3 SDRAM的命名規則也發生了變化,如DDR3-1066、DDR3-1600等,直接以等效數據傳輸速率命名。DDR3 SDRAM的推出不僅提升了系統的整體性能,還推動了計算機技術的進一步發展。

第五階段:DDR4 SDRAM及以后

DDR4 SDRAM在2015年左右開始進入消費市場,相較于DDR3而言,DDR4在速度、功耗和容量等方面都有了顯著提升。DDR4采用了更低的工作電壓(通常為1.2V),進一步降低了功耗;同時,DDR4還引入了更高效的時序參數和預取技術,使得數據傳輸效率更高。DDR4的命名規則繼續沿用DDR3的傳統,如DDR4-2133、DDR4-3200等。隨著技術的不斷進步,DDR5、DDR6等更高性能的內存技術也已經在研發中,并有望在未來幾年內推出。

SDRAM的工作原理

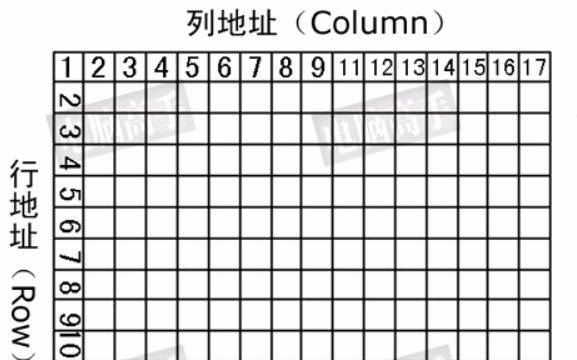

SDRAM的工作原理主要包括地址傳輸、行激活、列讀取/寫入、數據傳輸、預充電和刷新操作等步驟。以下是對這些步驟的詳細解析:

1. 地址傳輸

CPU通過地址總線向SDRAM發送行地址和列地址。這些地址信息用于指定要訪問的存儲單元的具體位置。

2. 行激活

根據接收到的行地址,SDRAM將對應的存儲體中的一行數據激活并讀取到內部的行緩沖區中。這個過程被稱為行激活或行選通(Row Activation)。在行激活后,該行數據就被緩存在行緩沖區中,等待進一步的列操作。

3. 列讀取/寫入

在確定行之后,通過列地址選擇要操作的具體數據位進行數據的讀取或寫入操作。這個過程被稱為列讀取(Column Read)或列寫入(Column Write)。在列讀取操作中,指定的數據位被從行緩沖區中讀取出來并通過數據總線傳輸到CPU或其他設備;在列寫入操作中,數據通過數據總線傳輸到行緩沖區中并寫入到指定的數據位。

4. 數據傳輸

在時鐘信號的同步下,數據沿著數據總線進行傳輸。SDRAM采用與外部時鐘信號同步的方式來傳輸數據,這保證了數據傳輸的穩定性和可靠性。

5. 預充電

完成一次操作后(無論是讀取還是寫入),對已激活的行進行預充電操作。預充電的目的是為了關閉當前行的激活狀態并為下一次行激活做準備。通過預充電操作可以減少行之間的干擾并提高內存的訪問效率。

6. 刷新操作

定期對存儲單元進行刷新操作以保持數據的有效性。由于SDRAM采用電容來存儲二進制位信息而電容存在漏電現象因此需要定期對存儲單元進行刷新以保持數據的正確性。刷新操作通常由內存控制器自動完成無需用戶干預。

工作原理的深入解析

1. 內部結構與組織

SDRAM內部由多個存儲體(Bank)組成,每個存儲體包含多個行(Row)和列(Column)。每個行對應一個行緩沖區,用于緩存該行中的數據。當CPU發起內存訪問請求時,首先通過地址總線發送行地址和列地址到SDRAM控制器。控制器根據地址信息激活相應的行,并將數據讀取到行緩沖區中。然后,通過列地址選擇要讀取或寫入的數據位,并進行數據傳輸。

2. 時鐘同步與數據管道

SDRAM的數據傳輸是與時鐘信號同步的。時鐘信號由外部時鐘源提供,并作為SDRAM內部操作的基準。在時鐘信號的驅動下,數據沿著數據總線以一定的速率進行傳輸。為了提高數據傳輸效率,SDRAM通常采用數據管道技術,即在時鐘信號的每個周期內傳輸多個數據位(如8位或16位)。

3. 刷新機制

由于SDRAM使用電容來存儲數據,而電容存在漏電現象,因此需要定期對存儲單元進行刷新以保持數據的正確性。刷新操作通常由內存控制器自動完成,并在不影響正常讀寫操作的情況下進行。刷新周期根據電容的漏電速度和存儲單元的穩定性來確定,以確保在數據丟失之前完成刷新。

4. 命令解碼與執行

SDRAM控制器負責接收來自CPU的命令(如行激活、列讀取/寫入、預充電和刷新等),并對這些命令進行解碼和執行。控制器內部包含復雜的邏輯電路和時序控制單元,以確保命令的正確執行和數據傳輸的穩定性。

DDR5及未來展望

DDR5 SDRAM作為最新的內存標準,已經在高端服務器和消費者市場上開始普及。DDR5帶來了多項關鍵改進,包括更高的數據傳輸速率、更低的電壓和功耗、更大的容量以及增強的錯誤校正和數據保護機制。

- 更高的數據傳輸速率 :DDR5引入了更先進的信號完整性和時序優化技術,使得數據傳輸速率得到了顯著提升。目前市場上的DDR5內存模塊已經能夠達到4800MT/s以上的速度,未來還將進一步提升。

- 更低的電壓和功耗 :DDR5采用了更低的操作電壓(通常為1.1V),進一步降低了功耗和發熱量。這有助于提升系統的整體能效比,并延長電池續航時間(在移動設備上)。

- 更大的容量 :DDR5支持更大的內存容量,以滿足日益增長的數據處理需求。隨著技術的進步,未來我們可能會看到更大容量的DDR5內存模塊,以滿足高性能計算和大數據應用的需求。

- 增強的錯誤校正和數據保護 :DDR5引入了更強大的錯誤校正碼(ECC)和其他數據保護機制,以提高系統的可靠性和穩定性。這對于需要高可靠性的應用場景(如數據中心和服務器)尤為重要。

總結與展望

SDRAM作為計算機系統中不可或缺的組成部分,其發展歷程見證了計算機技術的飛速進步。從SDR SDRAM到DDR5,每一次技術迭代都帶來了顯著的性能提升和更好的用戶體驗。未來,隨著計算機技術的不斷發展,我們可以期待更高性能、更低功耗、更大容量的內存技術的出現。這些新技術將進一步推動計算機系統的性能提升和應用的拓展,為我們帶來更加豐富多彩的數字化生活。

-

SDRAM

+關注

關注

7文章

441瀏覽量

56039 -

存儲器

+關注

關注

38文章

7636瀏覽量

166449 -

計算機

+關注

關注

19文章

7632瀏覽量

90216

發布評論請先 登錄

一文搞懂DDR SDRAM工作原理

SDRAM的工作原理

SDRAM設計詳細說明

使用Verilog實現基于FPGA的SDRAM控制器

關于SDRAM電路的設計

SDRAM工作原理 DRAM控制器系統設計架構

簡談 SDRAM的工作原理

簡談 SDRAM的工作原理

DDR SDRAM工作原理簡介

SDRAM工作原理 SDRAM布局布線說明

SDRAM的發展經歷和工作原理

SDRAM的發展經歷和工作原理

評論