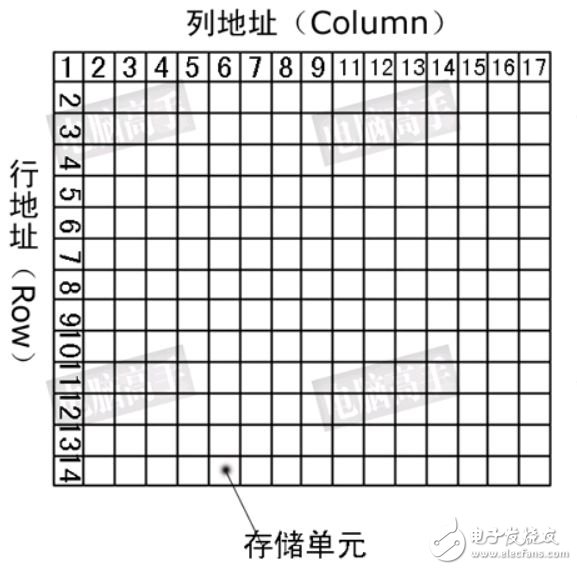

介紹SDRAM電路設(shè)計(jì)之前先了解下SDRAM的尋址原理。SDRAM內(nèi)部是一個存儲陣列,可以把它想象成一個表格,和表格的檢索原理一樣,先指定行,再指定列,就可以準(zhǔn)確找到所需要的存儲單元,這是內(nèi)存芯片尋址的基本原理,這個表格稱為邏輯Bank。由于技術(shù)、成本等原因,不可能只做一個全容量的Bank,而且由于SDRAM工作原理限制,單一的Bank會造成非常嚴(yán)重的尋址沖突,大幅降低內(nèi)存效率,所以在SDRAM內(nèi)部分割成多個Bank,目前的SDRAM基本都是4個Bank。存儲陣列示意如圖1所示:

圖1SDRAM存儲陣列示意圖

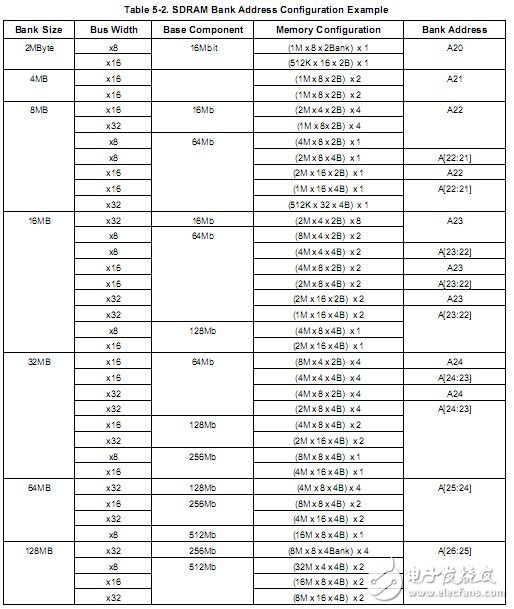

圖2SDRAM引腳配置方案

圖2是S3C2440A手冊提供的SDRAMbank地址的配置方案,維護(hù)系統(tǒng)使用的SDRAM是HY57V561620FTP-H,它的規(guī)格是4*4M*16bit(使用兩片是為了配置成32位的總線寬度),BANK大小是4M*16=64MB,總線寬度是32位,器件大小是4*BANK大小=256Mb,寄存器配置就是(4M*16*4B)*2,根據(jù)圖2可知,SDRAM上的BANK地址引腳(BA[1:0])與S3C2440的A[25:24]相連。

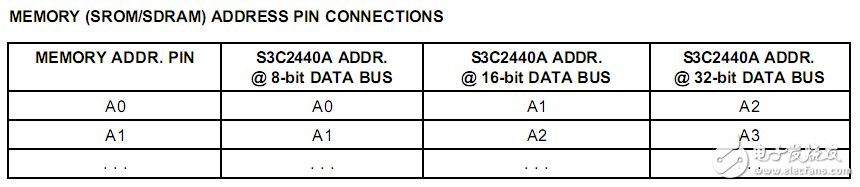

圖3 S3C2440A控制地址總線連接

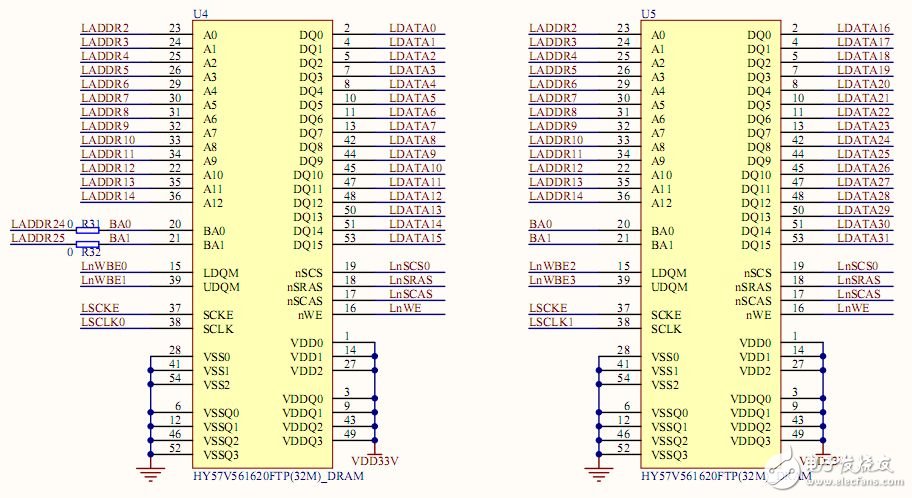

圖3是寄存器控制地址總線連接方式,我們使用2片SDRAM配置成32位的總線寬度,所以SDRAM上的A[12:0]接到S3C2440的A[14:2]引腳。具體的SDRAM電路連接如圖4所示:

圖4SDRAM電路連接圖

SDRAM的地址引腳是復(fù)用的,在讀寫SDRAM存儲單元時,操作過程是將讀寫地址分兩次輸入到芯片中,每一次由同一組地址線送入,兩次送入到芯片上去的地址分別稱為行地址和列地址,它們被鎖存到芯片內(nèi)部的行地址鎖存器和列地址鎖存器。下面是該芯片的部分信號

-

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56032

發(fā)布評論請先 登錄

SDRAM連接電路設(shè)計(jì)詳解

XILINX 關(guān)于FPGA 對DDR SDRAM 的設(shè)計(jì)文檔

關(guān)于FPGA讀寫SDRAM問題?

如何實(shí)現(xiàn)Reg istered SDRAM接口電路的設(shè)計(jì)?

關(guān)于STM32F429控制SDRAM

SDRAM設(shè)計(jì)詳細(xì)說明

關(guān)于SDRAM的時序控制研究方案分析

DRAM、SDRAM及DDR SDRAM之間的概念詳解

關(guān)于SDRAM的基本概念講解

FPGA讀寫SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文

數(shù)碼相框的SDRAM存儲電路電路圖免費(fèi)下載

關(guān)于SDRAM內(nèi)存條時序特點(diǎn)的詳細(xì)介紹

(網(wǎng)盤)關(guān)于SDRAM和錄音機(jī)等FPGA視頻

關(guān)于SDRAM電路的設(shè)計(jì)

關(guān)于SDRAM電路的設(shè)計(jì)

評論