一博高速先生成員:王輝東

“三面青山一面湖,無盡煙波畫舫浮。”說的是巢湖,到了合肥怎能不去巢湖看看呢。

周末休息,大剛說我開車,小胡(麗華)說我也去。

大剛說走就走,秒開車,不停留。

我們驅車向東南方向出發。

環湖公路風景秀麗,一路歡聲笑語。

正行之間,忽聽電話鈴聲響起。

小胡華麗麗的拿起手機。

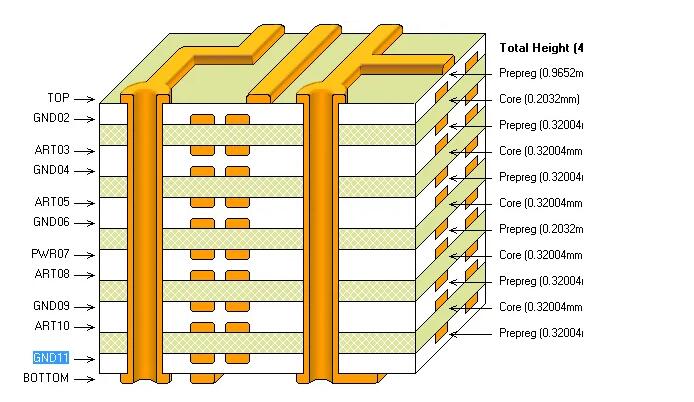

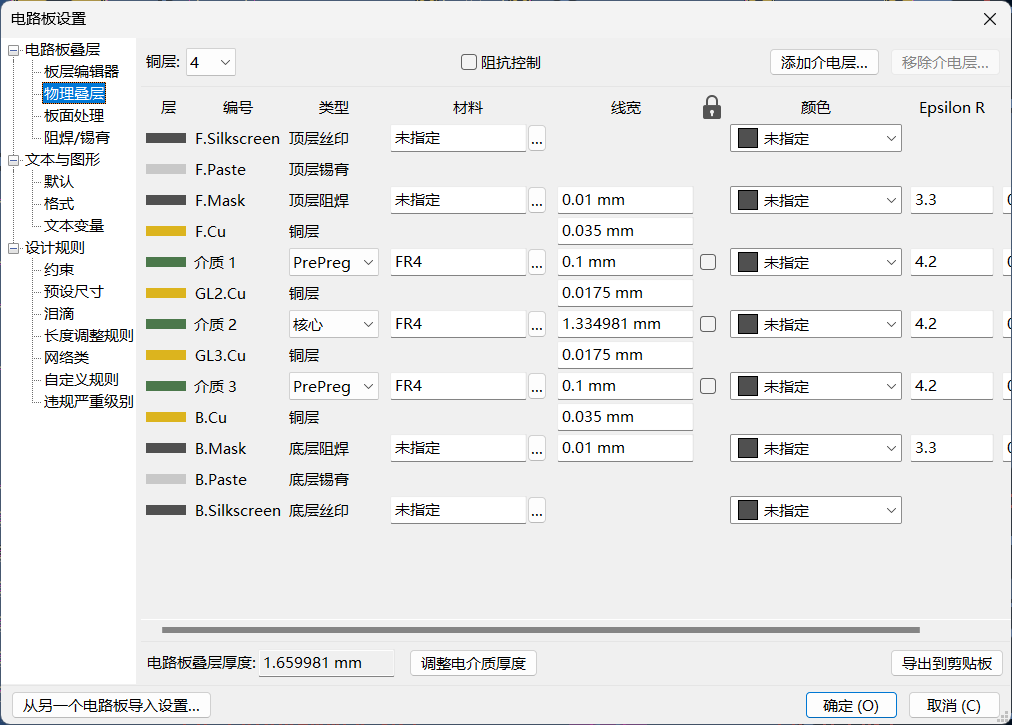

客戶說他們線路板廠發過來個工程確認,其中有個高速PCB的層疊幫忙確認下。

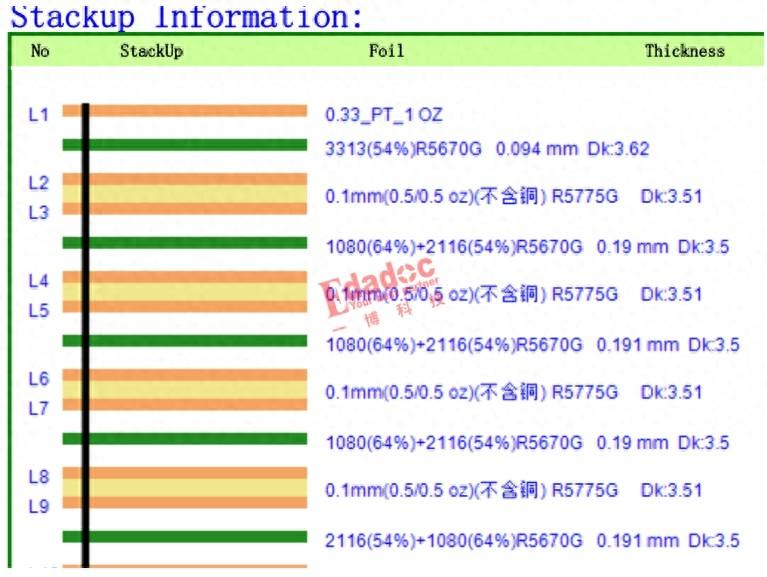

猛一看,感覺工廠的層疊設計合情合理,但是仔細一看,感覺少了點東西,小胡除了看到各層銅厚的數據,沒有找到銅箔類型的信息。

這種看似合理的層疊確認背后,隱藏著什么秘密。

小胡是東瞅瞅,西望望,怎么不見銅箔類型,找的好心慌。

小胡說讓客戶再和工廠確認下,為什么不寫銅箔類型。

PCB設計時的明明有銅箔類型的要求。

PCB設計要求用松下M6G的材料,內層用HVLP銅箔。

工程確認不寫銅厚信息有哪些問題呢,這還要從銅箔類型說起。

高速PCB的銅箔類型介紹:

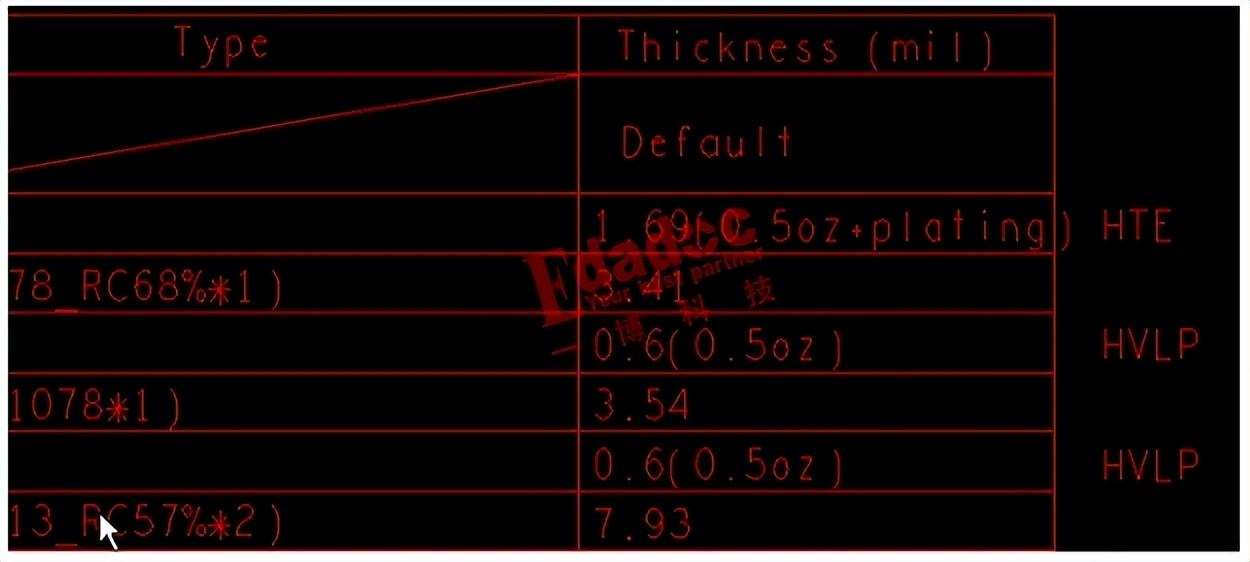

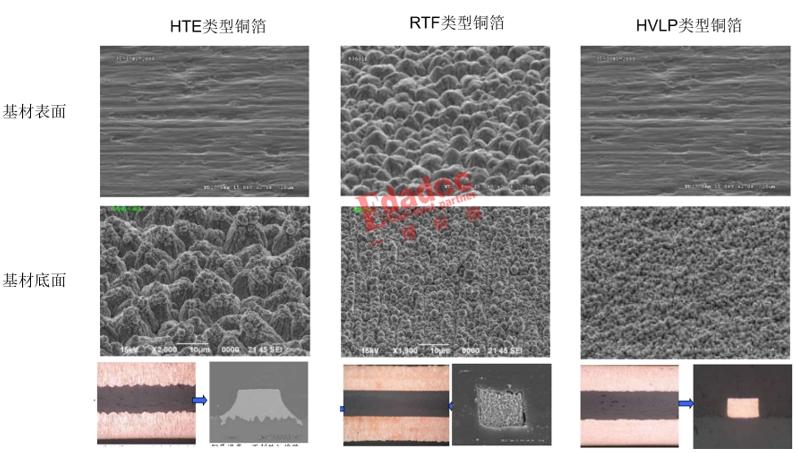

我們高速pcb層疊設計時,常用銅箔有如下幾種,HTE RTF 和HVLP。

松下M6G的材料手冊上明確標示,有兩種銅箔類型,你是否有注意到。

為此大師兄專門找了松下的華總確認過,松下和我們是戰略合作。

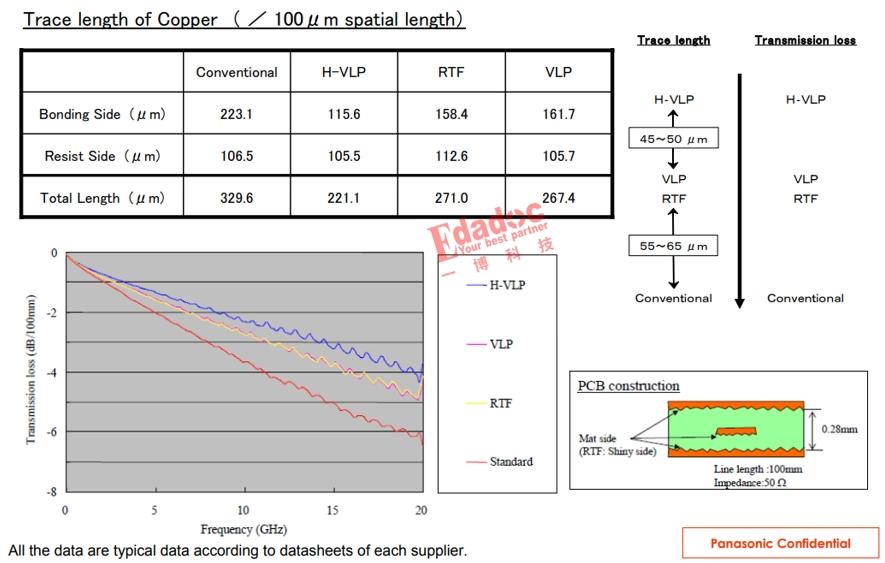

松下第一時間提供了不同銅箔類型的損耗對比資料。

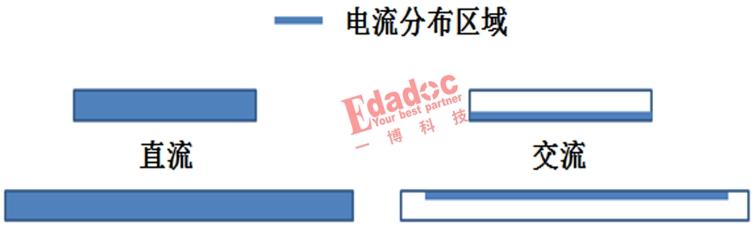

由于信號在頻率越來越高的情況下,電流在傳輸路徑上會重新調整分布,沿著最小電阻的路徑去傳輸。

當信號的頻率較越來越高時,信號都會趨向于導體的表面傳遞。這樣就會導致信號流過導體的相對有效面積變小,從電阻的角度來分析,這就會導致電阻增加,

導致傳遞能量的損失。 電流大量聚集在導體的表面上,越往導體中心電流越小,這種現象稱為“趨膚效應”。

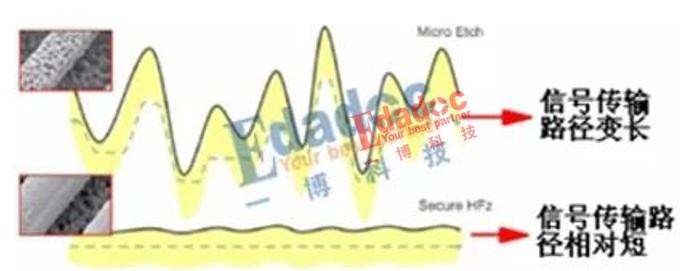

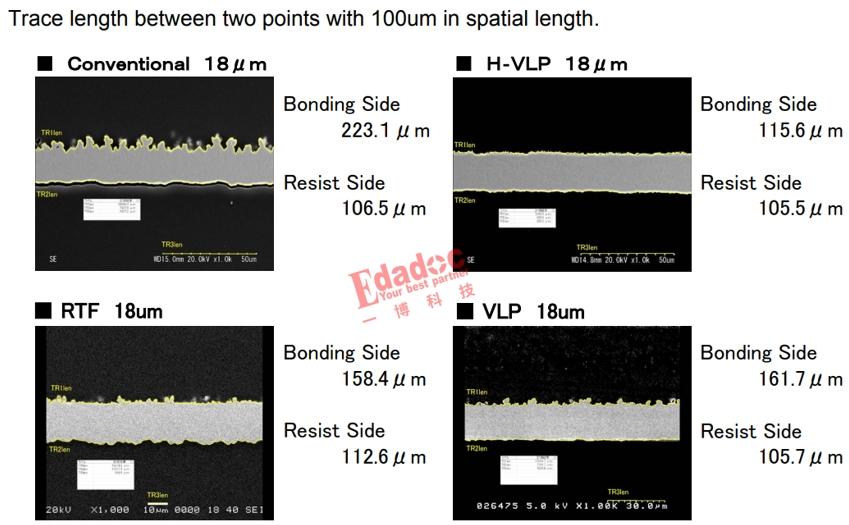

如果導體表面粗糙度大于趨膚深度時,信號傳輸僅在粗糙度的厚度范圍內進行,使傳輸信號的駐波、反射越來越嚴重,并導致信號傳輸路徑變長,增加傳輸損耗。

信號在導體表面粗糙度低于趨膚深度時,傳輸路徑短,降低傳輸損耗因此,導體銅箔粗糙度越低,制作出的PCB產品插入損耗(傳輸損耗)越低。

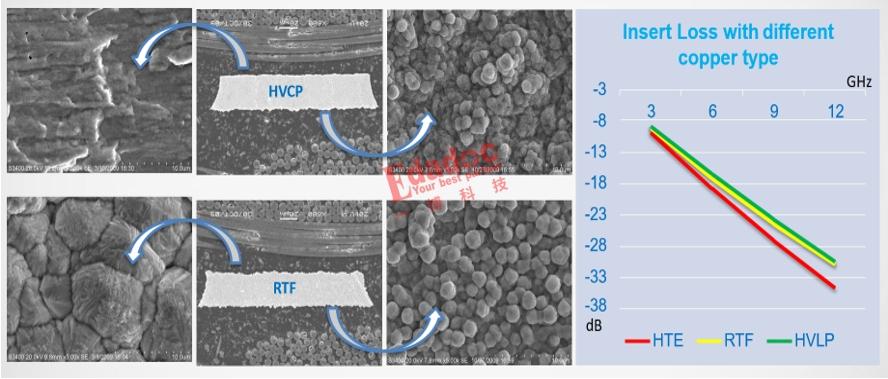

當信號沿著傳輸線傳播時,會發生了嚴重的趨膚效應和電離損耗。下圖是兩種銅箔類型和插損的對比。

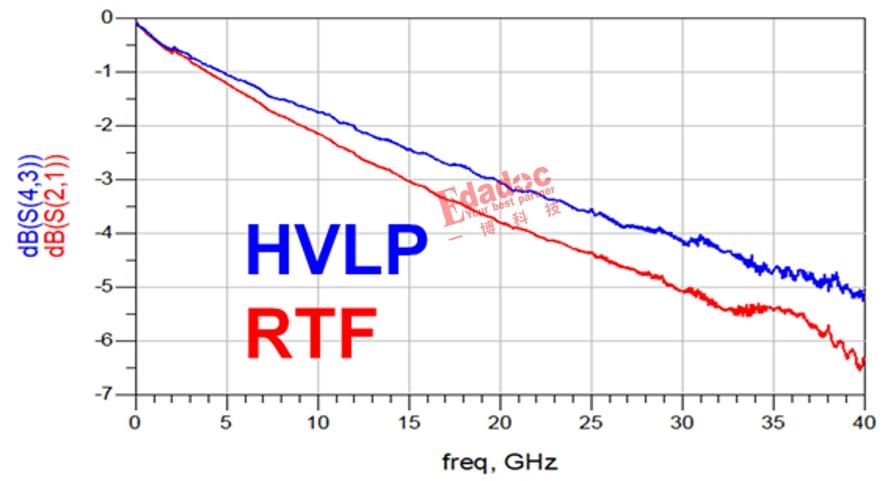

高速先生Chris曾經做過一個很有意思的測試,在同一個疊層且線寬等條件都不變的情況下,實測出了RTF 銅箔和 HVLP銅箔之間的差異。

由于趨膚效應的存在,高速PCB如果繼續使用常規銅箔,其結果是:隨信號傳輸頻率增加,趨膚效應導致的信號“失真”愈發嚴重。因此,當前的高速材料上低

粗糙度銅箔的應用越來越廣泛。

頻率越高、波長越短,信號在導體間行進,將只集中在導體的表面。表面粗糙度越平坦對信號傳輸越有利。PCB層間的附著力強度,受導體表面粗糙度影響。但是

導體表面粗糙度越高,樹脂與導體接觸面積越大,附著力隨之增加,這就是生產與設計的矛盾。

關于不同粗糙度銅箔對高速PCB信號的影響,小胡那是體會最深。

她說走巢湖環湖公路6公里,一路平坦道路開闊,開車那是刷刷而過,到了湖邊也是6公里,一路坑坑洼洼,那速度就是龜速,路程一樣,用時差很多,到達時間也

差了很多,一目了然。后來客戶電話打了過來,告訴小胡,工廠說不寫銅箔類型,他們在生產時是多一種選擇。

小胡一時凝噎

麗華喝了一口酒,滿眼淚痕和溫柔,老王說喝完這一杯,我們去河邊走一走。

細節經不起推敲,高速PCB的銅箔類型還請PCB工廠大方的展示出來,不要藏著掖著。

建議按下面的層疊設計來確認工程。

所以有的工廠說這是多一種考慮,這樣做真的好嗎,你能接受嗎。

振河塔,高聳入云,說著這世間的正道和陽剛。

另外說了這么多,忘記告訴大家一件事,RTF和HVLP銅箔在高速PCB層疊設計上,不但損耗有差異,價格上也有很大的不同,哪個更貴,朋友你知道嗎。

如果你還不清楚,那么好機會來了,這周五在合肥有一場高速PCB的技術研討會,我們一起來聊聊這方面事。

審核編輯 黃宇

-

銅箔

+關注

關注

5文章

223瀏覽量

16820 -

高速PCB

+關注

關注

4文章

102瀏覽量

25379

發布評論請先 登錄

PCB層疊結構設計的先決條件

高層數層疊結構PCB的布線策略

舵機精準定位背后的秘密

探秘高純度銅箔,解鎖高品質 PCB 的性能密碼

PCB 設計規則、層疊結構的導入/導出

谷歌和Meta秘密廣告交易被歐洲監管機構調查

0.4mm層疊封裝(PoP)封裝的PCB組裝指南,第二部分

0.5mm層疊封裝應用處理器的PCB組裝指南,第II部分

秘密背后的秘密-高速PCB的層疊確認時,工廠為何不寫銅箔類型

秘密背后的秘密-高速PCB的層疊確認時,工廠為何不寫銅箔類型

評論