2024年6月25日 周二 19:00-20:30中星聯華科技將舉辦《深度解析高速串行信號的誤碼測試》“碼”上行動系列線上講堂。

將深入講解當前高速信號的發展趨勢、挑戰及難點,分析高速串行信號傳輸的原理并講解如何進行高速串行信號的誤碼測試,帶您全面掌握高速誤碼分析儀的基本概念、原理、框架,并剖析如何通過誤碼分析儀注抖和加噪來完成壓力眼測試,同時將與大家探討高速誤碼分析儀的典型應用如高速互聯、高速芯片、數據中心、高速背板、光模塊、光通信等。

關于高速串行信號的誤碼測試

隨著數字電路工作速度的提高,PCB、連接器、背板上信號的傳輸速率也越來越高,其中串行數據通信在傳輸中占據主導地位。按照最嚴格性能標準制造的擁有精密設計的各種高速互連的PCIE/ETH/VPX背板,以及高速線纜,在當今社會對于高速信號需求普遍存在的大背景下變得至關重要。背板是嵌入式系統中的通信主干,必須按照嚴格的信號完整性標準進行設計,以確保系統內模塊之間及時、準確的數據傳輸。

高速IEEE ETH以太網主流速率已經從10G支持到100G、200G、400G,消費電子類的高速總線USB3/4/PCIE6的信號速率已經覆蓋了從2.5G到64Gbps的速率范圍,高速FPGA的串行高速接口速率則從8Gbps猛增到28Gbps,DSP和ADC/DAC從3Gbps過渡到32Gbps。

高信號完整性對于實現故障安全操作至關重要。要滿足高速傳輸的性能預期,特別是高速接收端的性能, 接收端容限測試至關重要。

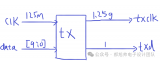

RX接收端是整個高速鏈路的最終環節,接收端測試由于在芯片內部,在絕大多數場景無法直接觀測信號完整性問題。最主流的方式是通過創建壓力眼來模擬真實世界最苛刻的運行環境。誤碼儀是構建和校準壓力眼的核心測試儀器。對于一個高速傳輸鏈路,接收端需要在最嚴苛的環境中保證可靠的接收傳輸的數據。發送端和鏈路上的各種信號完整性問題都會惡化信號,減小接收機的余量。接收端測試需要誤碼分析儀注入多種不同類型的抖動和噪聲等壓力信號,模擬嚴苛復雜的真實環境,來完成RX接收端的抖動容限和噪聲容限測試。

SL3000B系列高性能誤碼儀能夠針對各種高速協議標準和非標的速率進行接收端容限測試。

SL3000B系列高性能誤碼儀

SL3000B具有強大的模塊化設計,單機設備支持6個可擴展功能槽位,靈活配置不同模塊,每通道支持1GBaud到最高32GBaud,速率連續可調,沒有斷點,支持NRZ/PAM4信號切換,支持各種常用的碼型(prbs7/9/11/13/15/23/3l,prbs7Q~31Q,SSPRQ用戶自定義碼型)及多種隨機碼型和高級自定義碼型,支持JTOL/ITOL測試,支持RJ、PJ、SJ、BUJ抖動注入功能,支持DMI、CMI和寬帶噪聲注入功能,支持SSC擴頻時鐘注入功能,具有眼圖特征信息分析功能,通道間ps級別分辨率相位精確可調功能。

-

測試

+關注

關注

8文章

5632瀏覽量

128327 -

高速串行

+關注

關注

2文章

22瀏覽量

11408 -

串行信號

+關注

關注

0文章

28瀏覽量

8619

發布評論請先 登錄

是德S系列示波器如何應對高速串行測試

皮秒級暗戰:深度解析高速信號完整性的“隱形殺手”!

DAC8801信號輸出波形會隨著串行數據線上的信號變化而變化,為什么?

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

【9月3日|線上講堂】從衛星通信技術到測試方案全景解析

深度解析高速串行信號的誤碼測試|線上講堂

深度解析高速串行信號的誤碼測試|線上講堂

評論