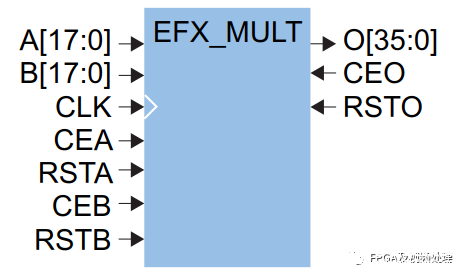

在使用Trion乘法器可能會遇到以下問題:

(1)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CEA' is not permanently disabled in the Register Bypass mode.

說明:如果輸入寄存器A_REG沒有使能,CEA接口要設置為0

(2)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'RSTA' is not permanently disabled in the Register Bypass mode.

說明:如果輸入寄存器A_REG沒有使能,RSTA接口要設置為0

(3)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CLK' is not permanently disabled in the Register Bypass mode.

說明:如果輸入和輸出寄存都沒有使用的話,時鐘也要設置為0。

所以這里提供下面的寫法供參考。

EFX_MULT.WIDTH(18),.A_REG(AREG),.B_REG(BREG),.O_REG(OREG),.CLK_POLARITY(1'b1), // 0 falling edge, 1 rising edge.CEA_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTA_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTA_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTA_VALUE(1'b0), // 0 reset, 1 set.CEB_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTB_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTB_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTB_VALUE(1'b0), // 0 reset, 1 set.CEO_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTO_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTO_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTO_VALUE(1'b0) // 0 reset, 1 set) mult (.CLK((AREG || BREG || OREG) ? clk : 0),.CEA(AREG),.RSTA(AREG ? rst : 1),.CEB(BREG),.RSTB(BREG ? rst : 1),.CEO(OREG),.RSTO(OREG ? rst : 1),.A(A_in),.B(B_in),.O(O_out));

-

dsp

+關注

關注

556文章

8154瀏覽量

356554 -

原語使用

+關注

關注

0文章

2瀏覽量

1259

發布評論請先 登錄

如何減少dsp啟動時間?

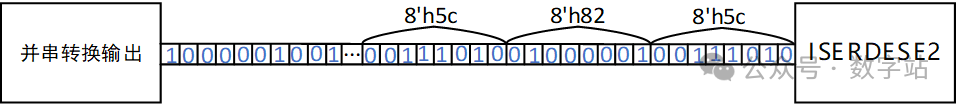

ISERDESE2原語端口及參數介紹

選擇DSP處理器ADSP-2101與DSP16A的注意事項

TMS320C54x DSP CPU和外設參考集,第1卷

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

使用AMD Versal AI引擎加速高性能DSP應用

如何選擇合適的DSP平臺

DSP平臺與RTB的關系

DSP功放HOSt和acc區別

DSP控制器的主要優勢是什么?

雙核dsp和單核dsp的區別

雙DSP音效處理芯片有什么作用

DSP是什么意思

Efinity編譯生成文件使用指導

Trion DSP 原語使用問題 - 1

Trion DSP 原語使用問題 - 1

評論