本文來(lái)源:半導(dǎo)體行業(yè)觀察

摘要:將多個(gè)異構(gòu)芯粒集成在一起進(jìn)行封裝是一種具有廣闊前景且成本效益高的策略,它能夠構(gòu)建出既靈活又可擴(kuò)展的系統(tǒng),并且能有效加速多樣化的工作負(fù)載。在此基礎(chǔ)上,我們提出了Arvon,它使用嵌入式多芯片互連橋(EMIBs)將一個(gè)14nm FPGA芯粒和兩個(gè)緊密排列的高性能22nm DSP芯粒集成在了一起。芯粒間通過(guò)一個(gè)1.536-Tb/s的高級(jí)接口總線(AIB)1.0接口和一個(gè)7.68-Tb/s的AIB 2.0接口進(jìn)行互連。Arvon是可編程的,支持從神經(jīng)網(wǎng)絡(luò)(NN)到通信信號(hào)處理的各種工作負(fù)載。每個(gè)DSP芯粒在半精度浮點(diǎn)運(yùn)算中提供了4.14 TFLOPS的峰值性能,同時(shí)保持了1.8 TFLOPS/W的能效。我們還開(kāi)發(fā)了一個(gè)能夠?yàn)镕PGA和DSP分配工作負(fù)載的編譯程序,以此來(lái)優(yōu)化系統(tǒng)的性能和資源利用率。我們使用36-μm-pitch微凸塊實(shí)現(xiàn)的AIB 2.0接口達(dá)到了4 Gb/s/pin的數(shù)據(jù)傳輸速率,包括適配器在內(nèi)的能效為0.10–0.46 pJ/b。其Shoreline帶寬密度達(dá)到 1.024 Tb/s/mm,areal帶寬密度達(dá)到1.705 Tb/s/mm2。

I. 介紹

隨著機(jī)器學(xué)習(xí)、機(jī)器人技術(shù)和5G/6G通信等領(lǐng)域的快速發(fā)展,用于這些領(lǐng)域的DSP工作負(fù)載正變得越來(lái)越動(dòng)態(tài)和多樣化。一個(gè)靈活且計(jì)算效率高的硬件系統(tǒng)能夠很好地滿足這些需求。這樣的系統(tǒng)可以集成多個(gè)組件,包括CPU、FPGA以及DSP加速器等,其中CPU或FPGA提供了系統(tǒng)所需的靈活性,DSP加速器提供了高效的內(nèi)核加速。

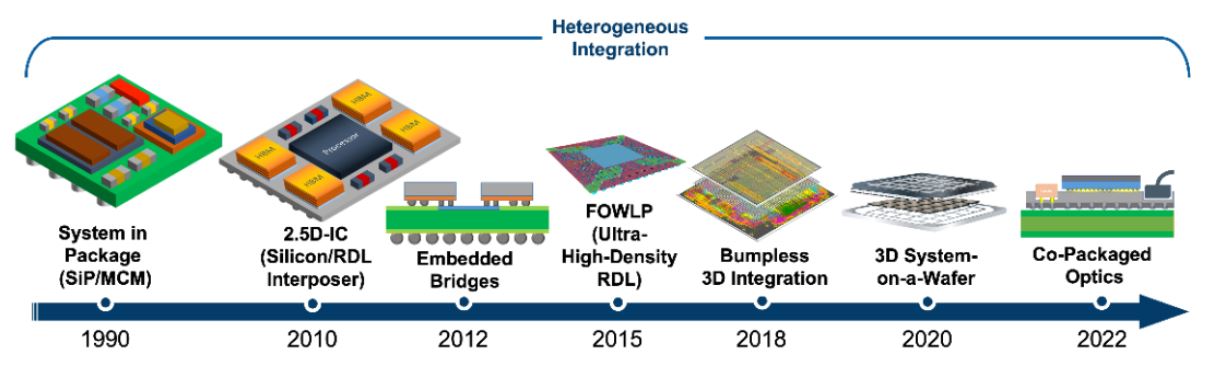

實(shí)現(xiàn)這類系統(tǒng)的一種方法是設(shè)計(jì)并制造一個(gè)單片系統(tǒng)級(jí)芯片(SoC)。然而,構(gòu)建一個(gè)大型SoC有著高昂的時(shí)間成本和經(jīng)濟(jì)成本。對(duì)此,作為一種成本效益高且可行的替代方案,采用2.5D或3D芯粒集成的異構(gòu)系統(tǒng)級(jí)封裝(SiP)為構(gòu)建大規(guī)模系統(tǒng)提供了一條有希望的途徑,以實(shí)現(xiàn)與單片集成相媲美的性能,同時(shí)避免了與單片集成相關(guān)的高成本、高風(fēng)險(xiǎn)和高工作量。SiP由稱為芯粒(chiplet)的互連組件組成。每個(gè)芯粒都包含一個(gè)功能模塊,可以在最適合的技術(shù)節(jié)點(diǎn)上制造,以獲得最佳性能和效率。由于每個(gè)芯粒在尺寸上更小、功能上更專一,因此其設(shè)計(jì)復(fù)雜性會(huì)降低,而產(chǎn)量則會(huì)提高。通過(guò)選擇已知良片(KGD)來(lái)組裝SiP,可以提高系統(tǒng)產(chǎn)量。在未來(lái)設(shè)想的芯片生態(tài)中,我們可以從不同的供應(yīng)商那里采購(gòu)經(jīng)過(guò)驗(yàn)證的芯片,并在構(gòu)建多樣化的系統(tǒng)時(shí)重復(fù)利用它們,這樣就能有效地克服在快速開(kāi)發(fā)新系統(tǒng)過(guò)程中遇到的挑戰(zhàn)和障礙。

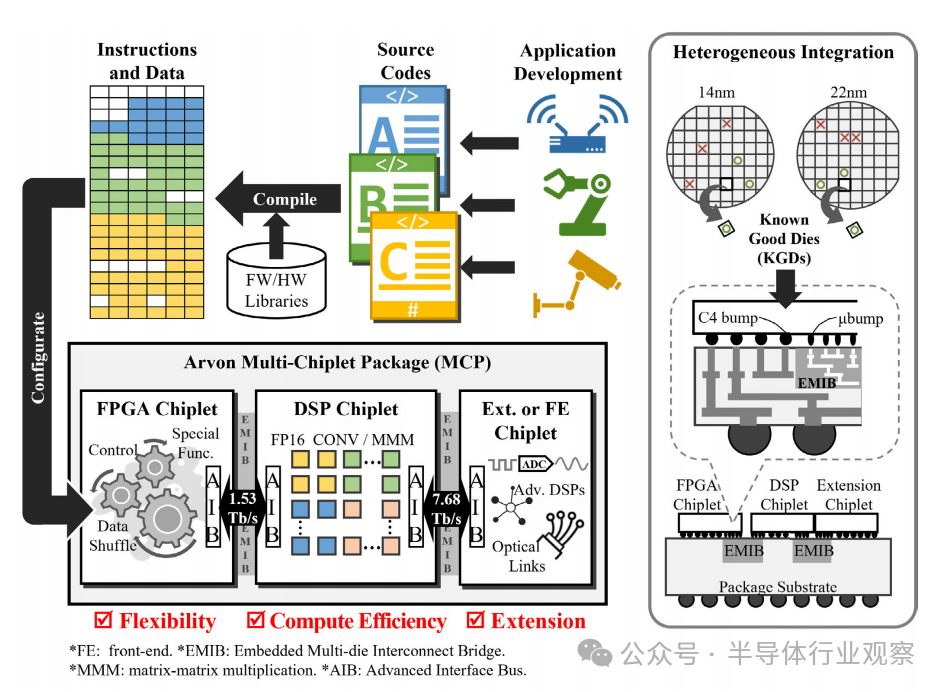

圖1展示了一種多功能加速器的SiP解決方案,它整合了一個(gè)FPGA芯粒、一個(gè)DSP加速器芯粒,以及可能包括的擴(kuò)展芯粒,比如模數(shù)轉(zhuǎn)換器(ADC)或光學(xué)收發(fā)器。這種異構(gòu)SiP設(shè)計(jì)能夠靈活地將各種動(dòng)態(tài)DSP工作負(fù)載——從機(jī)器學(xué)習(xí)到通信信號(hào)處理,映射到其上。FPGA芯粒提供必要的自適應(yīng)性,DSP芯粒貢獻(xiàn)高效的計(jì)算能力,而擴(kuò)展芯粒則提供了與前端(FE)組件如傳感器、無(wú)線或光接口的連接。在SiP內(nèi)部,芯粒之間的芯片間接口對(duì)于數(shù)據(jù)傳輸至關(guān)重要,它必須提供足夠高的帶寬,以確保與單片SoC相匹敵的性能,同時(shí)維持較低的每比特能耗,確保整個(gè)解決方案保持競(jìng)爭(zhēng)力。

圖1 Arvon SiP通過(guò)異構(gòu)集成FPGA、DSP和FE芯粒,實(shí)現(xiàn)靈活的工作負(fù)載映射

近期的研究展示了在具有高帶寬和高效的die-to-die接口的SiP中集成芯粒的成果。在文獻(xiàn)中,兩個(gè)雙Arm核心芯粒集成在chip-on-wafer-on-substrate(CoWoS)上,具有8-Gb/s/pin的低電壓封裝內(nèi)互連(LIPINCON)接口。在文獻(xiàn)中,36個(gè)深度神經(jīng)網(wǎng)絡(luò)(DNN)加速器芯粒使用25-Gb/s/pin的地參考信號(hào)(GRS)接口集成在有機(jī)基板上。在文獻(xiàn)和中,四個(gè)運(yùn)行時(shí)可重配置的通用數(shù)字信號(hào)處理器(UDSP)集成在具有 1.1 Gb/s/pin SNR-10 接口的硅片互連結(jié)構(gòu) (Si-IF) 中介層上。IntAct則在活性硅中介層上集成了六個(gè)16核芯粒,使用了1.2-Gb/s/pin的3-D-Plug接口。這些成果代表了同構(gòu)集成的典型應(yīng)用,通過(guò)將模塊化芯粒的多個(gè)實(shí)例拼接在一起,有效地?cái)U(kuò)展了計(jì)算系統(tǒng)的規(guī)模。

在Arvon中,我們展示了不同類型芯粒的異構(gòu)集成,以構(gòu)建一個(gè)用于DSP工作負(fù)載的多功能加速器。Arvon由一個(gè)14nm FPGA芯粒和兩個(gè)通過(guò)嵌入式多芯片互連橋(EMIB)技術(shù)集成的22nm DSP芯粒組成。我們?cè)突说谝淮偷诙_(kāi)放式高級(jí)接口總線(AIB)芯片間接口,分別稱為AIB 1.0和AIB 2.0,用于連接這些芯粒。結(jié)果在一個(gè)SiP中得到展示,該SiP能夠有效地加速各種機(jī)器學(xué)習(xí)和通信DSP工作負(fù)載,同時(shí)保持較高的硬件利用率。這項(xiàng)工作還展示了AIB 2.0接口,該接口在能效為 0.1 pJ/b的情況下實(shí)現(xiàn)了1 Tb/s/mm 的海岸線帶寬密度和 1.7 Tb/s/mm2的面積帶寬密度。

本文的其余部分安排如下:第二部分概述了Arvon SiP。第三部分詳細(xì)闡述了AIB接口的設(shè)計(jì),包括物理層(PHY)I/O、時(shí)鐘分布和總線適配。第四部分深入探討了DSP芯粒及其矢量引擎設(shè)計(jì)的細(xì)節(jié)。第五部分討論了各種工作負(fù)載的映射。第六部分介紹了硅片測(cè)量和系統(tǒng)評(píng)估。最后,第七部分對(duì)本文進(jìn)行了總結(jié)。

II. ARVON 系統(tǒng)概述

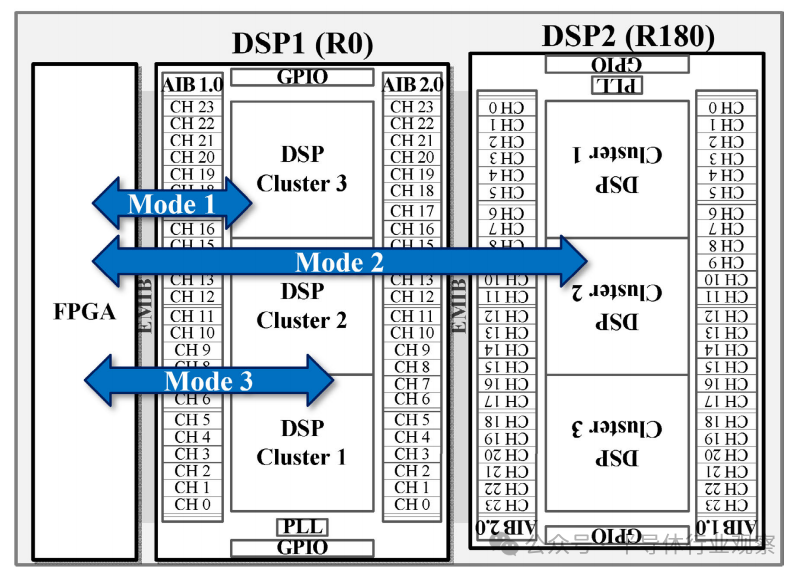

Arvon系統(tǒng)概覽如圖2所示。該系統(tǒng)包括一個(gè)FPGA芯粒和兩個(gè)DSP芯粒實(shí)例,分別命名為DSP1和DSP2。DSP2是DSP1的物理旋轉(zhuǎn)版本。FPGA使用EMIB技術(shù)通過(guò)AIB 1.0接口連接到DSP1,而DSP1使用EMIB技術(shù)通過(guò)AIB 2.0接口連接到DSP2。Arvon提供了三種操作模式,如圖2所示。在模式1和模式2中,F(xiàn)PGA分別連接到DSP1和DSP2,并將通用計(jì)算核心卸載到DSP上面。這些通用核心包括在神經(jīng)網(wǎng)絡(luò)(NN)和通信工作負(fù)載中至關(guān)重要的矩陣乘法(MMM)和二維卷積(conv)。在模式3中,DSP1和DSP2被組合起來(lái)以增強(qiáng)計(jì)算能力。DSP2也可以被FE芯粒(例如光學(xué)tile或 ADC tile)取代,以實(shí)現(xiàn)完整的通信或傳感系統(tǒng)。

圖2 Arvon SiP支持的數(shù)據(jù)流模式: 在模式1和模式2中,F(xiàn)PGA連接到其中一個(gè)DSP; 在模式3中,F(xiàn)PGA同時(shí)連接到兩個(gè)DSP

A

DSP芯粒

DSP 芯粒可為計(jì)算密集型工作負(fù)載提供卸載和加速功能。DSP芯粒的設(shè)計(jì)如圖2所示。芯粒的兩側(cè)都放置了芯片間接口。在西側(cè),有24個(gè)AIB 1.0接口通道,為與FPGA的通信提供1.536 Tb/s的帶寬。在東側(cè),有24個(gè)AIB 2.0接口通道,為與另一個(gè)DSP的通信提供7.68 Tb/s的帶寬。芯粒包含三個(gè)DSP集群,每個(gè)集群提供1024個(gè)16位半精度浮點(diǎn)處理元素(PE)。每個(gè)集群最多使用8個(gè)AIB 1.0接口通道和8個(gè)AIB 2.0接口通道進(jìn)行輸入輸出。使用低抖動(dòng)環(huán)形鎖相環(huán)(PLL)為DSP集群以及AIB 1.0和AIB 2.0接口生成時(shí)鐘。沿著芯粒頂部和底部有兩排通用輸入/輸出(GPIO)端口,便于進(jìn)行全局配置和調(diào)試。

B

FPGA主機(jī)芯粒

FPGA在實(shí)現(xiàn)Arvon的靈活性方面發(fā)揮著關(guān)鍵作用。FPGA的可編程邏輯被用來(lái)支持各種任務(wù),例如為DSP執(zhí)行轉(zhuǎn)置和洗牌等數(shù)據(jù)處理操作。此外,F(xiàn)PGA也可以用來(lái)提供DSP上沒(méi)有的特殊功能,從而能夠滿足完整的處理需求。

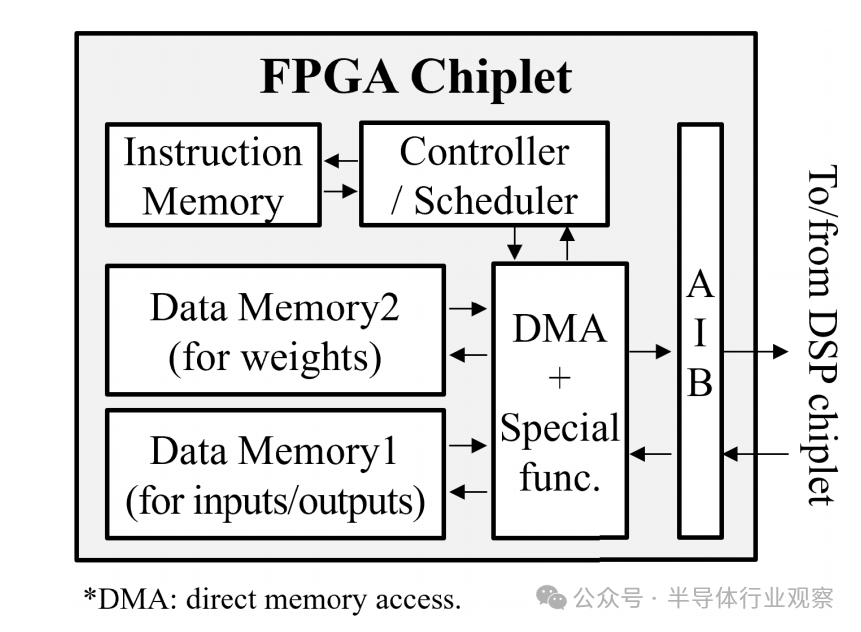

在Arvon中,F(xiàn)PGA充當(dāng)主機(jī)的角色,采用如圖3所示的基于指令的處理器形式出現(xiàn)。一個(gè)簡(jiǎn)單的主機(jī)處理器配備了指令存儲(chǔ)器、用于存儲(chǔ)輸入輸出數(shù)據(jù)數(shù)據(jù)和權(quán)重?cái)?shù)據(jù)的數(shù)據(jù)存儲(chǔ)器,以及一個(gè)用于管理和協(xié)調(diào)與DSP芯粒進(jìn)行數(shù)據(jù)傳輸?shù)闹苯觾?nèi)存訪問(wèn)(DMA)單元。指令用于在運(yùn)行時(shí)配置和重新配置DSP,引導(dǎo)數(shù)據(jù)存儲(chǔ)器和DSP之間的數(shù)據(jù)流,以及執(zhí)行DSP的前處理和后處理。

當(dāng)FPGA內(nèi)的主處理器觸發(fā)并從指令存儲(chǔ)器中讀取首條指令時(shí),工作負(fù)載的執(zhí)行便正式啟動(dòng)。這些指令詳細(xì)說(shuō)明了所需的所有信息,包括數(shù)據(jù)內(nèi)容、寄存器訪問(wèn)地址、存儲(chǔ)器地址、總線地址、DMA進(jìn)行讀寫操作的數(shù)據(jù)長(zhǎng)度,以及執(zhí)行的先后順序。根據(jù)指令,主機(jī)處理器生成AXI總線事務(wù)以訪問(wèn)發(fā)送到DSP的DSP配置寄存器。同時(shí),它也會(huì)發(fā)布DMA命令,用以從數(shù)據(jù)存儲(chǔ)器讀取或?qū)懭霐?shù)據(jù),以及向DSP進(jìn)行數(shù)據(jù)的讀取和寫入。鑒于DSP中矢量引擎的處理時(shí)間較快,包括主機(jī)處理器在內(nèi)的FPGA實(shí)現(xiàn)得到了高度利用,以最小化延遲并防止任何潛在的瓶頸。

圖3 FPGA主機(jī)實(shí)現(xiàn)示例

III. AIB 芯片間接口

在 DSP 芯粒內(nèi),其西側(cè)集成了24個(gè) AIB 1.0 接口通道,東側(cè)集成了24個(gè) AIB 2.0 接口通道。AIB 通道由兩層組成:適配器層和物理層 I/O 層。適配器層負(fù)責(zé)協(xié)調(diào) DSP 核與物理層 I/O 之間的數(shù)據(jù)傳輸。它負(fù)責(zé)這兩個(gè)域之間的數(shù)據(jù)成幀和同步。狀態(tài)機(jī)用于啟動(dòng) AIB 鏈路并啟用自動(dòng)時(shí)鐘相位調(diào)整。這種調(diào)整有助于確定數(shù)據(jù)的眼寬和中心。在 AIB 2.0 中,適配器還支持可選的數(shù)據(jù)總線反轉(zhuǎn) (DBI),從而減少了總線切換活動(dòng)并提高了能效。

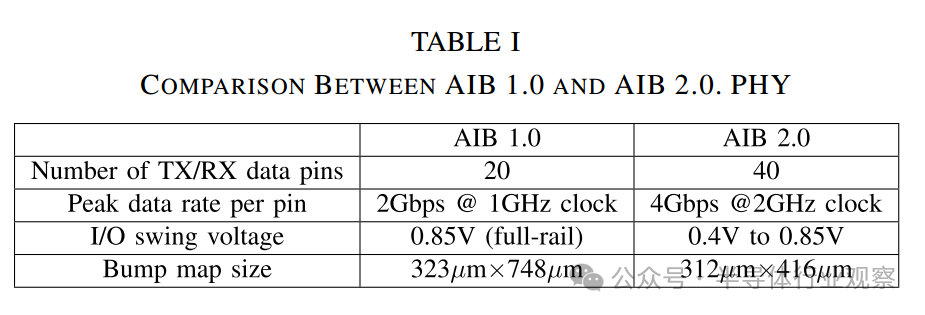

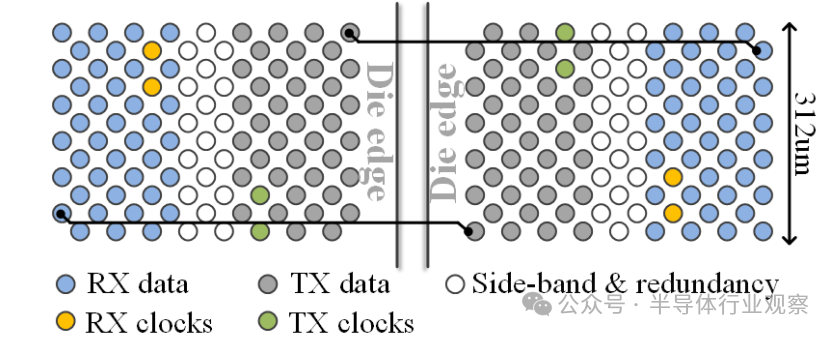

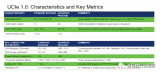

AIB 接口的物理層實(shí)現(xiàn)了源同步、短距離、低延遲和并行單端 I/O。在雙數(shù)據(jù)速率(DDR)模式下,AIB 1.0的每個(gè)I/O端口通過(guò)全軌信號(hào)傳輸,提供從1 Mb/s到2 Gb/s的帶寬范圍。而AIB 2.0則進(jìn)一步在DDR模式下,通過(guò)0.4 V至全軌信號(hào)的擺幅變化,實(shí)現(xiàn)了從1 Mb/s至4 Gb/s的帶寬,從而顯著提升了數(shù)據(jù)傳輸速率。單個(gè) AIB 1.0 通道由 96 個(gè)引腳組成,其中包括2個(gè) TX 時(shí)鐘引腳、2個(gè) RX 時(shí)鐘引腳、20 個(gè) TX 數(shù)據(jù)引腳、20 個(gè) RX 數(shù)據(jù)引腳以及用于邊帶控制的和冗余的附加引腳。相比之下,單個(gè) AIB 2.0 通道由 102 個(gè)引腳組成,其中包括兩個(gè) TX 時(shí)鐘引腳、兩個(gè) RX 時(shí)鐘引腳、40 個(gè) TX 數(shù)據(jù)引腳、40 個(gè) RX 數(shù)據(jù)引腳以及用于邊帶控制的和冗余的附加引腳。AIB 2.0 在 AIB 1.0 的基礎(chǔ)上進(jìn)行了改進(jìn),它將每個(gè)引腳的數(shù)據(jù)傳輸速率和每個(gè)通道的數(shù)據(jù)引腳數(shù)量增加了一倍,從而將數(shù)據(jù)傳輸帶寬提高了四倍。此外,AIB 2.0 還通過(guò)使用低擺動(dòng)信號(hào)提高了能效。AIB 1.0 和 AIB 2.0 的對(duì)比總結(jié)見(jiàn)表 I。值得注意的是,AIB 1.0 與 AIB 2.0 有著相似的設(shè)計(jì)結(jié)構(gòu)。

表 I

A

AIB 2.0 適配器

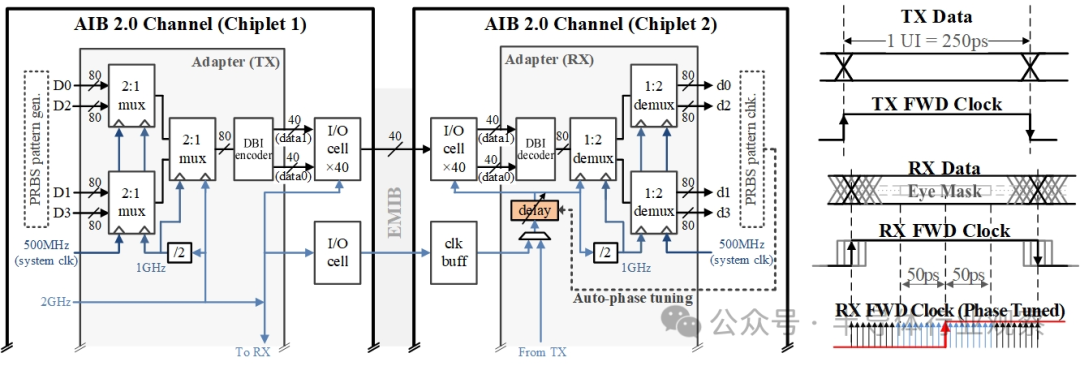

AIB 適配器管理 DSP 核與 PHY I/O 層之間的數(shù)據(jù)傳輸。數(shù)據(jù)路徑包括 TX 端的串行器和 RX 端的并行器。圖 4 展示了一個(gè)數(shù)據(jù)傳輸實(shí)例。在芯粒 1 中,一個(gè) AIB 2.0 TX 通道每次從 DSP 核收集四條 80 位寬的數(shù)據(jù)流,DSP 核的時(shí)鐘頻率為 500 MHz。使用兩級(jí) 2:1 多路復(fù)用器實(shí)現(xiàn)的串行器將并行數(shù)據(jù)流轉(zhuǎn)換為單條 80 位寬的數(shù)據(jù)流進(jìn)行傳輸。在可選用的 DBI 之后,80位數(shù)據(jù)被分為高低兩個(gè)40位的段,這兩個(gè)數(shù)據(jù)段分別發(fā)送至40個(gè)TX I/O單元的data0和data1引腳。在 DDR 模式下這些TX I/O單元以2 GHz的頻率運(yùn)行,每個(gè)單元每次傳輸2位數(shù)據(jù),從而實(shí)現(xiàn)了4 Gb/s的有效數(shù)據(jù)傳輸速率。差分的2 GHz TX 時(shí)鐘與數(shù)據(jù)一起被轉(zhuǎn)發(fā)到芯粒2。在芯粒2 中,一個(gè) AIB 2.0 RX 通道負(fù)責(zé)接收來(lái)自40個(gè) RX I/O 單元的80位寬數(shù)據(jù)。在 DDR 模式下,數(shù)據(jù)以2 GHz的頻率進(jìn)行采樣。隨后,接收到的數(shù)據(jù)流通過(guò)并行器處理,其采用兩級(jí)1:2的解復(fù)用器實(shí)現(xiàn),將數(shù)據(jù)恢復(fù)成四路80位寬的數(shù)據(jù)流。接收到的TX端的時(shí)鐘信號(hào)通過(guò)可調(diào)節(jié)的延時(shí)線進(jìn)行微調(diào),以適配RX端I/O單元的采樣時(shí)鐘需求。

1)自動(dòng)時(shí)鐘相位調(diào)整:在鏈路的初始化階段,RX 時(shí)鐘相位會(huì)進(jìn)行調(diào)整,以便在最佳點(diǎn)對(duì) RX 數(shù)據(jù)進(jìn)行采樣。適配器采用自動(dòng) RX 時(shí)鐘相位調(diào)整機(jī)制。TX負(fù)責(zé)發(fā)送一個(gè)已知的偽隨機(jī)二進(jìn)制序列(PRBS),而后RX則利用可配置的延遲線掃描從TX接收到的時(shí)鐘信號(hào)的延遲,從而監(jiān)測(cè)潛在的錯(cuò)誤。通過(guò)分析接收到的PRBS序列中的錯(cuò)誤模式,RX端能夠估算出眼圖的邊界。這樣做的目的是將延遲以及采樣點(diǎn)設(shè)置在估計(jì)的眼圖中點(diǎn)。

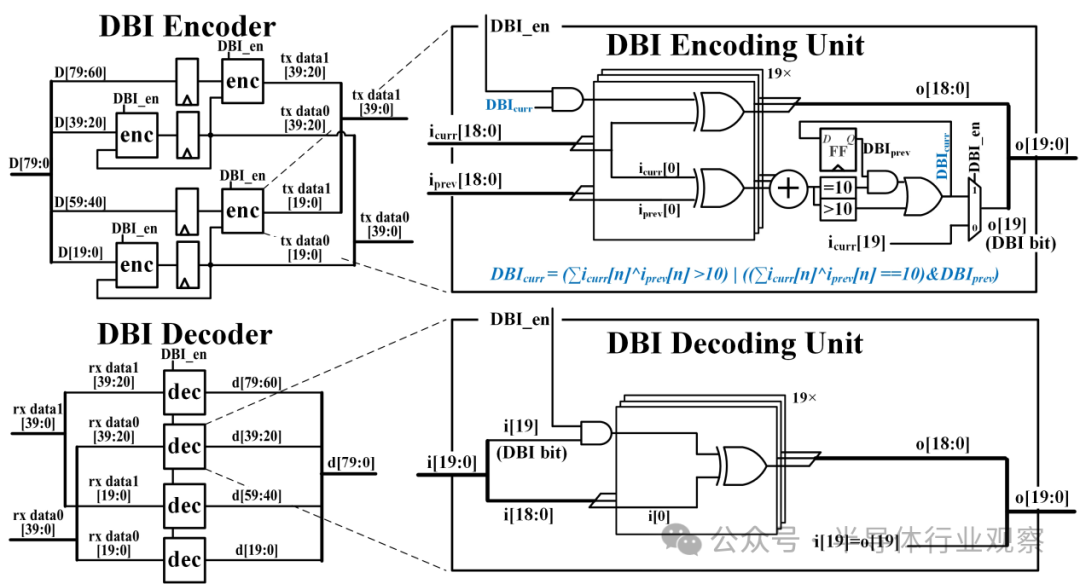

2)數(shù)據(jù)總線反轉(zhuǎn)(DBI):AIB 2.0支持?jǐn)?shù)據(jù)總線反轉(zhuǎn),這有效地減少了單端及源同步接口中的轉(zhuǎn)換和同步開(kāi)關(guān)輸出(SSO)噪聲。圖5展示了一個(gè)1:19比例的DBI編碼器和解碼器。在TX端,80位數(shù)據(jù)由四個(gè)并行DBI編碼單元進(jìn)行編碼。每個(gè)單元獲取19位數(shù)據(jù)線的值(在圖5中由icurr[18:0]表示),并計(jì)算先前編碼的數(shù)據(jù)(iprev[18:0])中已發(fā)生轉(zhuǎn)換的位數(shù)。如果計(jì)數(shù)超過(guò)10(20比特的一半),則DBI編碼單元會(huì)反轉(zhuǎn)這些位,并給DBI位分配一個(gè)高(HIGH)值。如果計(jì)數(shù)等于10,并且前一個(gè)DBI位已經(jīng)是高(HIGH),則DBI位保持高(HIGH)。如果上述條件都不滿足,數(shù)據(jù)保持不變,DBI位被設(shè)置為低(LOW)。然后,DBI位與編碼后的19位數(shù)據(jù)結(jié)合,打包成20位的TX數(shù)據(jù),并發(fā)送到20個(gè)I/O單元。在RX端,采用四個(gè)并行DBI解碼單元。如果DBI位(接收到的20位數(shù)據(jù)塊的最高位)為高(HIGH),則每個(gè)單元將反轉(zhuǎn)接收到的19位數(shù)據(jù)位,如果DBI位為低(LOW),則數(shù)據(jù)保持不變。

圖4 AIB 2.0 通道頂層圖和自動(dòng)時(shí)鐘相位調(diào)整

圖5 1:19比例DBI編碼器(上)和解碼器(下)

B

AIB 2.0 I/O

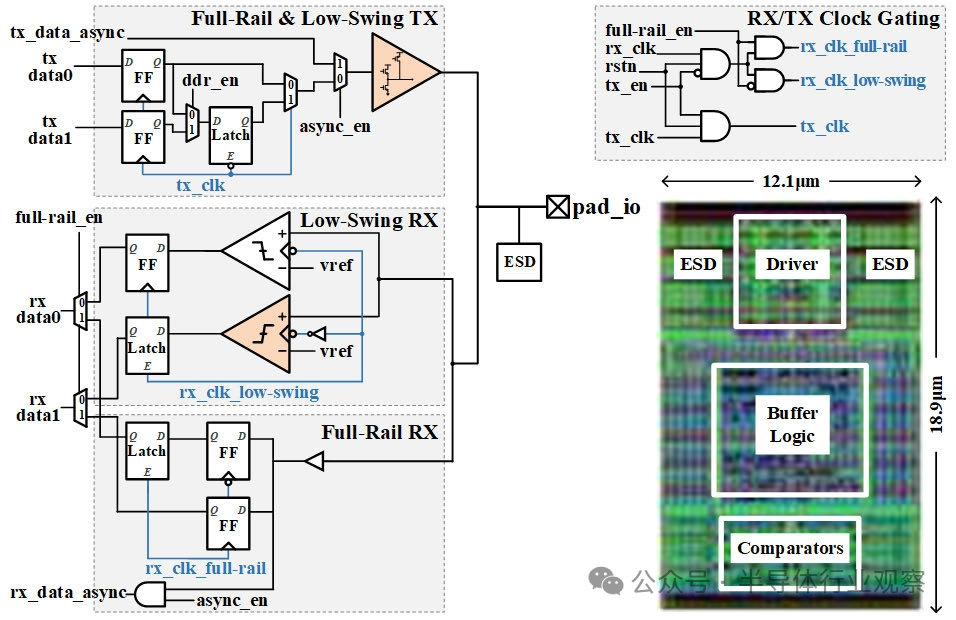

圖6展示了一種緊湊型統(tǒng)一 AIB 2.0 I/O 單元設(shè)計(jì)的原理圖和布局。為了實(shí)現(xiàn)36 μm微凸塊間距的目標(biāo),該I/O 單元的布局經(jīng)過(guò)了精心的優(yōu)化,每個(gè)單元都在相應(yīng)的微凸塊下連接,以確保布局符合規(guī)定的凸塊間距。統(tǒng)一I/O單元支持多種模式。首先,傳輸方向可以靈活設(shè)置為TX或RX模式,這不僅有助于進(jìn)行冗余修復(fù),也便于芯粒間的靈活連接。在TX模式下,為了降低功耗,RX組件的時(shí)鐘被門控;反之,在RX模式下,TX組件的時(shí)鐘被門控。其次,對(duì)于 AIB 1.0 和 AIB 2.0,I/O 信號(hào)擺幅可設(shè)置為全軌,而對(duì)于 AIB 2.0,擺幅還可以降低至 0.4 V。第三,傳輸模式可以設(shè)置為單數(shù)據(jù)速率(SDR)模式或雙數(shù)據(jù)速率(DDR)模式。在DDR模式下,數(shù)據(jù)0和數(shù)據(jù)1被串行化后進(jìn)行傳輸,其中數(shù)據(jù)1比數(shù)據(jù)0延遲半個(gè)時(shí)鐘周期。這意味著,在TX時(shí)鐘的正邊沿,數(shù)據(jù)0被發(fā)送至驅(qū)動(dòng)器,而在負(fù)邊沿,數(shù)據(jù)1被發(fā)送。在RX端,這一過(guò)程則相反,數(shù)據(jù)通過(guò)并行化恢復(fù)。SDR模式僅使用數(shù)據(jù)0,它在TX時(shí)鐘的正邊沿發(fā)送到驅(qū)動(dòng)器。最后,I/O 單元可設(shè)置為在時(shí)鐘和其他邊帶信號(hào)的異步模式下運(yùn)行。

圖6 一個(gè)統(tǒng)一AIB I/O單元的原理圖和布局

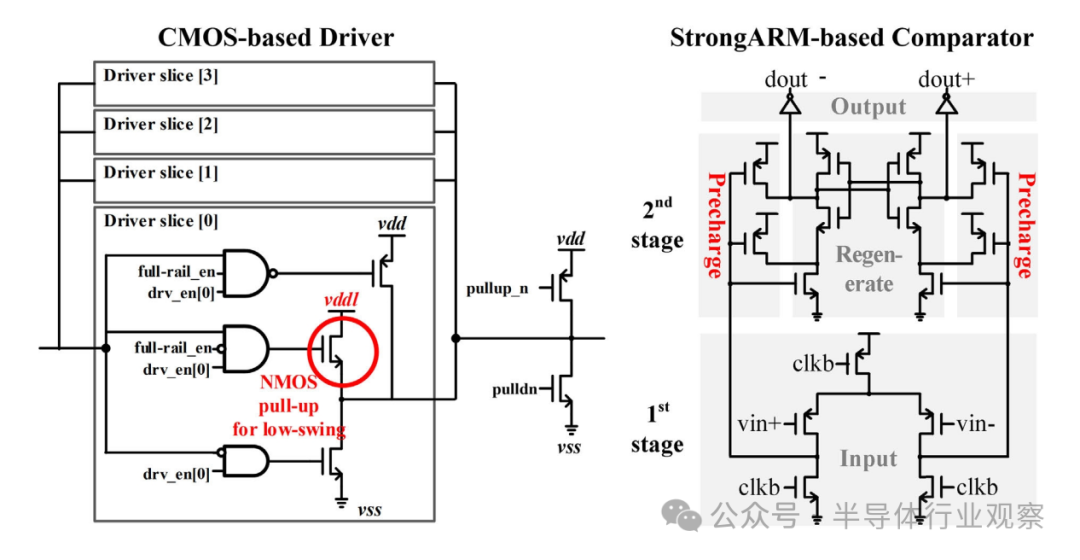

圖7 基于 CMOS 的 TX 驅(qū)動(dòng)器(左)和基于 strongARM 的 RX(右)示意圖

1)TX驅(qū)動(dòng)器:如圖7(左)所示,TX驅(qū)動(dòng)器的設(shè)計(jì)采用了分段技術(shù),由四部分組成。該設(shè)計(jì)允許將最多四段驅(qū)動(dòng)器連接起來(lái),以實(shí)現(xiàn)可調(diào)節(jié)的驅(qū)動(dòng)強(qiáng)度,這樣就可以根據(jù)通道變化靈活調(diào)整,同時(shí)平衡傳輸速度和功耗之間的關(guān)系。每個(gè)驅(qū)動(dòng)器段包括一個(gè)用于下拉的NMOS晶體管,以及一個(gè)可切換的PMOS或NMOS上拉驅(qū)動(dòng)器,后者可以根據(jù)需要提供全軌或低擺幅的驅(qū)動(dòng)力。在低擺幅模式下,NMOS上拉驅(qū)動(dòng)會(huì)被適度增強(qiáng),以確保與下拉驅(qū)動(dòng)力的平衡。此外,系統(tǒng)還允許通過(guò)設(shè)置弱上拉和下拉來(lái)配置初始開(kāi)機(jī)值。

2)RX緩沖器:RX緩沖器的設(shè)計(jì)區(qū)分了全軌輸入和低擺輸入。對(duì)于全軌輸入信號(hào),采用了標(biāo)準(zhǔn)單元緩沖器進(jìn)行處理;而對(duì)于低擺輸入信號(hào),則使用了再生比較器,如圖7(右)所示。該比較器是StrongARM鎖存器的優(yōu)化版本 ,無(wú)需校準(zhǔn)即可將平均偏移降低到 4.1 mV。此外,設(shè)計(jì)中還利用PMOS增強(qiáng)了對(duì)低波動(dòng)輸入的檢測(cè)。該設(shè)計(jì)采用了一個(gè)簡(jiǎn)單的基準(zhǔn)電壓發(fā)生器。比較器可在 2 GHz DDR 頻率下可靠地檢測(cè)低至 0.38 V 的輸入。

3)凸塊圖:圖8展示了一個(gè)AIB 2.0通道的12×17凸塊圖。該通道由40個(gè)TX數(shù)據(jù)引腳、40個(gè)RX數(shù)據(jù)引腳、2個(gè)TX轉(zhuǎn)發(fā)時(shí)鐘引腳、2個(gè)RX轉(zhuǎn)發(fā)時(shí)鐘引腳以及18個(gè)邊帶和冗余引腳組成。TX和RX凸塊的設(shè)計(jì)是對(duì)稱的,使得在EMIB上每對(duì)TX-RX的布線長(zhǎng)度對(duì)等。其總共擁有80個(gè)數(shù)據(jù)引腳,每個(gè)引腳的數(shù)據(jù)速率為4 Gb/s,一個(gè)AIB 2.0通道提供了總共320 Gb/s的帶寬。該設(shè)計(jì)的微凸塊間距為 36 μm,通道岸線寬度為 312.08 μm,帶寬密度達(dá)到 1024 Gb/s/mm。

圖8 一個(gè)AIB 2.0通道的凸塊圖

圖9 兩級(jí)時(shí)鐘分布

C

時(shí)鐘分布

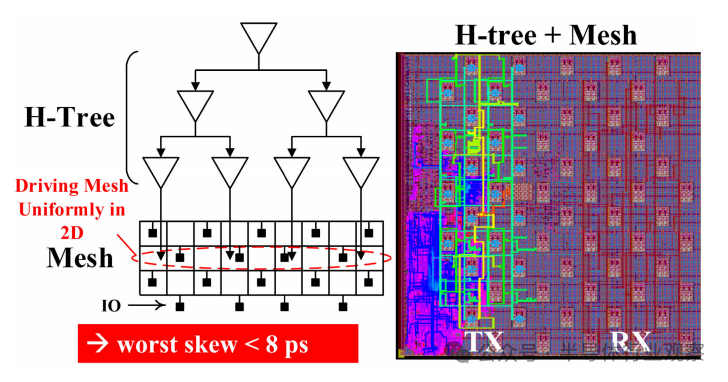

對(duì)于像AIB這樣的高速并行I/O接口來(lái)說(shuō),必須采用低偏斜時(shí)鐘分布,以確保給定通道中的所有數(shù)據(jù)引腳相位正確地對(duì)齊。如圖9所示,我們?cè)诿總€(gè)AIB通道中采用兩級(jí)時(shí)鐘分布。上層是一個(gè)均衡的H型樹(shù)狀結(jié)構(gòu),它覆蓋了整個(gè)通道;而下層則由一個(gè)局部時(shí)鐘網(wǎng)格構(gòu)成。這種雙層設(shè)計(jì)有效限制了H樹(shù)的深度,確保了各分支之間更好的平衡。此外,局部時(shí)鐘網(wǎng)格還能提供更穩(wěn)定的時(shí)鐘匯(clock sinks),且不會(huì)顯著增加功耗。因此,整個(gè)時(shí)鐘網(wǎng)絡(luò)能夠?qū)⒆顗牡臅r(shí)鐘偏斜控制在8ps以內(nèi)。H樹(shù)和網(wǎng)狀時(shí)鐘網(wǎng)絡(luò)都是使用IC Compiler II的多源時(shí)鐘樹(shù)綜合(MSCTS)流程創(chuàng)建和評(píng)估的。

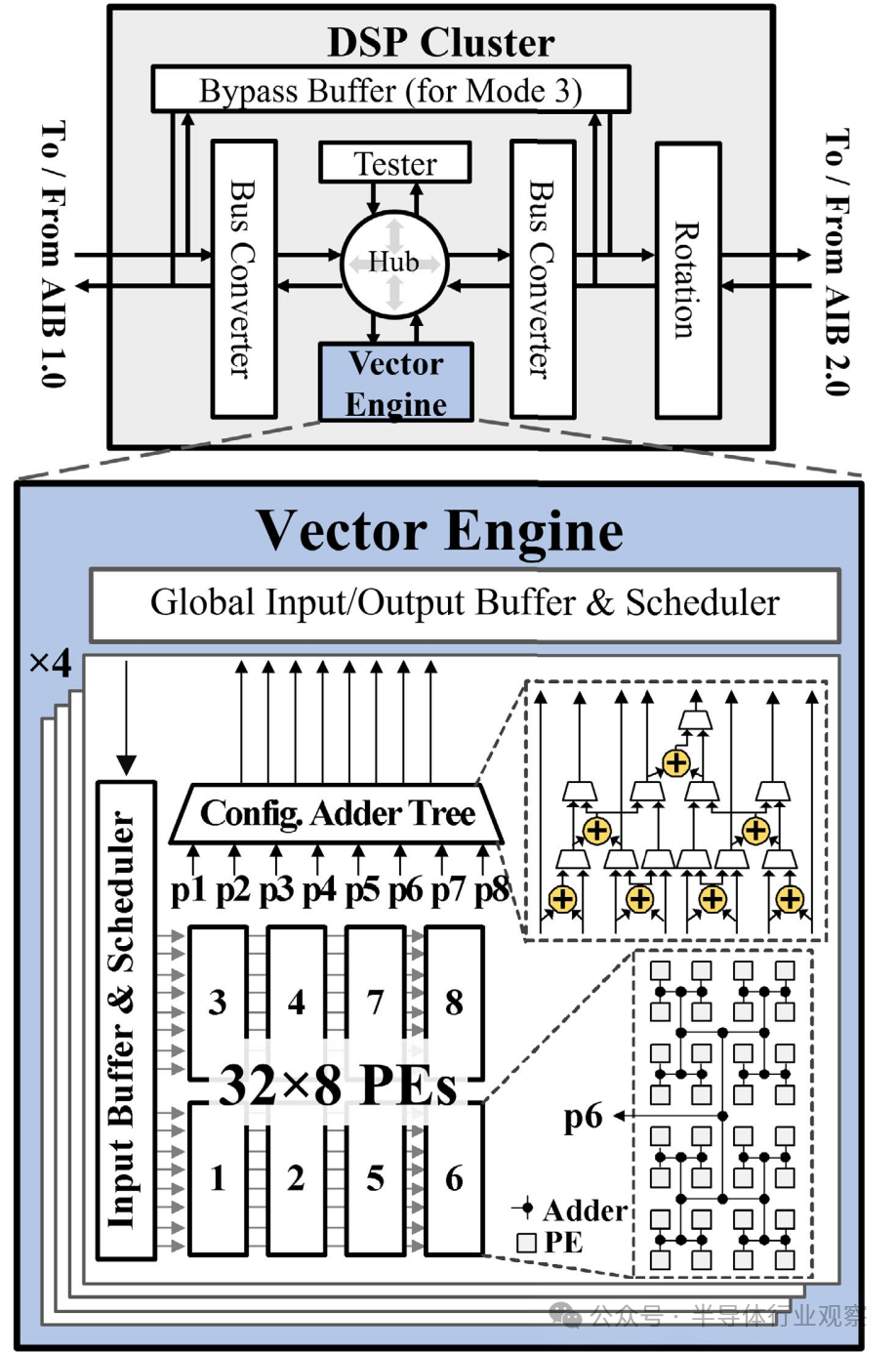

IV. DSP集群

如圖10所示,每個(gè)DSP集群包括一個(gè)靈活的矢量引擎、一個(gè)旁路緩沖器、一個(gè)用于數(shù)據(jù)成幀的旋轉(zhuǎn)塊、兩個(gè)用于在多個(gè) AIB 通道之間打包和解包數(shù)據(jù)的 兼容AXI 的總線轉(zhuǎn)換器,以及一個(gè)與AXI兼容的系統(tǒng)總線。此外,還包括一個(gè)總線樞紐,用于在矢量引擎和測(cè)試器、AIB 1.0接口或AIB 2.0接口之間建立連接。旁路緩沖器支持Arvon的模式2操作,可繞過(guò) DSP1 直接連接 FPGA 和 DSP2。通過(guò)這種連接,F(xiàn)PGA 的 AIB 1.0 事務(wù)可直接轉(zhuǎn)發(fā)到 DSP2 的 AIB 2.0 事務(wù)。旋轉(zhuǎn)塊反轉(zhuǎn)了AIB接口的通道索引順序。例如,將 DSP1 連接到 DSP2(DSP1 的旋轉(zhuǎn)版本)時(shí),DSP1 的通道 1-8 連接到 DSP2 的通道 24-17,需要 DSP2 的旋轉(zhuǎn)塊來(lái)顛倒連接順序。

圖10 DSP集群(上)和矢量引擎(下)

A矢量引擎

DSP集群的核心部件是矢量引擎,它由四個(gè) 2-D 對(duì)稱陣列實(shí)例組成。每個(gè)脈動(dòng)陣列包含256個(gè)PE,每個(gè) PE 以半精度浮點(diǎn)格式(FP16)執(zhí)行乘法運(yùn)算。這256個(gè)PE被分成八個(gè)單元,每個(gè)單元包含32個(gè)PE。每個(gè)32-PE單元的求和結(jié)果隨后輸入到一個(gè)可配置的加法器樹(shù)中。可配置的加法器樹(shù)可以通過(guò)選擇將八個(gè)單元中的哪些單元求和在一起,從而靈活地支持各種工作負(fù)載映射。這種設(shè)計(jì)提供了更短的部分求和累積路徑,并通過(guò)并發(fā)工作負(fù)載實(shí)現(xiàn)了更高的利用率,這與經(jīng)典的脈動(dòng)陣列有所區(qū)別。整個(gè)矢量引擎總共提供1024個(gè)PE,以支持矩陣-矩陣乘法(MMM)和卷積(conv)。最后,實(shí)現(xiàn)了一個(gè)全局I/O緩沖器和調(diào)度器,其使用多播或輪詢仲裁技術(shù)將輸入分配給PE陣列。

通過(guò)指令配置,矢量引擎便于輸入流的連續(xù)計(jì)算。矢量引擎還具有高度的映射靈活性。首先,四個(gè)脈動(dòng)陣列可以獨(dú)立映射。此外,每個(gè)陣列內(nèi)的256個(gè)PE可以32個(gè)PE為單位進(jìn)行配置,可適應(yīng) 1 到 8 個(gè)獨(dú)立的工作負(fù)載。

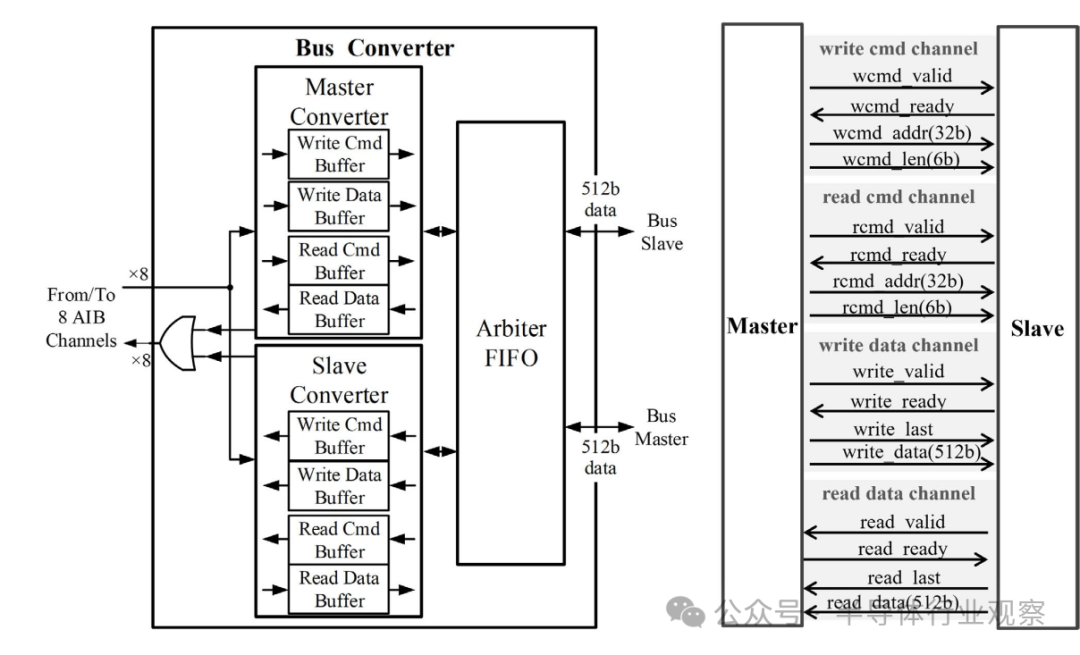

B系統(tǒng)總線和總線轉(zhuǎn)換器

AIB 連接由兼容 AXI 的點(diǎn)對(duì)點(diǎn)系統(tǒng)總線抽象出來(lái)。總線轉(zhuǎn)換器處理跨多個(gè)AIB通道的數(shù)據(jù)打包和解包。它還支持突發(fā)模式,以最大限度地利用帶寬進(jìn)行流式傳輸。系統(tǒng)總線的通道和信號(hào)在圖11中進(jìn)行了說(shuō)明。系統(tǒng)總線由四個(gè)通道組成:讀命令通道、寫命令通道、讀數(shù)據(jù)通道和寫數(shù)據(jù)通道。一個(gè)主設(shè)備能發(fā)出一個(gè)帶有32位地址和6位突發(fā)長(zhǎng)度的讀寫命令,以及512位寫數(shù)據(jù)和寫命令。在響應(yīng)讀命令時(shí),從設(shè)備將512位讀數(shù)據(jù)發(fā)送回主設(shè)備。系統(tǒng)總線和AIB通道之間的轉(zhuǎn)換由總線轉(zhuǎn)換器完成。我們?cè)谠O(shè)計(jì)總線轉(zhuǎn)換器時(shí)采用了基于報(bào)頭的流方法,以實(shí)現(xiàn)高帶寬和低延遲。一個(gè)矢量引擎最多可使用八個(gè) AIB 通道,以確保最佳利用率。每個(gè)AIB通道可以靈活地配置為主設(shè)備或從設(shè)備,允許根據(jù)需要調(diào)整TX/RX帶寬。

圖11 兼容AXI的系統(tǒng)總線:總線轉(zhuǎn)換器(左)以及總線接口通道和信號(hào)(右)

V. 工作負(fù)載映射

Arvon作為一個(gè)多功能的計(jì)算平臺(tái),它能夠支持不同規(guī)模的計(jì)算任務(wù),并且這些任務(wù)的復(fù)雜性可以在運(yùn)行過(guò)程中根據(jù)需要?jiǎng)討B(tài)調(diào)整。為確保高效的數(shù)據(jù)處理,必須建立一套系統(tǒng)方法,將工作負(fù)載映射到最佳硬件配置和數(shù)據(jù)布局上。

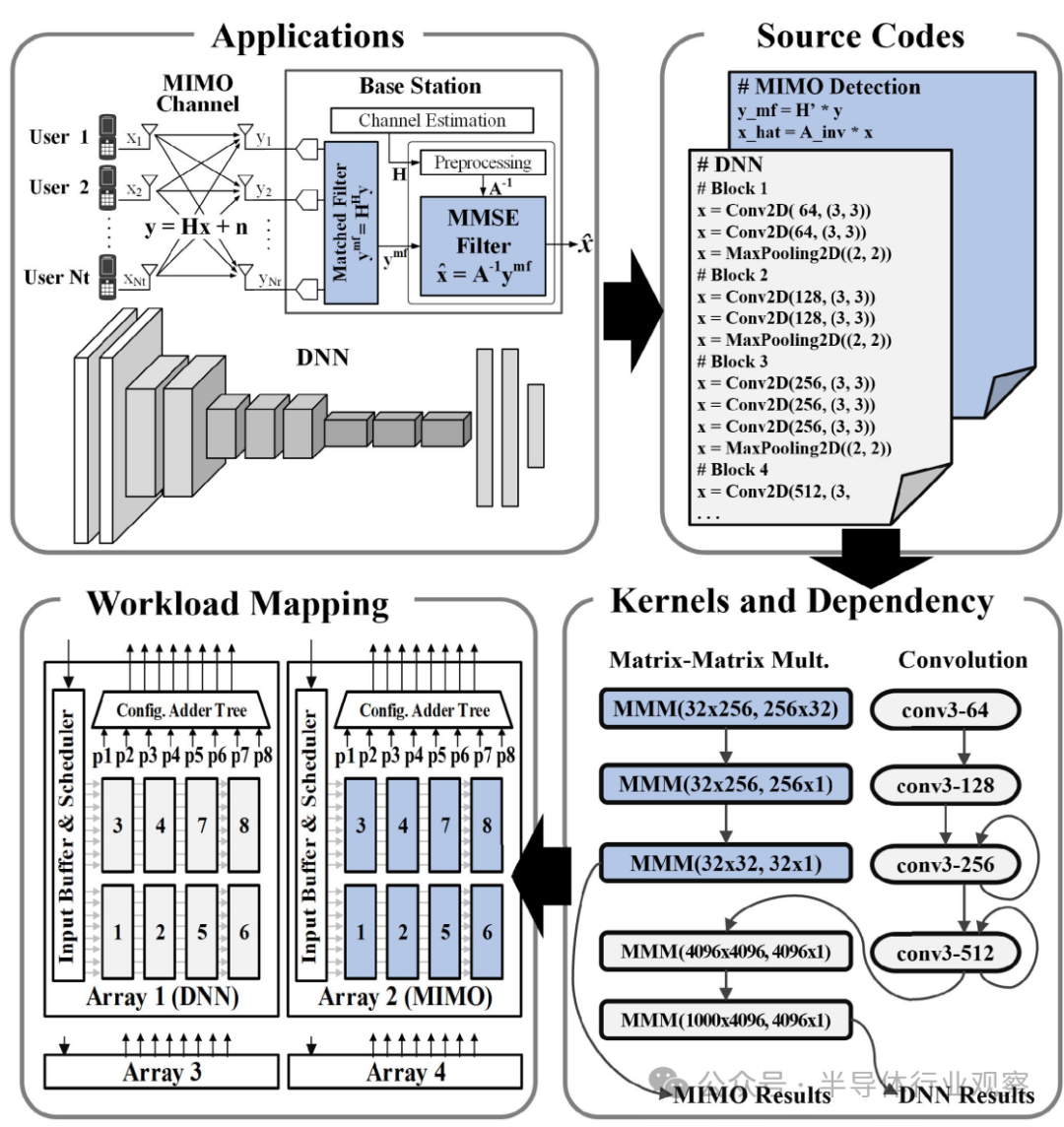

為了實(shí)現(xiàn)這一目標(biāo),我們開(kāi)發(fā)了一套編譯程序,如圖 12 所示。工作負(fù)載首先被分割成幾個(gè)部分,即使用 conv 核或 MMM 核的部分,或二者兼有的部分,這些部分可以通過(guò)適當(dāng)?shù)呐渲弥苯佑成涞紸rvon DSP上。此外,一些計(jì)算核之間的中間步驟可由FPGA主機(jī)執(zhí)行。具體來(lái)說(shuō),conv的配置是基于濾波器和輸入的大小(R × S × C)制定的,而MMM的配置是基于矩陣的尺寸制定的。隨后,工作負(fù)載中的conv和MMM核心將根據(jù)既定的指令和內(nèi)存數(shù)據(jù)配置,被調(diào)度并分配給Arvon DSP的矢量引擎。這一分配過(guò)程綜合考慮了多個(gè)關(guān)鍵因素,包括提高資源利用率、增強(qiáng)數(shù)據(jù)的可重用性,以及最小化端到端的延遲。

圖12 工作負(fù)載映射的編譯流程說(shuō)明

矢量引擎采用靜態(tài)權(quán)重方案,其核心的權(quán)重分配給 PE。為了將MMM映射到矢量引擎,權(quán)重矩陣的每一行都被分配給PE,從而有效地將一維矢量分配到二維陣列中。具有相同權(quán)重矩陣的行可以分配給同一組PE。在涉及多個(gè)核的多租戶場(chǎng)景中,不同權(quán)重矩陣的行可以分配給不同的分區(qū),在圖12和13中用p1–p8表示。分區(qū)輸出被定向到可配置加法器樹(shù)的相應(yīng)輸入端,確保計(jì)算出單獨(dú)的和作為輸出。

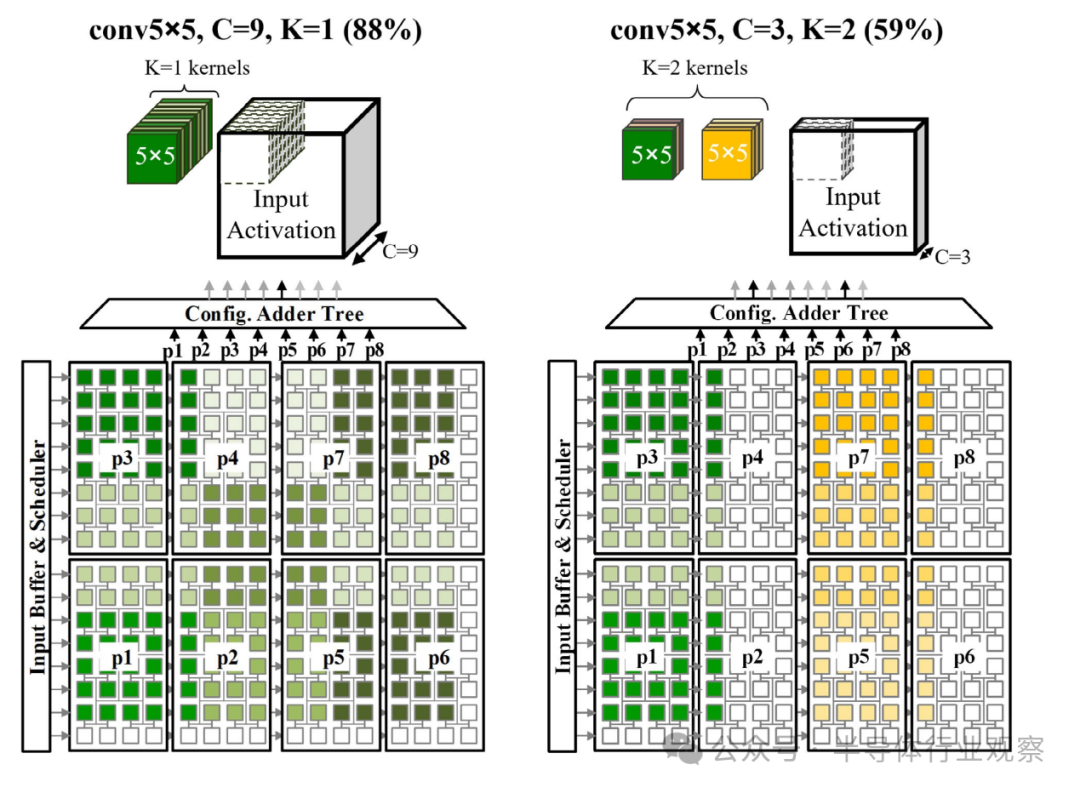

conv 的權(quán)重映射與多租戶 MMM 的情況類似,因?yàn)槠淇赡苌婕岸鄠€(gè)卷積核。圖13展示了兩個(gè)卷積操作示例的映射。每個(gè)卷積核的大小為 R × S × C,并通過(guò)在二維中編織三維切片將其展開(kāi)到二維 PE 陣列中。在滑動(dòng)卷積窗口下的三維輸入激活元素也相應(yīng)地展開(kāi)到二維PE數(shù)組上。輸入激活在PE數(shù)組內(nèi)部保留,以便通過(guò)相鄰PE之間的脈動(dòng)數(shù)據(jù)轉(zhuǎn)發(fā)實(shí)現(xiàn)水平和/或垂直重用。對(duì)于單個(gè)卷積核的情況(如圖 13 中的第一個(gè)示例),可以不考慮分區(qū)邊界進(jìn)行映射,從而實(shí)現(xiàn)高效利用。然而,當(dāng)存在多個(gè)卷積核時(shí),例如圖13中的第二個(gè)示例,每個(gè)卷積核都需要與分區(qū)邊界對(duì)齊,從而降低了利用率。

圖13 不同內(nèi)核大小的映射示例

VI. 芯片測(cè)量與比較

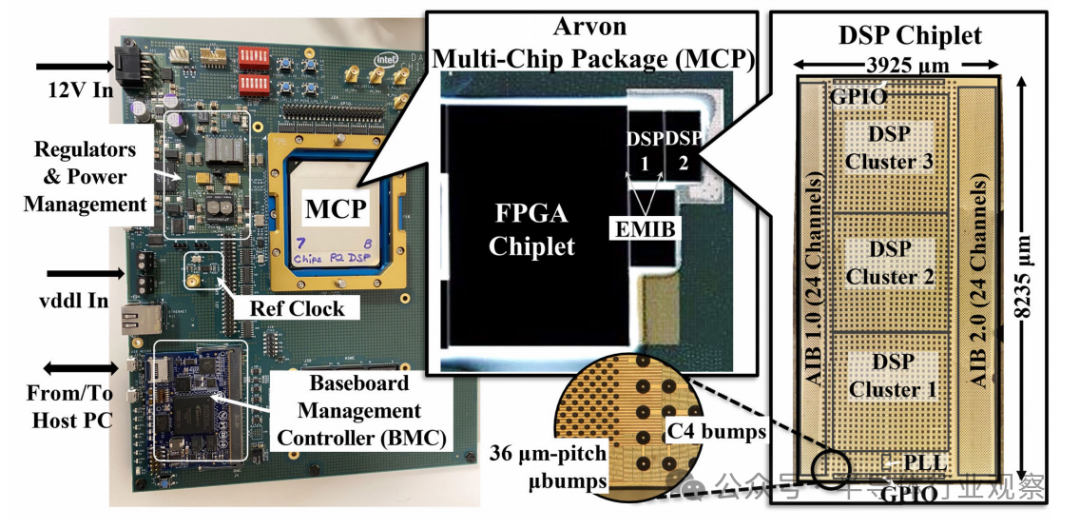

DSP 芯粒采用 22 nm FinFET 技術(shù)制造,面積為 32.3 mm2,如圖 14 所示。為了構(gòu)建 Arvon SiP,我們將一個(gè) 14 nm FPGA 芯粒和兩個(gè) DSP 芯粒通過(guò)兩個(gè)十層 EMIB 相互封裝和互連,同時(shí)使用 36 微米間距的微凸塊。AIB 1.0 側(cè)的平均導(dǎo)線長(zhǎng)度為 1.5 毫米,而 AIB 2.0 側(cè)的平均導(dǎo)線長(zhǎng)度為 0.85 毫米。

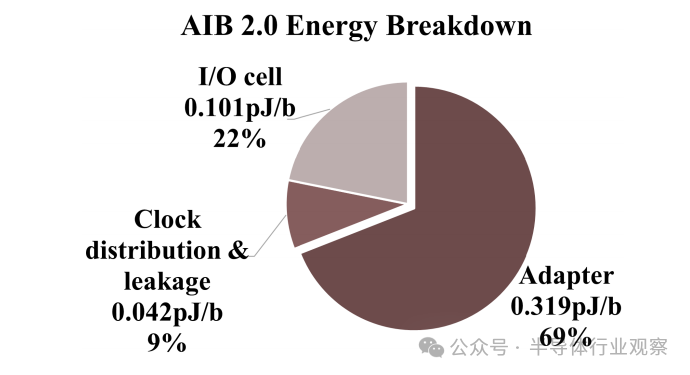

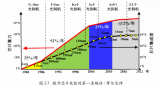

在室溫和 0.85 V 的芯粒電壓下,每個(gè) DSP 集群的最高工作頻率為 675 MHz,功耗為 0.76 W。在這種配置下,DSP 芯粒的峰值性能為 4.14 TFLOPS,功耗效率達(dá)到 1.8 TFLOPS/W。在 0.85 V I/O 電壓和 800-MHz 時(shí)鐘(受 FPGA 時(shí)鐘頻率限制)條件下,AIB 1.0 I/O 的功耗為 0.44 pJ/b,包括適配器在內(nèi)為 0.85 pJ/b,傳輸延遲為 3.75 ns。在室溫條件下,輸入/輸出電壓為 0.4 V,時(shí)鐘頻率為 2 GHz,AIB 2.0 輸入/輸出每比特消耗 0.10 pJ,包括適配器在內(nèi)為 0.46 pJ/b,傳輸延遲為 1.5 ns。AIB 2.0 接口的能耗分解如圖 15 所示。適配器的能耗占絕大部分,為 0.32 pJ/b,約占總能耗的 69%。另一方面,I/O 單元僅消耗 0.10 pJ/b,約占總能耗的 22%。I/O 單元能耗較低的原因是利用了 0.4 V 的低信號(hào)擺幅。

圖14 測(cè)試裝置、Arvon多芯粒封裝和DSP芯粒顯微照片

圖15 AIB 2.0 接口的能耗分解

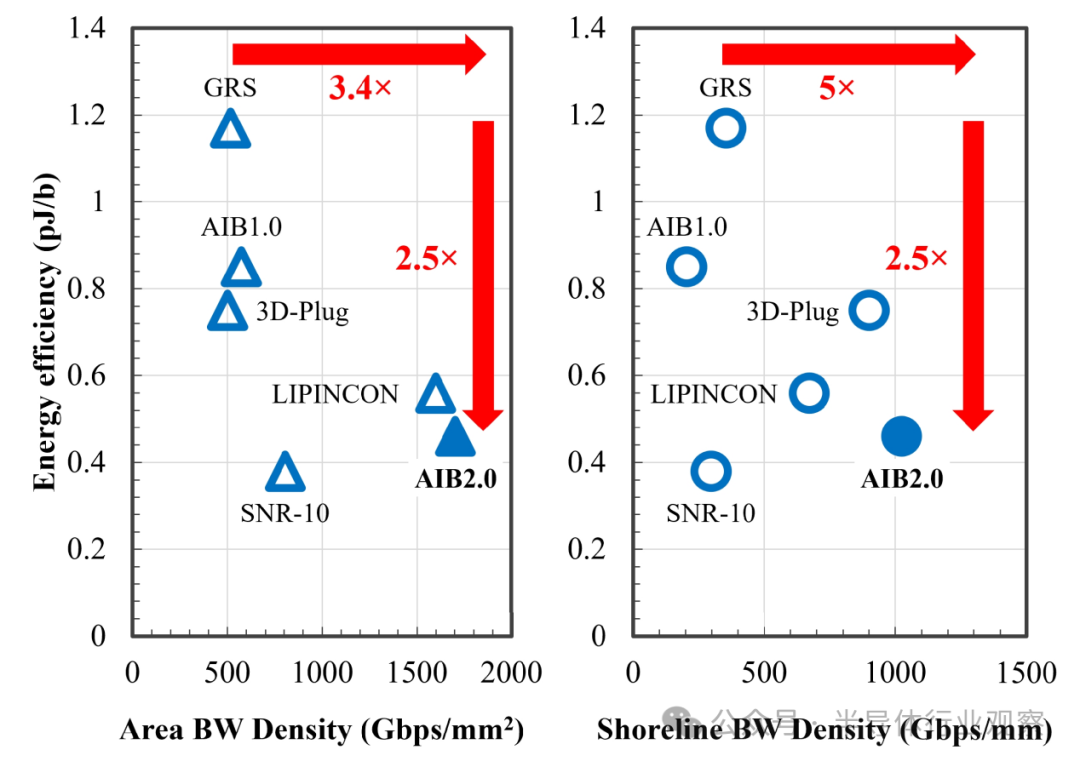

圖16 能效與區(qū)域帶寬密度(左)和海岸線帶寬密度(右)的關(guān)系

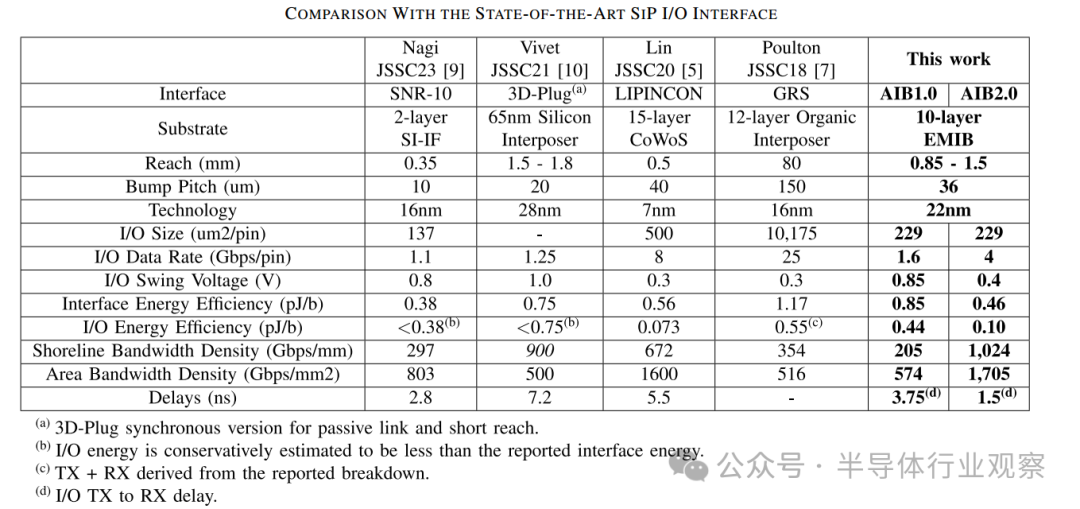

Arvon的AIB I/O 接口與最先進(jìn)的 SiP I/O 接口的比較見(jiàn)表II。與 AIB 接口類似,SNR-10 、3-D-Plug 和 LIPINCON 也是并行 I/O 接口。其中,LIPINCON 的數(shù)據(jù)傳輸率最高,達(dá)到 8 Gb/s/pin,I/O 能耗最低,在 0.3 V 信號(hào)擺幅下僅為 0.073 pJ/b;3-D-Plug 的帶寬密度最高,達(dá)到 900 Gb/s/mm 的海岸線;SNR-10 的 I/O 尺寸最小,僅為 137 μm2。GRS 是一種高速串行 I/O 接口,可提供 25 Gb/s/pin,能效為 1.17 pJ/b。我們的 AIB 2.0 原型提供了一個(gè)極具吸引力的解決方案,其 I/O 能耗僅為 0.10 pJ/b,如果包括適配器,則為 0.46 pJ/b。如表 II 所示,它還實(shí)現(xiàn)了 1.0-Tb/s/mm 的海岸線和 1.7-Tb/s/mm2 面積的最高帶寬密度。圖 16 比較了芯片間接口的能效、面積帶寬密度和海岸線帶寬密度。與 GRS 接口相比,AIB 2.0 接口的能效、面積帶寬密度和海岸線帶寬密度分別提高了 2.5 倍、3.4 倍和 5 倍,優(yōu)于其他接口。

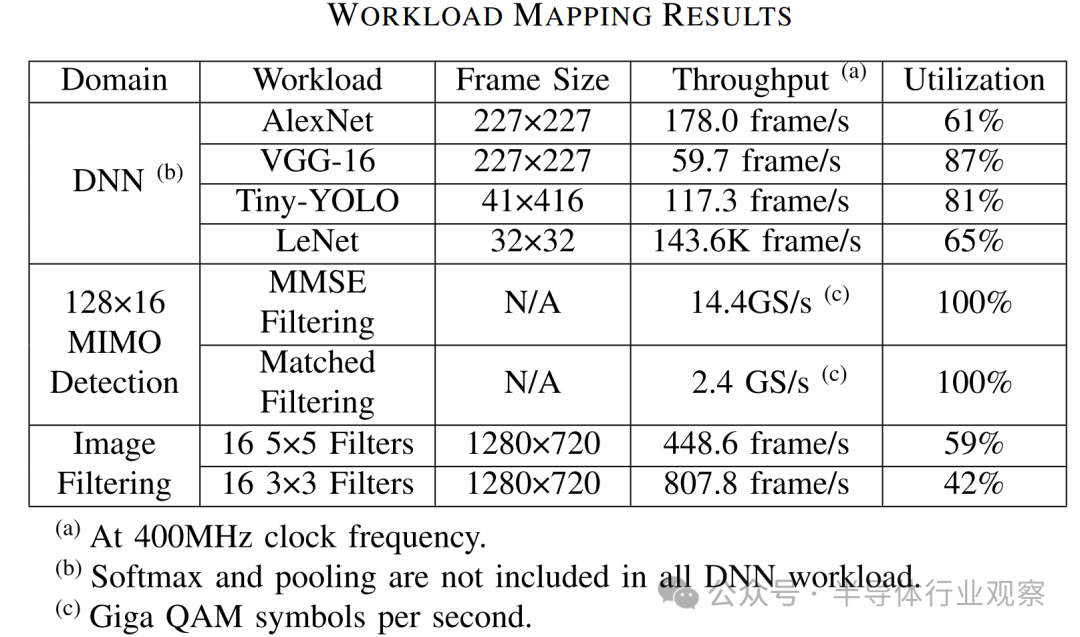

我們展示了可以利用Arvon的各種應(yīng)用的工作負(fù)載映射,包括深度神經(jīng)網(wǎng)絡(luò)(DNN)、多輸入多輸出(MIMO)信號(hào)處理和圖像濾波。工作負(fù)載大小、總體吞吐量和利用率在表III中進(jìn)行了總結(jié)。除了常用的DNN模型外,128×16 MIMO檢測(cè)工作負(fù)載利用128個(gè)接收天線來(lái)檢測(cè)16個(gè)單天線用戶。此任務(wù)涉及的處理包括最小均方誤差(MMSE)濾波操作,該操作需要使用矩陣-矩陣乘法(MMM)計(jì)算濾波矩陣,然后使用MMM應(yīng)用濾波矩陣。為了執(zhí)行這些操作,需要使用尺寸為32×256、256×32、32×32和32×1的MMM核來(lái)完成此工作負(fù)載。這些計(jì)算核可以高效地映射到PE陣列,利用率達(dá)到100%。圖像濾波工作負(fù)載涉及16個(gè)5×5的濾波器和16個(gè)3×3的濾波器,這些二維濾波器應(yīng)用于1280×720的圖像幀,這些操作均需要采用卷積核來(lái)進(jìn)行。不過(guò),由于濾波器尺寸較小,其利用率低于其他工作負(fù)載。這些示例工作負(fù)載的結(jié)果表明,Arvon的異構(gòu)SiP架構(gòu)為神經(jīng)網(wǎng)絡(luò)(NN)和通信處理提供了靈活性、性能和效率。

表II

表III

VII. 總結(jié)

Arvon是一個(gè)異構(gòu)系統(tǒng)級(jí)封裝(SiP),它使用嵌入式多芯片互連橋(EMIBs)集成了一個(gè)FPGA芯粒和兩個(gè)DSP芯粒。這種集成方式使Arvon不但能夠擁有FPGA作為主機(jī)的靈活性,還能擁有DSP的高計(jì)算性能和效率。

SiP 的主要特點(diǎn)是采用并行、短距離的 AIB 1.0 和 AIB 2.0 接口,用于無(wú)縫連接芯粒。輸入/輸出(I/O)單元設(shè)計(jì)緊湊,以數(shù)字為主,并且可綜合。這些單元非常靈活,能夠支持多種模式。此外,它們還采用了依賴模式的電源門控和兩級(jí)時(shí)鐘分布,從而提高了能效。我們使用 36 微米間距微凸塊實(shí)現(xiàn)了低擺幅 4-Gb/s AIB 2.0 接口,能效為 0.10 pJ/b,若包括適配器在內(nèi)則為 0.46 pJ/b,同時(shí)擁有1.024-Tb/s/mm 海岸線和 1.705-Tb/s/mm2的面積的帶寬密度。該接口采用 與AXI 兼容的總線協(xié)議進(jìn)行抽象,簡(jiǎn)化了主機(jī)和 DSP 的使用。

Arvon中的每個(gè)DSP芯粒都采用低延遲的脈動(dòng)陣列架構(gòu),擁有3072個(gè)FP16 PE。這些PE按層次分為三個(gè)集群,每個(gè)集群包含八個(gè)32-PE單元。這種細(xì)粒度的組織結(jié)構(gòu)允許同時(shí)并行執(zhí)行多個(gè)工作負(fù)載。每個(gè) DSP 芯粒可提供 4.14 TFLOPS 的峰值性能,功耗效率為 1.8 TFLOPS/W。我們開(kāi)發(fā)了一套將工作負(fù)載映射到 Arvon 上的系統(tǒng)程序,并演示了 Arvon 可以加速的各種工作負(fù)載,以實(shí)現(xiàn)具有競(jìng)爭(zhēng)力的性能和利用率。

-

dsp

+關(guān)注

關(guān)注

556文章

8155瀏覽量

357283 -

FPGA

+關(guān)注

關(guān)注

1645文章

22036瀏覽量

618105 -

芯片

+關(guān)注

關(guān)注

459文章

52471瀏覽量

440440 -

系統(tǒng)級(jí)封裝

+關(guān)注

關(guān)注

0文章

40瀏覽量

9264 -

芯粒

+關(guān)注

關(guān)注

0文章

65瀏覽量

274

原文標(biāo)題:一種集成FPGA和DSP芯粒的異構(gòu)系統(tǒng)級(jí)封裝

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

異構(gòu)集成的三個(gè)層次解析

Nexar如何為FPGA設(shè)計(jì)提供一種全新的方法?

北極雄芯開(kāi)發(fā)的首款基于Chiplet異構(gòu)集成的智能處理芯片“啟明930”

一種基于DSP和FPGA的雷達(dá)信號(hào)分選電路設(shè)計(jì)

一種基于DSP+FPGA的控制系統(tǒng)方案設(shè)計(jì)

一種異構(gòu)雙核系統(tǒng)芯片平臺(tái)設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的異構(gòu)可重配置DSP平臺(tái)

一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

探究一種新的可配置處理器的異構(gòu)多核線程級(jí)動(dòng)態(tài)調(diào)度模型

芯粒峰會(huì):如何打通芯粒市場(chǎng)

一種集成FPGA和DSP芯粒的異構(gòu)系統(tǒng)級(jí)封裝

一種集成FPGA和DSP芯粒的異構(gòu)系統(tǒng)級(jí)封裝

評(píng)論