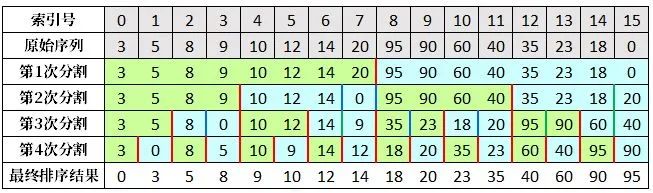

在上篇文章中我們介紹了如何對雙調序列進行排序,操作過程如下圖所示。

其特征是每次分割都是將原始的序列分成兩個等長序列。

例如:原始序列長度為16,第1次分割將其分為2個長度為8的序列;第2次分割將第1次分割的排序結果(長度仍為16)分為4個長度為4的序列;第3次分割將第2次分割的排序結果分為8個長度為2的序列;第4次分割將第3次分割的排序結果分為16個長度為1的序列。

圖中相鄰的綠色標記和藍色標記序列構成一組進行比較。

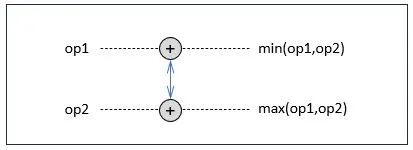

為進一步說明,我們定義操作符?,如下圖所示。

兩個操作符?由雙向箭頭連接,表示彼此之間共享數(shù)據,即下方的?可接收上方的?對應操作數(shù)op1,同時上方的?可接收下方的?對應操作數(shù)op2。

位于上方的?輸出op1與op2中的較小者,位于下方的?輸出op1與op2的較大者,簡言之?表示對兩個輸入數(shù)據進行升序排序。

此外,還有一個關鍵點就是圖中虛線的含義。

可以看到op1與min(op1,op2)在一條直線上,op2與max(op1,op2)在一條直線上。

同一條直線上的兩個數(shù)據其位置是相同的。

即若op1是0號數(shù)據,那么min(op1,op2)也必須放到0號位置上,這就是所謂的原位(In-place)運算。

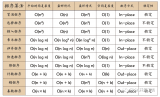

在?操作符的定義下,長度為16的雙調序列的排序過程如下圖所示。

圖中第1列為二進制數(shù),表示序列中每個元素在序列中的位置也就是地址,用于體現(xiàn)原位運算的特征。

整個排序過程分為4個階段完成對應圖中的Stage 0~Stage3。

在Stage 0中,?的兩個操作數(shù)的地址間距為8(例如,3來自0號地址,95來自8號地址);在Stage 1中間距為4;在Stage 2中間距為2;在Stage 3中間距為1。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21963瀏覽量

614094 -

比較器

+關注

關注

14文章

1840瀏覽量

108526

原文標題:用FPGA實現(xiàn)雙調排序(2)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

基于FPGA的雙口RAM實現(xiàn)及應用

怎么實現(xiàn)6通道電源排序

四種FPGA 電源排序方案

如何選擇FPGA電源排序?這幾個方法交給你

算法的原理是什么?基數(shù)排序是如何實現(xiàn)的?

用FPGA實現(xiàn)糾錯編碼的一種方法

分析FPGA 電源排序的四種方案介紹

用FPGA實現(xiàn)FFT算法的方法

FPGA實現(xiàn)雙調排序算法的探索與實踐

FPGA實現(xiàn)雙調排序方法詳解

用FPGA實現(xiàn)雙調排序的方法(2)

用FPGA實現(xiàn)雙調排序的方法(2)

評論