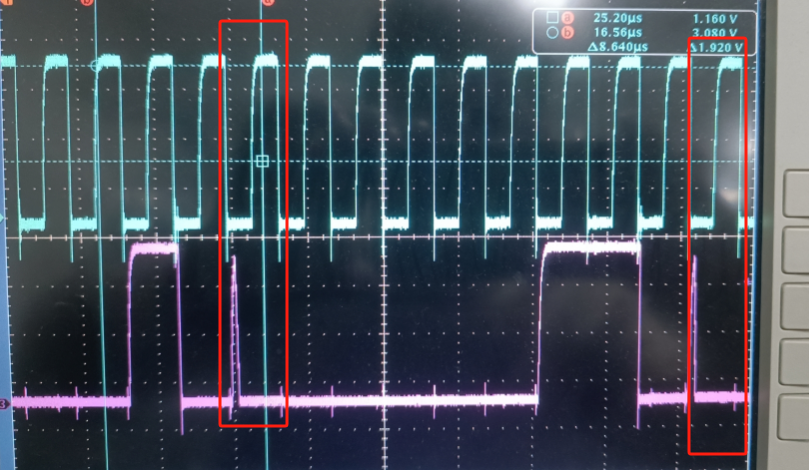

在I2C的波形中,經(jīng)常會(huì)發(fā)現(xiàn)有這樣的脈沖毛刺,會(huì)被認(rèn)為是干擾或者器件不正常。

看到這個(gè)波形時(shí),可以先數(shù)一下出現(xiàn)在第幾個(gè)clock的位置,如果出現(xiàn)在第9個(gè)clock的低電平期間,就不是干擾或者器件異常導(dǎo)致。

在I2C的協(xié)議中,不管是地址匹配階段還是數(shù)據(jù)讀寫階段,第9個(gè)clock都是ACK和NACK位;

其中NACK為第9個(gè)SCL上升沿時(shí)SDA高電平:

ACK為第9個(gè)SCL上升沿時(shí)SDA低電平:

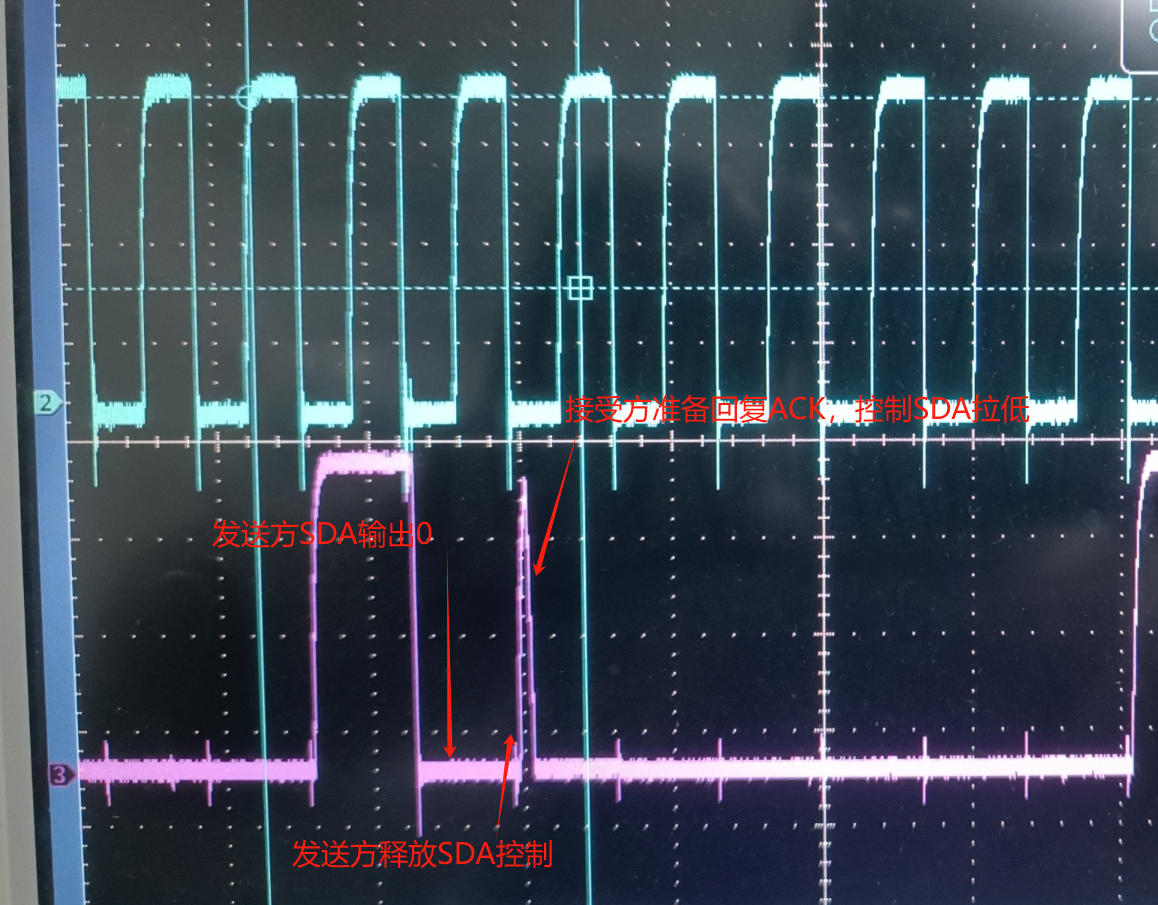

在地址匹配階段由從機(jī)來回復(fù)ACK,在數(shù)據(jù)收發(fā)階段由接受方來回復(fù)ACK。

那么I2C是雙向半雙工通信,SDA引腳通過主機(jī)和從機(jī)共同控制,ACK回復(fù)過程意味著發(fā)送方會(huì)在通過SDA發(fā)送了8個(gè)bit的數(shù)據(jù)后釋放SDA控制權(quán)給接受方,此時(shí)如果最后一個(gè)波形數(shù)據(jù)BIT0是0,那SDA會(huì)在SCL下降沿后從拉低狀態(tài)被釋放,由于上拉電阻的作用SDA就會(huì)恢復(fù)到高電平,但緊接著接受方開始數(shù)據(jù)建立開啟對(duì)SDA的控制權(quán),拉低SDA引腳準(zhǔn)備回復(fù)ACK,于是SDA信號(hào)被再次拉低。

由于整個(gè)過程是連續(xù)的,且都會(huì)在SCL第9個(gè)Clock的低電平期間完成,產(chǎn)生的波形就會(huì)像一個(gè)毛刺被誤認(rèn)為干擾。實(shí)際上這個(gè)波形的出現(xiàn)不用在意,可以不采取任何措施。

-

單片機(jī)

+關(guān)注

關(guān)注

6063文章

44923瀏覽量

646974 -

mcu

+關(guān)注

關(guān)注

146文章

17838瀏覽量

360452 -

嵌入式

+關(guān)注

關(guān)注

5141文章

19535瀏覽量

315012 -

I2C

+關(guān)注

關(guān)注

28文章

1534瀏覽量

127022 -

GD32

+關(guān)注

關(guān)注

7文章

418瀏覽量

25158

發(fā)布評(píng)論請(qǐng)先 登錄

I2C在MM32F032/MM32F0140系列MCU上的實(shí)現(xiàn)

I2C通信開發(fā)障礙以及總結(jié)

為什么MCU I2C波形中會(huì)出現(xiàn)脈沖毛刺?#MCU #單片機(jī) #嵌入式開發(fā) #i2c

mcu復(fù)位導(dǎo)致I2C異常

MCU實(shí)現(xiàn)I2C通信

I2C接口配置ES7243錄音芯片,MCU(STM32)收不到I2C ACK的問題

硬件I2C與模擬I2C

MSP MCU I2C入門指南

I2C通信沒反應(yīng)怎么辦?

如何提高I2C調(diào)試效率?

為什么MCU I2C波形中會(huì)出現(xiàn)的脈沖毛刺?

為什么MCU I2C波形中會(huì)出現(xiàn)的脈沖毛刺?

評(píng)論