在實際的電路設計過程中,存在傳播延時和信號變換延時。由延時引起的競爭與冒險現(xiàn)象會影響輸出的正確與否。下面將就競爭與冒險產(chǎn)生的原因,判斷方法和避免競爭與冒險的方法進行討論,希望對諸位有所幫助。

產(chǎn)生原因

競爭:在組合邏輯電路中不同路徑的輸入信號到達同一個門級電路時,在時間上有先有后,這種先后時間上的差異稱之為競爭(Competition)

冒險:由于競爭的存在,信號在過渡時間瞬間可能產(chǎn)生錯誤的輸出,例如尖峰脈沖。成為冒險。

有競爭不一定產(chǎn)生冒險,但是有冒險一定存在競爭。

判斷方法

代數(shù)法

在電路的邏輯表達式中保持一個變量不變,其余變量用0或者1替代如果邏輯表達式可以化成:

F = A + ~A

或

F = A·~A

的形式則可以判斷出此邏輯存在競爭與冒險。

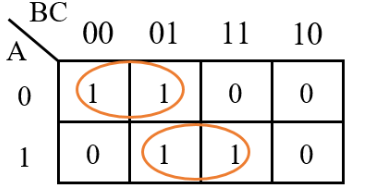

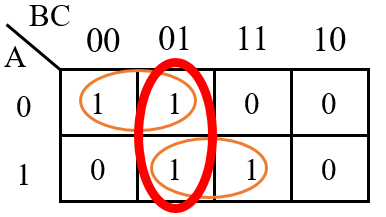

卡諾圖法

存在兩個相切的卡諾圖,若在相切處沒有其他卡諾圖包圍,可能會出現(xiàn)競爭與冒險現(xiàn)象。如下圖所示:

F = ~A·~B + A·C

F = A·~B + B·~C

消除方法

常見的避免競爭與冒險的辦法有以下四種:

增加濾波電容,濾除窄脈沖

在輸出端并聯(lián)一個小電容,將尖峰脈沖幅度削弱至門電路閾值以下。這種方法的突出問題是會增加輸出電壓的翻轉(zhuǎn)時間,容易破壞波形。

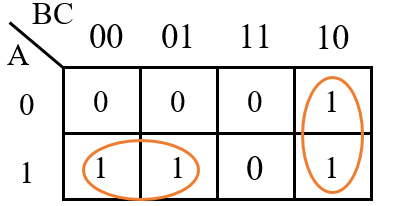

修改邏輯,增加冗余項

在卡諾圖中兩個相切的圈之間增加一個圈,并加入邏輯表達式之中。如下圖所示:

F = ~A·~B + A·C + ~B·C

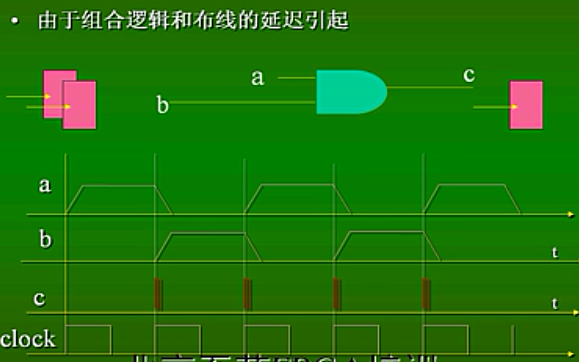

使用時鐘同步電路,利用觸發(fā)器進行打拍延遲

同步電路信號的變化都發(fā)生在時鐘邊沿,對于D觸發(fā)器的輸入端而言,只要毛刺不出現(xiàn)在時鐘上升沿并且還不滿足建立保持時間要求,就不會對系統(tǒng)產(chǎn)生危害,即D觸發(fā)器對輸入端毛刺不敏感。因此在時鐘邊沿驅(qū)動下,對組合邏輯信號進行延遲打拍即可消除競爭冒險。實際設計過程中可以根據(jù)設計需求對信號進行合理的打拍延遲。

采用格雷碼計數(shù)器

在遞加的多bit位計數(shù)器,計數(shù)值有時候會發(fā)生多bit的跳變,產(chǎn)生短暫的尖峰脈沖。而格雷碼計數(shù)器,計數(shù)時相鄰的數(shù)之間只有一個bit數(shù)據(jù)發(fā)生跳變,所以能有效避免競爭與冒險。

總結(jié)

在消除競爭與冒險的辦法中,增加濾波電容和邏輯冗余都不是在代碼層面考慮的問題。利用觸發(fā)器在時鐘同步電路下對異步信號進行打拍延時常在Verilog中使用。

審核編輯 黃宇

-

電路

+關注

關注

173文章

6022瀏覽量

174417 -

競爭冒險

+關注

關注

0文章

2瀏覽量

5050

發(fā)布評論請先 登錄

FPGA中競爭與冒險的前世今生

FPGA設計中競爭冒險問題的研究

怎樣消除競爭冒險

組合邏輯電路的競爭冒險,輸入信號同時從1變0會產(chǎn)生競爭冒險嗎

FPGA中的競爭和冒險現(xiàn)象

什么是競爭與冒險現(xiàn)象?怎樣判斷?如何消除?

簡談FPGA的競爭冒險和毛刺問題

FPGA | 競爭冒險和毛刺問題

組合邏輯中的競爭與冒險及毛刺的處理方法

競爭與冒險產(chǎn)生的原因,判斷方法和避免競爭與冒險的方法

競爭與冒險產(chǎn)生的原因,判斷方法和避免競爭與冒險的方法

評論