NVMe Host Controller IP

介紹

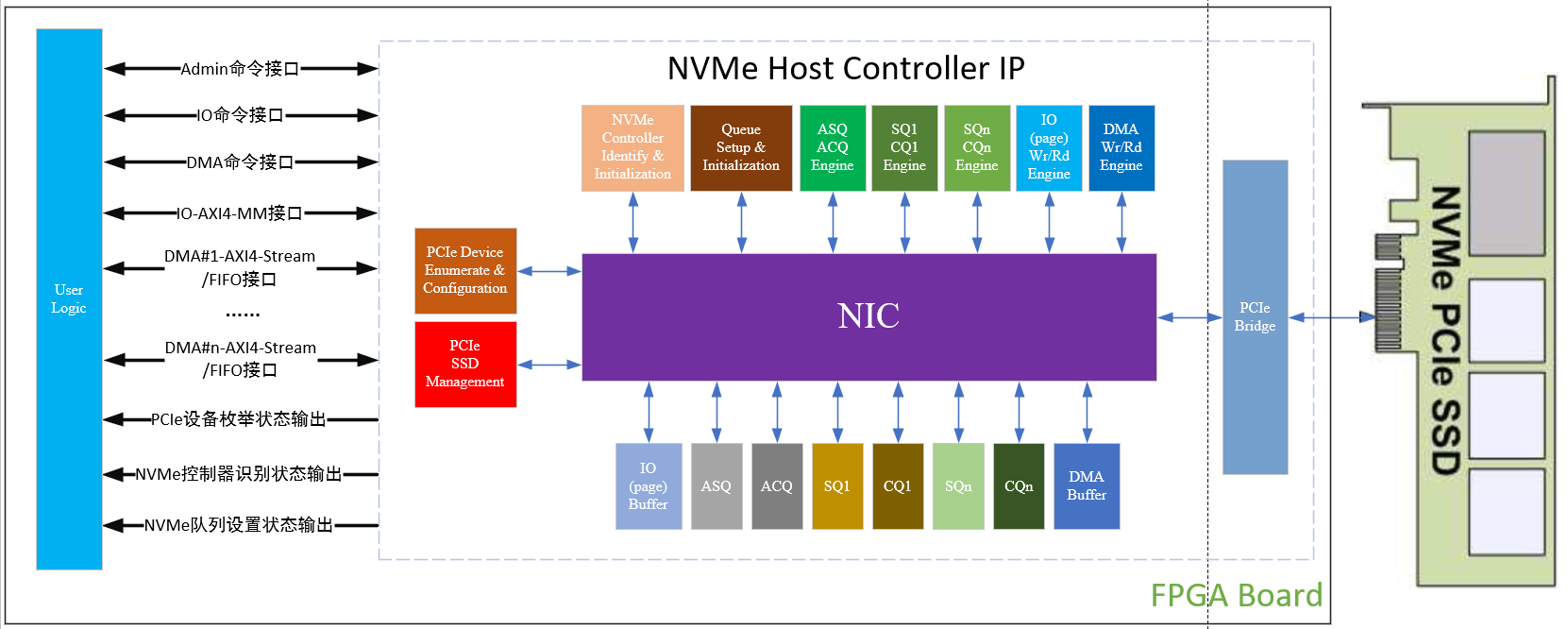

NVMe Host Controller IP可以連接高速存儲PCIe SSD,無需CPU和外部存儲器,自動加速處理所有的NVMe協議命令,具備獨立的數據寫入AXI4-Stream/FIFO接口和數據讀取AXI4-Stream/FIFO接口,非常適合于超高容量和超高性能的應用。此外,NVMe Host Controller IP支持RAID存儲,從而可實現更高存儲性能和存儲容量。

無需CPU,NVMe Host Controller IP自動執行對PCIe SSD的PCIe設備枚舉和配置、NVMe控制器識別和初始化、NVMe隊列設置和初始化,實現必須以及可選的NVMe Admin Command Set和NVM Command Set,實現對PCIe SSD的復位/斷電管理、IO(Page)讀寫、DMA讀寫和數據擦除功能,提供用戶一個簡單高效的接口實現高性能存儲解決方案。

NVMe Host Controller IP DMA讀寫的順序傳輸長度可以配置,最小是4K-Byte,最大是512K-Byte。順序傳輸長度配置為4K-Byte,NVMe Host Controller IP所消耗的BRAM最少,但是可以達到CrystalDiskMark測試軟件RND4K Q32T16測試模式下的讀寫性能。順序傳輸長度配置為128K-Byte,NVMe Host Controller IP所消耗的BRAM比較多,可以達到CrystalDiskMark測試軟件SEQ128K Q32T1測試模式下的讀寫性能。

針對多路數據通道訪問PCIe SSD,使用NVMe的多隊列特性,NVMe Host Controller IP支持靈活配置DMA讀寫的通道個數,按照NVMe隊列優先級仲裁機制,實現多個DMA通道對同一塊PCIe SSD的高效訪問,從而達到多路數據通道訪問的并行需求和QoS要求。

特性

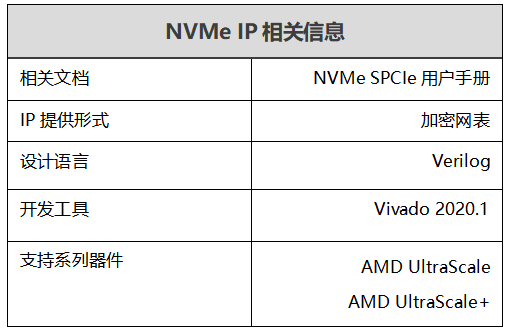

支持Ultrascale+,Ultrascale,7 Series FPGA

支持PCIe Gen4,PCIe Gen3,PCIe Gen2 SSD

無需CPU和外部存儲器

自動實現對PCIe SSD的PCIe設備枚舉、NVMe控制器識別和NVMe隊列設置

支持對PCIe SSD的NVM Subsystem Reset、Controller Reset和Shutdown

支持NVMe Admin Command Set:Identify、SMART、Create/Delete IO Submission/Completion Queue、Set Feature

支持NVMe NVM Command Set:Write、Read、Flush、Dataset Management

提供1個Admin命令接口,實現對PCIe SSD的復位/斷電管理功能

提供1個IO命令接口,實現對PCIe SSD的IO(Page)讀寫、Cache Flush和邏輯數據塊擦除功能;提供1個IO-AXI4-MM接口讀寫IO(page)數據

提供1個DMA命令接口,實現對PCIe SSD的DMA讀寫功能;提供1個DMA-AXI4-Stream-In/Out或DMA-FIFO-In/Out接口實現DMA數據的輸入和輸出

DMA讀寫的順序傳輸長度可以配置,4K-Byte~512K-Byte;不同的順序傳輸長度對應不同的DMA讀寫性能,同時也消耗不一樣的BRAM資源

針對多通道DMA需求,可以配置4個DMA命令接口和4個DMA-AXI4-Stream-In/Out或DMA-FIFO-In/Out接口

NVMe隊列的個數(配置DMA通道的個數)和深度可配置,平衡對PCIe SSD的DMA性能和消耗的邏輯資源

支持NVMe Admin和IO命令的超時和錯誤處理恢復機制,提供詳盡的訪問錯誤狀態輸出

支持的NVMe設備:

Base Class Code:01h(mass storage),Sub Class Code:08h(Non-volatile),Programming Interface:02h(NVMHCI)

MPSMIN(Memory Page Size Minimum):0(4K-byte)

MDTS(Maximum Data Transfer Size):大于等于順序傳輸長度或0(無限制)

LBA Unit:512-byte,1024-byte,2048-byte或4096-byte

一個NVMe Host Controller IP直接連接到PCIe SSD

易于集成的同步、可綜合Verilog設計

通過完全驗證的NVMe Host Controller IP

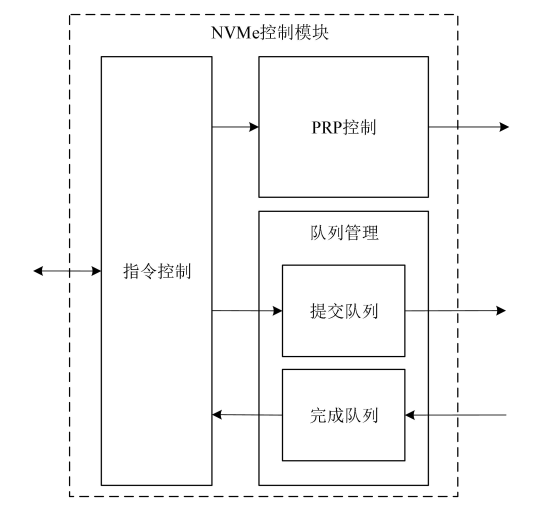

概述

NVMe Host Controller IP作為一個對PCIe SSD的高性能存儲控制器,不但提供對PCIe SSD的配置管理功能,而且提供對PCIe SSD的IO(Page)讀寫以及DMA讀寫功能。

NVMe Host Controller IP具備PCIe SSD Manegement,實現對PCIe SSD的復位/斷電管理功能。

NVMe Host Controller IP具備ASQ/ACQ引擎,實現NVMe Admin Command Set:Identify、SMART、Create/Delete IO Submission/Completion Queue、Set Feature。

NVMe Host Controller IP具備IO(Page) Wr/Rd引擎和SQ1/CQ1引擎,實現對PCIe SSD的IO(Page)讀寫、Cache Flush和邏輯數據塊擦除功能。

NVMe Host Controller IP具備DMA Wr/Rd引擎和SQn/CQn引擎,實現對PCIe SSD的DMA讀寫功能。

上電后,NVMe Host Controller IP內置的PCIe Device Enumerate & Configuration自動實現對PCIe SSD的PCIe設備枚舉和配置;然后內置的NVMe Controller Identify & Initialization自動實現對PCIe SSD的NVMe控制器識別和初始化;最后內置的Queue Setup & Initialization自動實現對PCIe SSD的NVMe隊列設置和初始化。上電后至此,NVMe Host Controller IP完成對PCIe SSD的所有配置和初始化工作,可以開始提供對PCIe SSD的讀寫、擦除、復位操作。

圖 2 NVMe Host Controller IP結構框圖

產品規格

性能

PCIe配置參數:Max Payload Size=256-byte,Max Read Request Size=512-byte

PCIe Gen3 SSD,Seq=128KB,1個DMA通道:

DMA寫入速度可達3300MB/s

DMA讀取速度可達3500MB/s

PCIe Gen2 SSD,Seq=128KB,1個DMA通道:

DMA寫入速度可達1700MB/s

DMA讀取速度可達1800MB/s

資源

KU040

表3.1 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,1-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 17251 | 25429 | 87 | 1 |

| NVMe Host Controller | 12780 | 17477 | 70 | 0 |

| PCIe Bridge | 5473 | 7952 | 17 | 1 |

表3.2 PCIe Gen3 SSD,Seq=4K,Queue Depth=8,1-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 16600 | 22812 | 31 | 1 |

| NVMe Host Controller | 11144 | 14864 | 14 | 0 |

| PCIe Bridge | 5461 | 7948 | 17 | 1 |

表3.3 PCIe Gen3 SSD,Seq=4K,Queue Depth=8,2-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 21068 | 28135 | 43 | 1 |

| NVMe Host Controller | 15596 | 20163 | 26 | 0 |

| PCIe Bridge | 5475 | 7962 | 17 | 1 |

ZU7EV

表3.4 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,1-DMA

| LUTs | FFs | BRAMs | URAM | PCIe | |

| 總資源 | 23925 | 34570 | 40 | 8 | 1 |

| NVMe Host Controller | 12621 | 17486 | 6 | 8 | 0 |

| PCIe Bridge | 11311 | 17085 | 34 | 0 | 1 |

表3.5 PCIe Gen3 SSD,Seq=4K,Queue Depth=16,1-DMA

| LUTs | FFs | BRAMs | URAM | PCIe | |

| 總資源 | 23128 | 33037 | 40 | 2 | 1 |

| NVMe Host Controller | 11811 | 15956 | 6 | 2 | 0 |

| PCIe Bridge | 11319 | 17081 | 34 | 0 | 1 |

表3.6 PCIe Gen3 SSD,Seq=4K,Queue Depth=16,2-DMA

| LUTs | FFs | BRAMs | URAM | PCIe | |

| 總資源 | 28201 | 39453 | 44 | 4 | 1 |

| NVMe Host Controller | 16893 | 22365 | 10 | 4 | 0 |

| PCIe Bridge | 11308 | 17088 | 34 | 0 | 1 |

審核編輯 黃宇

-

控制器

+關注

關注

114文章

16951瀏覽量

182754 -

SSD

+關注

關注

21文章

2944瀏覽量

119069 -

PCIe

+關注

關注

16文章

1317瀏覽量

84623 -

dma

+關注

關注

3文章

571瀏覽量

102253 -

nvme

+關注

關注

0文章

243瀏覽量

23101

發布評論請先 登錄

NVMe協議簡要分析

NVMe控制器IP設計之接口轉換

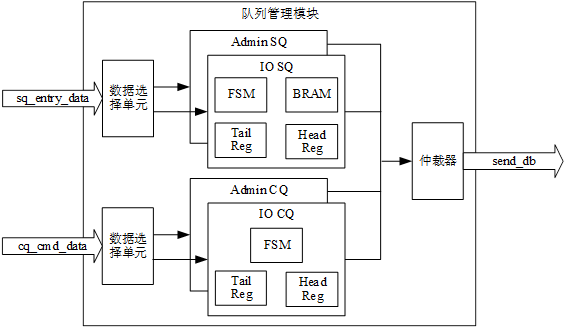

NVME控制器之隊列管理模塊

NVMe控制器之完成信息解析模塊

NVME控制器之隊列管理模塊

NVME控制器設計1

NVMe IP開發速成: 三個月不是夢

一文詳解 ALINX NVMe IP 特性

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

評論