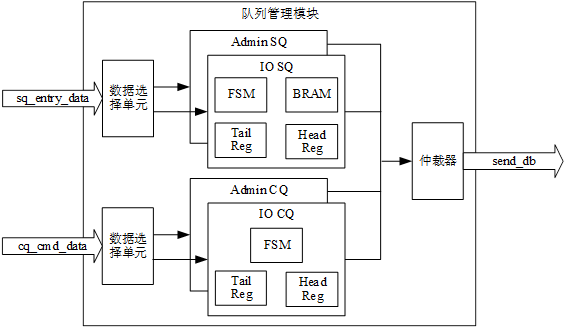

隊列管理模塊是整個NVMe Host控制器的核心模塊,該模塊實現(xiàn)了提交隊列與完成隊列的管理,多隊列請求的仲裁判決等功能。隊列管理模塊中含有數(shù)據(jù)選擇單元、SQ、CQ、和仲裁器等模塊。其中Admin SQ與IO SQ的內(nèi)部結(jié)構(gòu)一致,包含狀態(tài)機(jī)、BRAM、Tail REG和Head REG。Admin CQ與IO CQ的內(nèi)部結(jié)構(gòu)一致,包含狀態(tài)機(jī)、Tail REG和Head REG。

隊列管理模塊框圖如圖1所示。

圖1 隊列管理模塊框圖

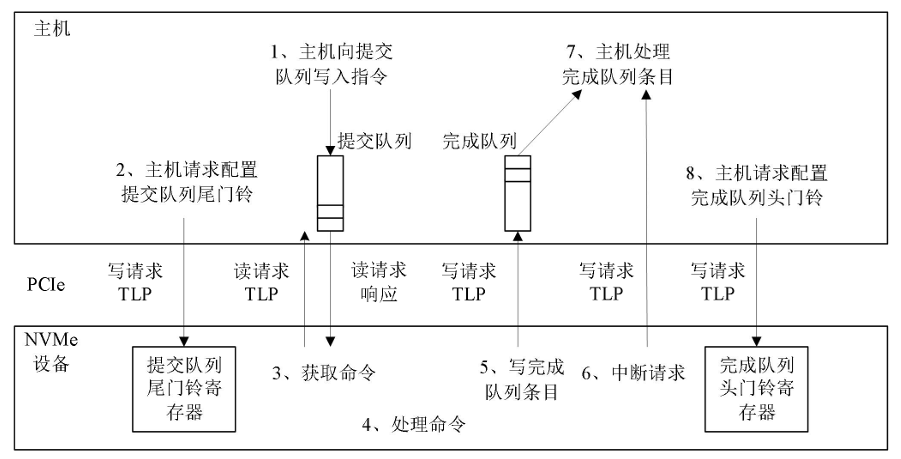

在NVMe協(xié)議中,使用隊列來傳輸、緩存和處理命令條目,以實現(xiàn)Host端和NVMe SSD端之間的通信。在CPU上運行NVMe軟件協(xié)議棧,其Host端生成提交命令的速度遠(yuǎn)大于NVMe SSD的執(zhí)行速度,同時由于CPU的指令是順序執(zhí)行的,需要通過中斷來通知CPU去處理完成信息。因此,通過增加提交隊列和完成隊列的深度可以提高系統(tǒng)的傳輸性能。

設(shè)計中可以利用FPGA的并行處理能力來加速NVMe Host端的控制流程。相較于軟件協(xié)議棧,通過硬件電路生成提交命令的速度更快,并且能夠通過并行操作去實時檢查返回的完成信息,從而避免了采用中斷來通知CPU去處理完成信息而造成延遲較大的問題。本設(shè)計主要針對順序讀寫場景進(jìn)行了資源方面的優(yōu)化。考慮到在順序讀寫情況下,傳輸性能與隊列深度的大小無關(guān),且硬件邏輯生成NVMe命令的速度要遠(yuǎn)大于軟件協(xié)議棧生成NVMe命令的速度,因此通過增加提交隊列和完成隊列的深度來提高系統(tǒng)的傳輸性能的方法不再可行,本設(shè)計將提交隊列深度設(shè)置為NVMe SSD一次突發(fā)讀取的數(shù)據(jù)量大小,這樣在保證性能的前提下,可以盡可能的減少資源的消耗。此外,取消了完成隊列緩存的設(shè)計,對完成信息的解析工作通過組合邏輯電路對其進(jìn)行實時檢測,而不用通過中斷來通知NVMe Host檢查,從而可以提高NVMe命令的執(zhí)行效率,并節(jié)省了大量的存儲資源。

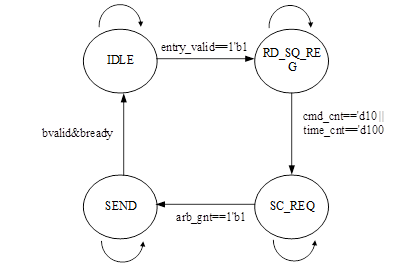

提交隊列內(nèi)部由一個雙端口RAM、兩個寄存器和一個狀態(tài)機(jī)構(gòu)成。其中,提交隊列分為Admin提交隊列和I/O提交隊列,分別用于管理Admin命令和I/O命令。雖然這兩個隊列針對的命令條目不同,但其內(nèi)部結(jié)構(gòu)相同。因此,通過采用相同的設(shè)計來實現(xiàn)兩個隊列,以提高代碼的復(fù)用性和可維護(hù)性。雙端口RAM使用BRAM資源實現(xiàn),包括兩個128位寬、深度可配置的端口,用于實現(xiàn)NVMe命令的緩存。四個控制寄存器用于監(jiān)測隊列狀態(tài),包括Head指針和Tail指針。Head指針指向隊列中下一個被執(zhí)行的命令的位置,Tail指針指向隊列中下一個空位置,新產(chǎn)生的命令條目總是被寫入Tail所指向的位置。當(dāng)同一個隊列的Head指針等于Tail指針加1時,表示隊列為滿;當(dāng)Head指針等于Tail指針時,表示隊列為空。該模塊中的狀態(tài)機(jī)用來實現(xiàn)門鈴寄存器信息更新的流程控制工作。隊列管理狀態(tài)機(jī)的跳轉(zhuǎn)圖如圖2所示。

圖2 隊列管理狀態(tài)機(jī)的跳轉(zhuǎn)圖

各狀態(tài)說明如下:

IDLE:空閑狀態(tài),該狀態(tài)為模塊上電后的初始化狀態(tài),該狀態(tài)下檢測到s_axis_entry_valid信號有效時,表示有提交命令傳輸至隊列管理模塊,狀態(tài)跳轉(zhuǎn)至RD_SQ_REG狀態(tài),否則維持當(dāng)前IDLE狀態(tài)。

RD_SQ_REG:讀提交隊列寄存器狀態(tài),該狀態(tài)下讀取提交隊列中的cmd_cnt寄存器,cmd_cnt寄存器負(fù)責(zé)記錄隊列中緩存的命令數(shù),即SQ Head指針與SQ Tail指針之差,當(dāng)cmd_cnt寄存器的值大于10時向仲裁器發(fā)起更新門鈴寄存器請求,這里設(shè)置為10主要是考慮到減少NVMe Host控制器和NVMe SSD之間的數(shù)據(jù)交互次數(shù),讓其通過突發(fā)傳輸一次讀取多條命令,來達(dá)到提升系統(tǒng)性能的效果,同時,為了解決長時間沒有接收到新的提交命令使得小于10條命令無法發(fā)送的情況,添加了超時機(jī)制,當(dāng)計時計數(shù)器達(dá)到一定值時,不再等待cmd_cnt滿足條件,直接跳轉(zhuǎn)至SC_REQ狀態(tài),否則維持當(dāng)前狀態(tài)。

SC_REQ:仲裁請求狀態(tài),該狀態(tài)下將sq_req信號置為高電平來向仲裁器發(fā)起仲裁請求,若接收到仲裁授權(quán),狀態(tài)跳轉(zhuǎn)至SEND狀態(tài),否則維持當(dāng)前狀態(tài)。

SEND:發(fā)送狀態(tài),該狀態(tài)下向接口轉(zhuǎn)換模塊發(fā)送當(dāng)前的隊列信息,接口轉(zhuǎn)換模塊將內(nèi)部信號轉(zhuǎn)換為AXI4接口信號,通過訪問PCIe的BAR空間來實現(xiàn)對NVMe SSD門鈴寄存器的更新,等待返回應(yīng)答信號,狀態(tài)跳轉(zhuǎn)至IDLE狀態(tài)。

相關(guān)視頻感興趣的,請移步B站,搜用戶名 專注與守望 或 內(nèi)容 NVMe IP

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1643文章

21941瀏覽量

613338 -

控制器

+關(guān)注

關(guān)注

114文章

16918瀏覽量

182657

發(fā)布評論請先 登錄

NVMe協(xié)議簡介2

NVMe控制器IP設(shè)計系列之接口轉(zhuǎn)換模塊

NVMe控制器IP設(shè)計之接口轉(zhuǎn)換

NVMe控制器之完成信息解析模塊

NVME控制器之指令控制模塊設(shè)計

NVME控制器設(shè)計之指令控制

NVMe控制器設(shè)計1

NVME控制器設(shè)計1

一文詳解 ALINX NVMe IP 特性

NVME控制器之隊列管理模塊

NVME控制器之隊列管理模塊

評論