芯片的先進(jìn)封裝是一種超越摩爾定律的重要技術(shù),它可以提供更好的兼容性和更高的連接密度,使得系統(tǒng)集成度的提高不再局限于同一顆芯片。

先進(jìn)封裝的優(yōu)勢主要體現(xiàn)在以下幾個方面:

優(yōu)化連接方式,實現(xiàn)更高密度的集成:通過改進(jìn)封裝技術(shù),可以實現(xiàn)更小、更密集的芯片連接,從而提高系統(tǒng)集成度。

更容易地實現(xiàn)異構(gòu)集成:先進(jìn)封裝可以在同一個封裝內(nèi)集成不同材料、線寬的半導(dǎo)體芯片和器件,從而充分利用不同種類芯片的性能優(yōu)勢以及成熟制程的成本優(yōu)勢。這種異構(gòu)集成可以大大提高系統(tǒng)的整體性能。

為芯片的功能拓展增加了可能性:傳統(tǒng)封裝技術(shù)本身對芯片的功能并不會產(chǎn)生實質(zhì)變化,而先進(jìn)封裝則可以通過集成不同的芯片和器件,為芯片的功能拓展提供更多的可能性。

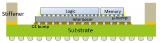

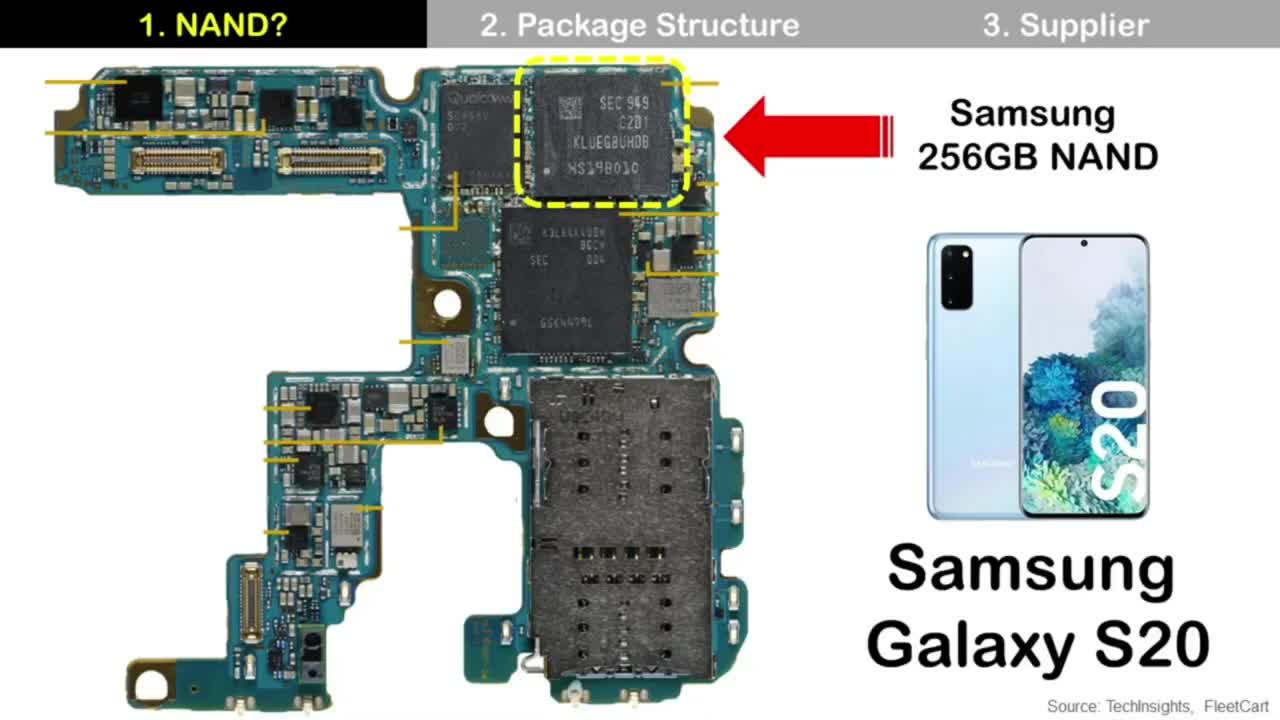

先進(jìn)封裝技術(shù)包括倒裝芯片(FlipChip)、晶圓級封裝(WLP)、2.5D封裝、3D封裝等。其中,倒裝芯片技術(shù)是一種將芯片有源區(qū)面對基板的封裝方式,通過芯片上呈陣列排列的焊料凸點實現(xiàn)芯片與基板的互聯(lián),具有封裝面積減小、引線互連長度縮短、引腳數(shù)量增加等優(yōu)點。晶圓級封裝技術(shù)則是一種在晶圓級別進(jìn)行封裝的技術(shù),可以提高生產(chǎn)效率和降低成本。

總的來說,先進(jìn)封裝技術(shù)是芯片制造領(lǐng)域的重要發(fā)展方向之一,它可以提高芯片的性能和可靠性,降低成本,為電子產(chǎn)品的進(jìn)一步發(fā)展提供支持。

倒裝芯片(FlipChip)

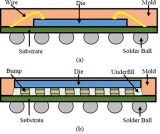

倒裝芯片(Flip Chip)也稱倒裝片,是一種無引腳結(jié)構(gòu),一般含有電路單元。其設(shè)計用于通過適當(dāng)數(shù)量的位于其面上的錫球(導(dǎo)電性粘合劑所覆蓋),在電氣上和機械上連接于電路。

具體來說,倒裝芯片是將集成電路(IC)芯片的有源區(qū)面對基板,通過芯片上呈陣列排列的焊料凸點實現(xiàn)芯片與基板的互聯(lián),芯片和基板之間的互聯(lián)僅靠焊料凸點來完成。這種技術(shù)可以大大減小封裝體積,實現(xiàn)輕、薄、短、小的封裝需求,同時可以有效改善芯片的電性能和熱性能。

倒裝芯片技術(shù)是當(dāng)前微電子封裝領(lǐng)域中最先進(jìn)的封裝技術(shù)之一,被廣泛應(yīng)用于各種高性能、小尺寸的電子產(chǎn)品中,如智能手機、平板電腦、可穿戴設(shè)備等。

晶圓級封裝(WLP)

晶圓級封裝(WLP,Wafer Level Packaging)是一種先進(jìn)的封裝技術(shù)。具體來說,這種技術(shù)涉及準(zhǔn)備預(yù)處理窗口晶圓和預(yù)處理電路晶圓,然后在中間載體的原子級光滑的表面上生長金屬層。它具有許多優(yōu)點,包括尺寸小、電性能優(yōu)良、散熱好、成本低等。

由于這些優(yōu)勢,晶圓級封裝近年來發(fā)展迅速,并被廣泛應(yīng)用于各種高性能、小尺寸的電子產(chǎn)品中

2.5D封裝

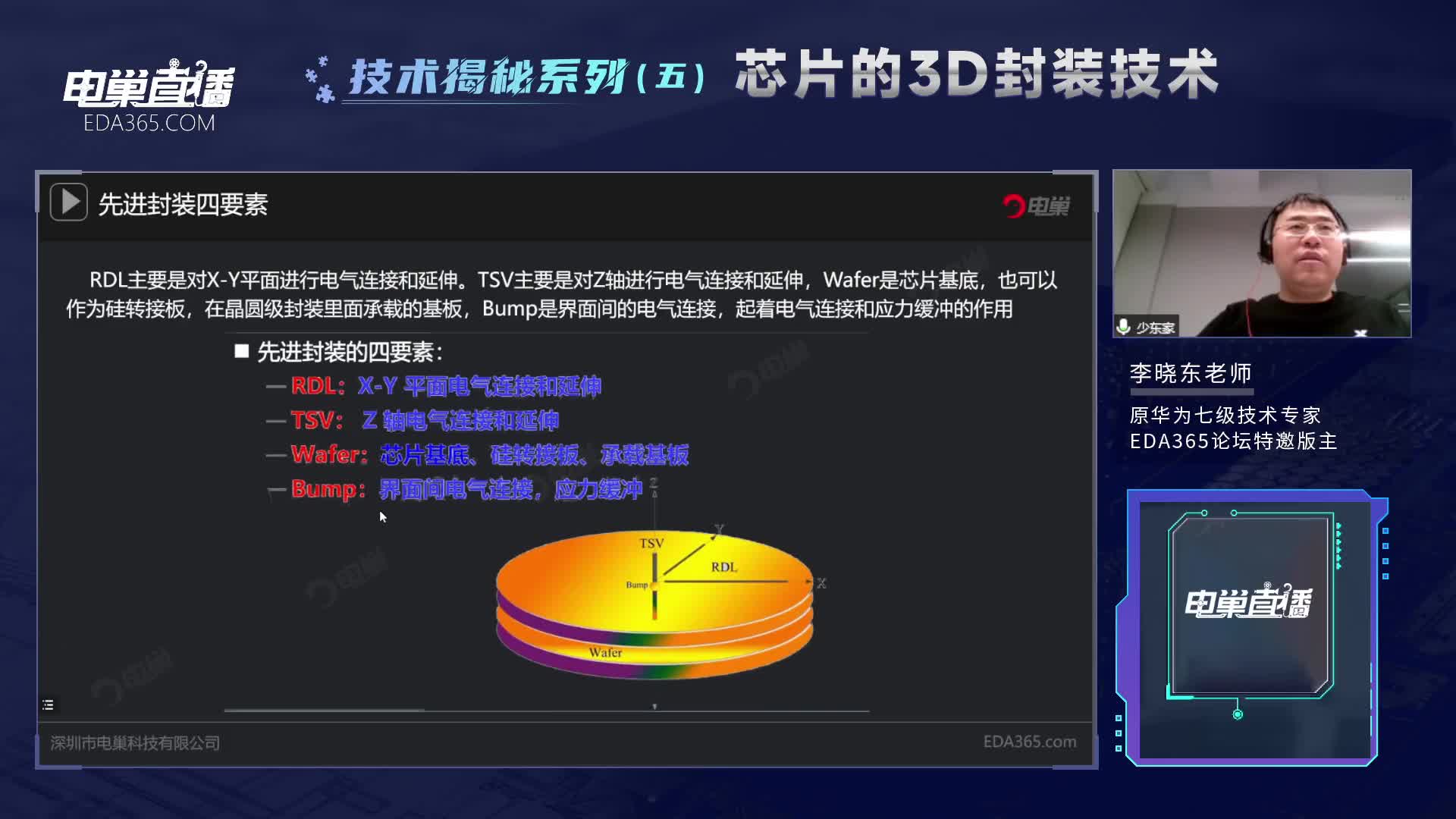

2.5D封裝是一種介于2D和3D之間的先進(jìn)封裝技術(shù)。在實現(xiàn)更精細(xì)的線路與空間利用方面,2.5D封裝展現(xiàn)出了顯著的優(yōu)勢。它將多個裸片堆疊或并排放置在具有硅通孔(TSV)的中介層頂部,并利用中介層提供芯片之間的互聯(lián)。

此外,2.5D封裝技術(shù)通常應(yīng)用于高端ASIC、FPGA、GPU和內(nèi)存立方體等領(lǐng)域。例如,賽靈思曾采用此技術(shù)將其大型FPGA劃分為四個良率更高的較小芯片,并將這些芯片連接到硅中介層,最終廣泛用于高帶寬內(nèi)存(HBM)處理器集成。

值得一提的是,2.5D封裝不僅有2D的特點,同時也具備部分3D的特點。其物理結(jié)構(gòu)表現(xiàn)為所有芯片和無源器件均位于XY平面上方,至少有部分芯片和無源器件安裝在中介層上。此外,中介層的布線和過孔位于XY平面的上方,而基板的布線和過孔則位于XY平面的下方。

3D封裝

3D封裝是一種先進(jìn)的封裝技術(shù),它在封裝過程中將芯片以立體方式堆疊,從而改變堆疊方式,縮短芯片之間的距離,加快芯片間的連接速度。這種技術(shù)被視為提升芯片性能的方法之一。

具體來說,3D封裝技術(shù)允許不同功能的芯片堆疊在一起,提高了芯片的整合度,減少了電路板上的空間占用,降低了系統(tǒng)的體積和重量。此外,由于芯片之間的距離縮短,信號傳輸?shù)难舆t也相應(yīng)減少,從而提高了系統(tǒng)的響應(yīng)速度和性能。

與2.5D封裝相比,3D封裝在Z軸方向上進(jìn)行堆疊,進(jìn)一步提高了封裝密度和性能。這種技術(shù)在高性能計算、人工智能、數(shù)據(jù)中心等領(lǐng)域具有廣泛的應(yīng)用前景。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

52151瀏覽量

436018 -

倒裝芯片

+關(guān)注

關(guān)注

1文章

102瀏覽量

16520 -

晶圓級封裝

+關(guān)注

關(guān)注

5文章

36瀏覽量

11631 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

460瀏覽量

501

原文標(biāo)題:芯片的先進(jìn)封裝

文章出處:【微信號:TenOne_TSMC,微信公眾號:芯片半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

盤點先進(jìn)封裝基本術(shù)語

超越芯片表面:探索先進(jìn)封裝技術(shù)的七大奧秘

HRP晶圓級先進(jìn)封裝替代傳統(tǒng)封裝技術(shù)研究(HRP晶圓級先進(jìn)封裝芯片)

芯片封裝引腳名稱自適應(yīng)顯示#芯片封裝#EDA #電子#電子工程師 #先進(jìn)封裝 #pcb設(shè)計

中美貿(mào)易戰(zhàn),國產(chǎn)芯片發(fā)展艱難,先進(jìn)封裝助力中國芯突圍!#芯片封裝 #先進(jìn)封裝 #華芯邦 #

傳統(tǒng)封裝你了解多少,小白快捷學(xué)習(xí) | 第1集 #傳統(tǒng)封裝 #先進(jìn)封裝 #芯片封裝 #華芯邦 #

中國芯片被美國“卡脖子”?先進(jìn)封裝Chiplet或許就是破局關(guān)鍵!#先進(jìn)封裝 #芯片封裝 #華芯邦 #

怎樣衡量一個芯片封裝技術(shù)是否先進(jìn)?

先進(jìn)封裝對比傳統(tǒng)封裝的優(yōu)勢及封裝方式

光芯片走向Chiplet,顛覆先進(jìn)封裝

何謂先進(jìn)封裝/Chiplet?先進(jìn)封裝/Chiplet的意義

倒裝芯片的優(yōu)勢_倒裝芯片的封裝形式

芯片先進(jìn)封裝的優(yōu)勢

芯片先進(jìn)封裝的優(yōu)勢

評論