在模塊劃分時(shí),我們通常會(huì)考慮解耦合,即盡量減少模塊間的交互,讓模塊間的接口盡量簡(jiǎn)單。

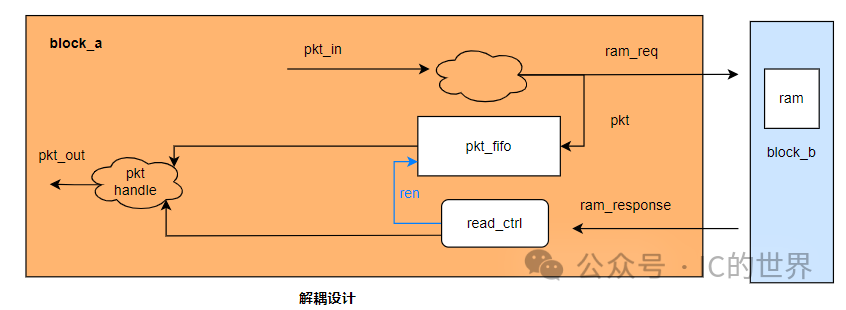

在包處理過(guò)程中,因?yàn)閿?shù)據(jù)處理的需求,需要讀取某些信息(配置信息,狀態(tài)信息),如圖中讀取block_b中的ram,根據(jù)讀返回的結(jié)果后對(duì)數(shù)據(jù)包進(jìn)行處理。

為了解耦合,我們可以采用一個(gè)fifo(pkt_fifo)存儲(chǔ)與ram請(qǐng)求(ram_req)無(wú)關(guān)的信息(數(shù)據(jù)包以及數(shù)據(jù)包的相關(guān)描述信息),等待response返回后,再?gòu)膒kt_fifo讀取相應(yīng)的數(shù)據(jù)包信息對(duì),從而對(duì)數(shù)據(jù)包進(jìn)行處理。

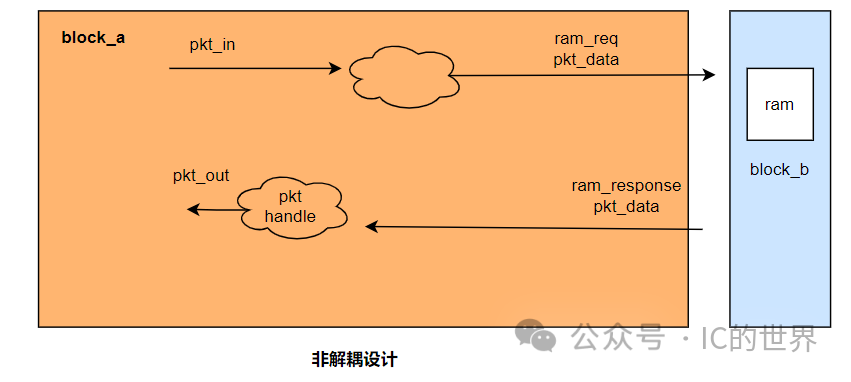

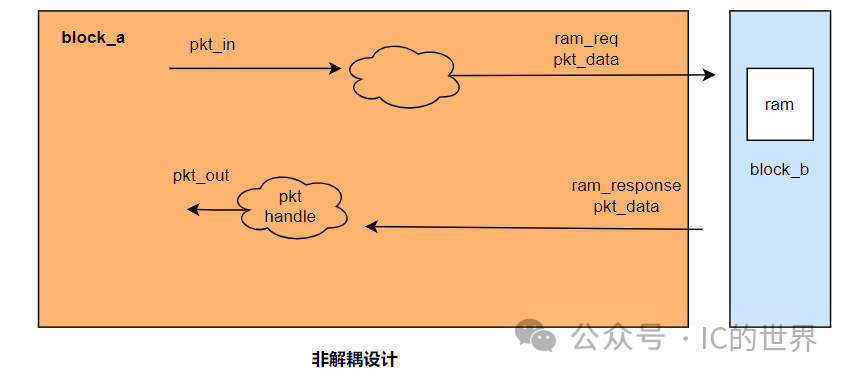

如果不采用pkt_fifo存儲(chǔ)包信息,那么會(huì)怎么設(shè)計(jì)呢?如非解耦設(shè)計(jì)圖所示,不需要額外的fifo,將包信息(pkt_data)與訪問(wèn)請(qǐng)求(ram_req)一同傳遞給block_b模塊,再由block_b將包信息(pkt_data)和訪問(wèn)響應(yīng)(ram_response)一同送到block_a模塊。

案例中的解耦合設(shè)計(jì)還有一個(gè)優(yōu)點(diǎn):節(jié)約資源和功耗。如果從發(fā)起ram_req到返回ram_reponse的流水比較長(zhǎng),例如需要幾十甚至上百個(gè)時(shí)鐘周期,在非解耦設(shè)計(jì)中,就需要使用寄存器對(duì)pkt_data進(jìn)行打拍,而解耦設(shè)計(jì)中采用fifo存儲(chǔ)pkt_data,雖然從存儲(chǔ)bit角度計(jì)算兩種設(shè)計(jì)需要的bit位幾乎相同,但是fifo(用ram實(shí)現(xiàn))面積更小,功耗更低。

? ? ?

? ? ?

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5423瀏覽量

123431 -

RAM

+關(guān)注

關(guān)注

8文章

1391瀏覽量

116839 -

FIFO存儲(chǔ)

+關(guān)注

關(guān)注

0文章

103瀏覽量

6148

原文標(biāo)題:IC設(shè)計(jì):ram的應(yīng)用 - 一種常見(jiàn)的解耦設(shè)計(jì)

文章出處:【微信號(hào):IP與SoC設(shè)計(jì),微信公眾號(hào):IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

怎樣去搭建一種永磁同步電機(jī)的數(shù)學(xué)模型

一種基于滑模觀測(cè)器的電流偏差解耦控制方法

常用的解耦設(shè)計(jì)方法

分享一種基于大RAM的系統(tǒng)設(shè)計(jì)IoT RAM

一種基于PID神經(jīng)網(wǎng)絡(luò)的解耦控制方法的研究

一種新的PI調(diào)節(jié)器在交流解耦控制系統(tǒng)中的應(yīng)用

基于補(bǔ)償器的解耦控制方法的研究

先進(jìn)PID多變量解耦控制

電容解耦如何放置

永磁同步電機(jī)控制之反饋解耦及復(fù)矢量解耦

RAM的應(yīng)用-一種常見(jiàn)的解耦設(shè)計(jì)

RAM的應(yīng)用-一種常見(jiàn)的解耦設(shè)計(jì)

評(píng)論