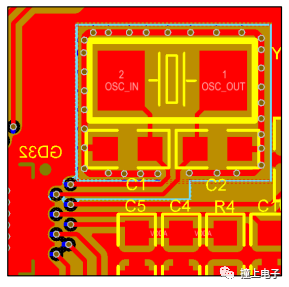

一,晶振

晶體要盡量靠近芯片Pin,遠離諸如功率電感的磁感應器件與諸如天線的輻射器件,與同層其他信號走線利用GND鋪銅及VIA隔離。晶體輸入輸出走線要盡可能短且少彎折,不可跨層或交叉走線。兩邊負載電容與晶體各自的GND和PAD可以相連,并擺放多個GND和VIA以提高散熱保障。晶體下方盡量不走任何傳輸線,保留完整的GND鋪銅。晶振電路走線以及匹配電容應該與晶振在同一側,盡量不穿層。布局應該使晶振靠近MCU,晶振電路走線不能太長,不要超過12mm。在晶振同層以及下一層與其他電路間隔開,晶振電路周圍也使用接地 VIA 形成保護環。

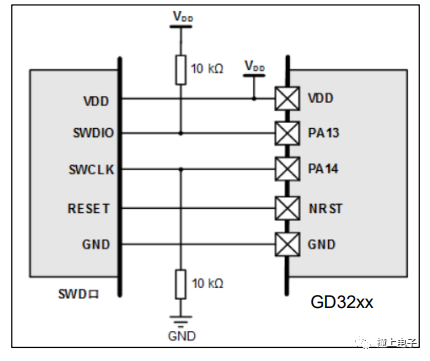

二,下載口

MCU的 SWD 燒錄口走線應盡量短,遠離板邊 12mm。有以下幾種方式可以提高SWD下載調試通信的可靠性,增強下載調試的抗干擾能力。縮 短SWD兩個信號線長度,最好15cm以內;將SWD兩根線和GND線編個麻花,纏在一 起;在SWD兩根信號線對地各并幾十pF小電容;SWD兩根信號線任意IO串入100Ω~1KΩ 電阻。

三,復位電路

-

芯片

+關注

關注

459文章

52205瀏覽量

436453 -

mcu

+關注

關注

146文章

17851瀏覽量

360684 -

敏感電路

+關注

關注

0文章

19瀏覽量

7674

發布評論請先 登錄

ADS1294 RLD相關的外圍電路設計和每個引腳代表的意義?

內卷下,MCU廠商面對的機遇有哪些?

靜電對敏感電子元件的影響

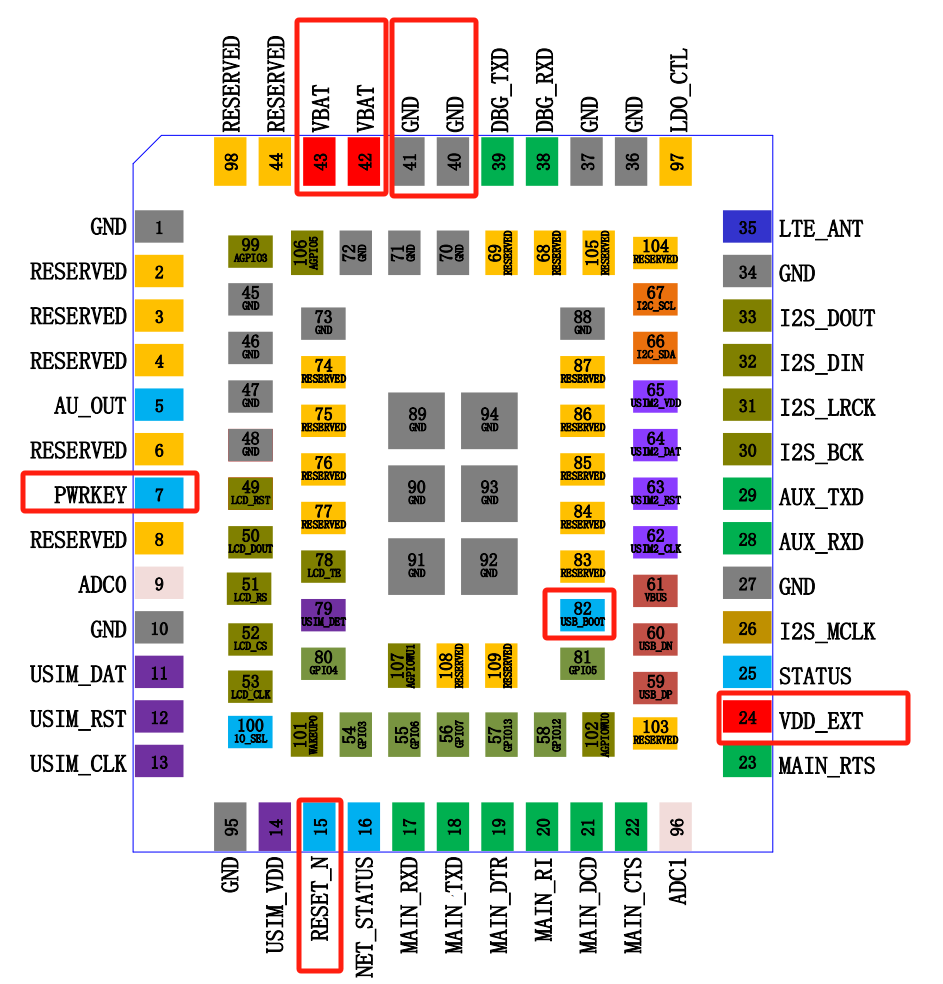

硬件設計很簡單?低功耗4G模組Air780E—開機啟動及外圍電路設計

硬件設計很簡單?合宙低功耗4G模組Air780E—開機啟動及外圍電路設計

32位單片機的電路設計技巧分享!

單片機方案開發-分享七個常用的外圍電路設計

PFC電路電感電流震蕩的原因

CAN總線節點數計算與外圍電路參考設計

MCU廠商推薦的外圍敏感電路設計

MCU廠商推薦的外圍敏感電路設計

評論