前幾天看到有人討論如何實現分頻時鐘÷2,÷4,÷8,÷16之間的切換。

其實這個分頻時鐘切換很簡單,根本不需要額外的切換電路。一個共用的計數器,加一點控制邏輯,就可以了,而且可以實現2到16任意整數分頻率之間的無縫切換。

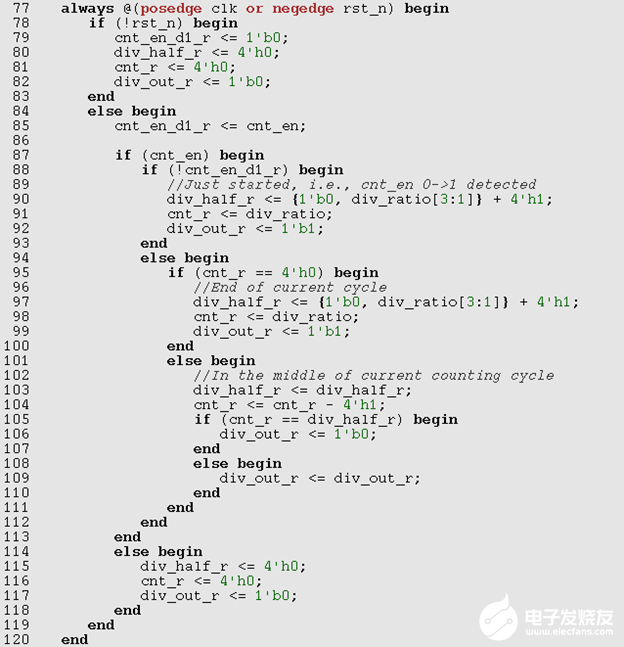

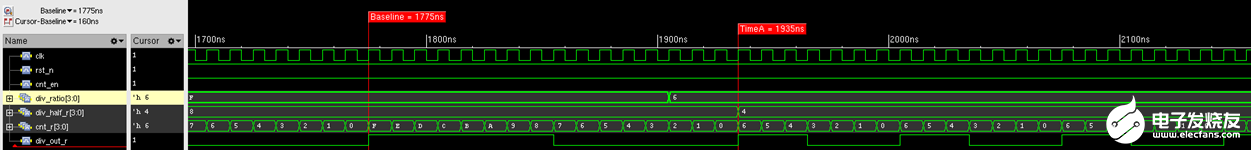

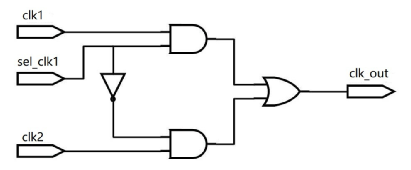

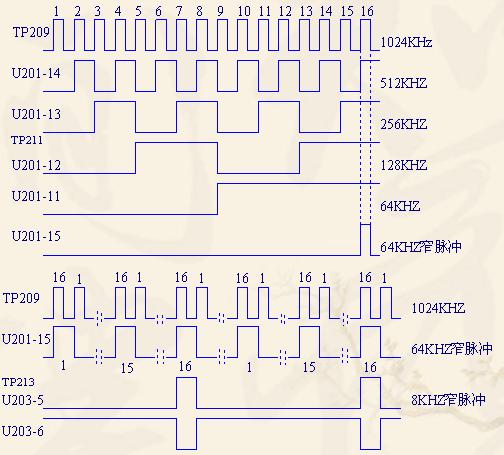

RTL示意如下。這里的關鍵是要等當前周期跑到最后才切換到新的分頻率。這樣才能保障輸出總是一個完整的周期,不會出現不規則的周期。

這里沒有加奇數分頻占空比調整。如果希望奇數分頻后占空比是50-50,要再加一個negedge DFF,再加一個OR,很簡單的,就不贅述了。

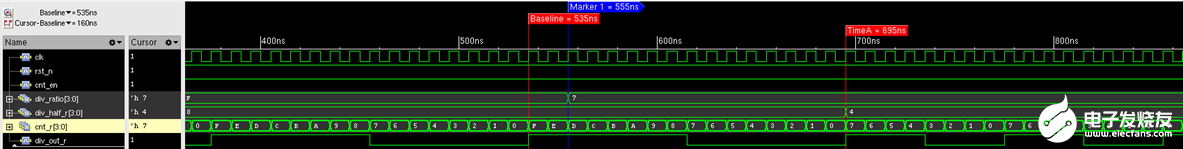

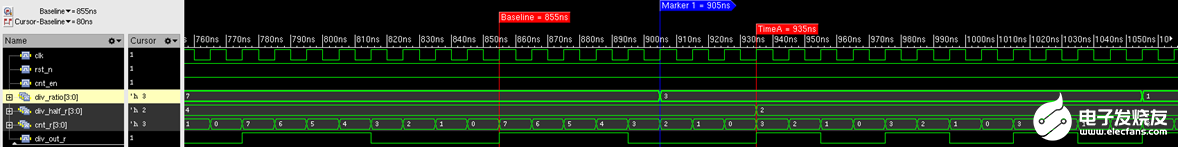

Divide 16 to divide 8

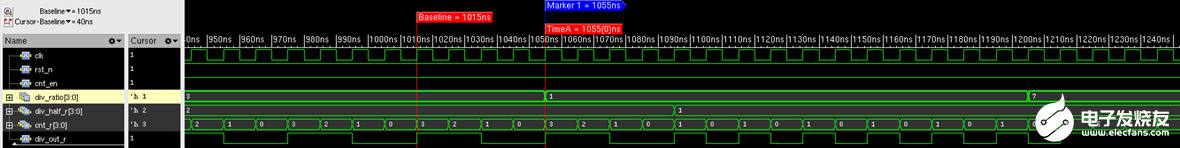

Divide 8 to divide 4

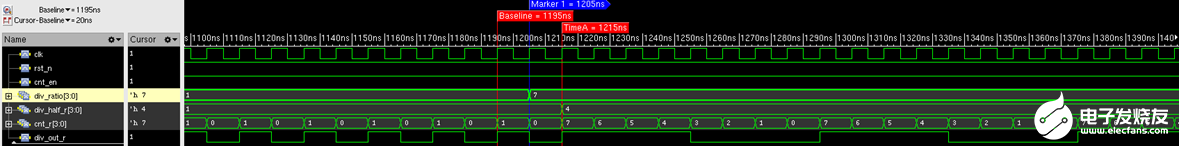

Divide 4 to divide 2

Divide 2 to divide 8

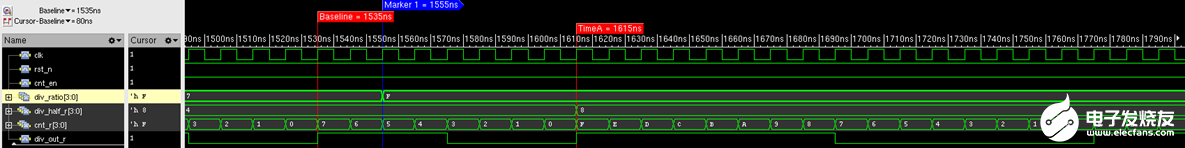

Divide 8 to divide 16

Divide 16 to divide 7

審核編輯:黃飛

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

計數器

+關注

關注

32文章

2284瀏覽量

96006 -

時鐘設計

+關注

關注

0文章

27瀏覽量

11003 -

控制邏輯

+關注

關注

0文章

14瀏覽量

2443

發布評論請先 登錄

相關推薦

熱點推薦

SPARTAN 3E上的時鐘分頻怎么實現?

你好,我需要在SPARTAN 3E上實現運行時,用戶可切換的時鐘分頻。它適用于用戶可以在VGA(25MHz像素時鐘)或SVGA(50MHz)

發表于 06-20 11:56

時鐘切換模式是如何工作的?

嗨,伙計,我使用PIC18F97 J94。目前,我的問題是動態切換時鐘(振蕩器)。我在切換前的設置是:OSCCONbits.COSC0=1;//快速RC振蕩器(FRC)除以N個

發表于 11-01 07:49

基于FPGA的高頻時鐘的分頻和分配設計

摘要:介紹了為PET(正電子發射斷層掃描儀)的前端電子學模塊提供時間基準而設計的一種新型高頻時鐘扇出電路。該電路利用FPGA芯片來實現對高頻時鐘的分頻

發表于 06-20 12:41

?1427次閱讀

如何理解STM32系統時鐘和分頻

STM32中有一個全速功能的USB模塊,其串行接口引擎需要一個頻率為48MHz的時鐘源。該時鐘源只能從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,

發表于 11-30 09:14

?7386次閱讀

verilog的時鐘分頻與時鐘使能

時鐘使能電路是同步設計的基本電路,在很多設計中,雖然內部不同模塊的處理速度不同,但由于這些時鐘是同源的,可以將它們轉化為單一時鐘處理;在ASIC中可以通過STA約束讓分頻始終和源

時鐘切換電路設計方案

隨著各種應用場景的限制,芯片在運行時往往需要在不同的應用下切換不同的時鐘源,例如低功耗和高性能模式就分別需要低頻率和高頻率的時鐘。兩個時鐘源有可能是同源且頻率比呈倍數關系,也有可能是不

如何實現分頻時鐘的切換

如何實現分頻時鐘的切換

評論