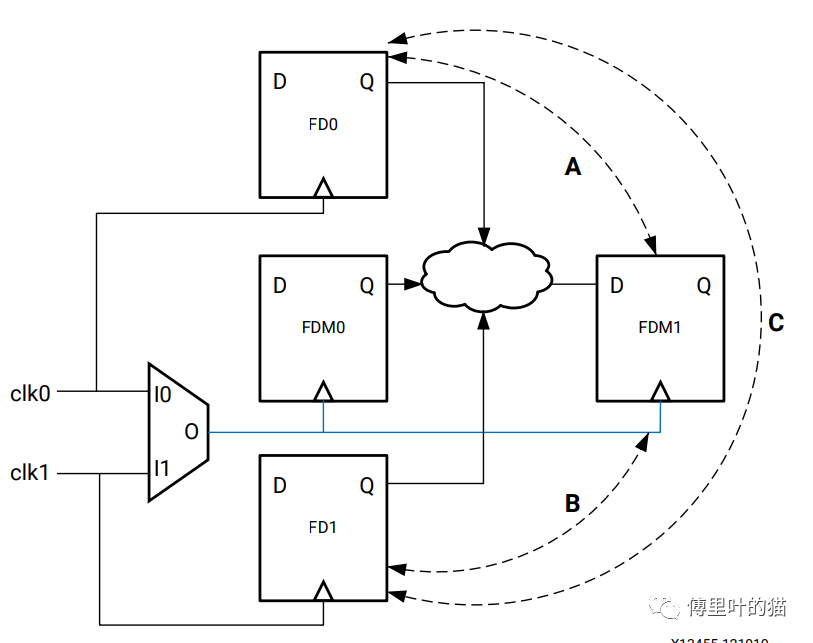

時序場景如下圖所示,clk0和clk1兩個時鐘輸入,經(jīng)過BUFGMUX后,輸出到后面的邏輯,但同時clk0和clk1還分別驅(qū)動了其他邏輯。

此時,如果路徑A/B/C都不存在,其中A路徑表示clk0與選擇器輸出的時鐘之間的數(shù)據(jù)交互,B路徑表示clk1與選擇器輸出的時鐘之間的數(shù)據(jù)交互,C路徑表示clk0和clk1之間的數(shù)據(jù)交互,那么使用下面的約束就可以了:

set_clock_groups-logically_exclusive-groupclk0-groupclk1

如果路徑 A、B 或 C 僅有一個存在,那么 clk0 和/或 clk1 與多路復(fù)用時鐘直接交互。

則需要使用下面的約束:

create_generated_clock-nameclk0mux-divide_by1 -source[get_pinsmux/I0][get_pinsmux/O] create_generated_clock-nameclk1mux-divide_by1 -add-master_clockclk1 -source[get_pinsmux/I1][get_pinsmux/O] set_clock_groups-physically_exclusive-groupclk0mux-groupclk1mu

logically_exclusive和physically_exclusive的區(qū)別在于:

-logical_exclusive

logical_exclusiveisusedfortwoclocksthataredefinedondifferentsourceroots. Logicallyexclusiveclocksdonothaveanyfunctionalpathsbetweenthem,butmighthavecouplinginteractionswitheachother. Anexampleoflogicallyexclusiveclocksismultipleclocks,whichareselectedbyaMUXbutcanstillinteractthroughcouplingupstreamoftheMUXcell. Whentherearephysicallyexistingbutlogicallyfalsepathsbetweenthetwoclocks,use"set_clock_groups-logical_exclusive".

-physical_exclusive

physical_exclusiveisusedfortwoclocksthataredefinedonthesamesourcerootby"create_clock-add". Timingpathsbetweenthesetwoclocksdonotphysicallyexist. Asaresultyouwillneedtouse"set_clock_groups-physical_exclusive"tosetthemasfalsepaths.

簡而言之,logical_exclusive用于選擇器的電路,兩個時鐘的source不一樣;而physical_exclusive兩個時鐘的source是一樣,比如在同一個時鐘輸入口,但可能會輸入兩個不同的時鐘。

再回到最上面的問題,如果路徑A、B和C有一條存在,說明時鐘之間有交互,就不能簡單的使用logical_exclusive,而是要為這兩個時鐘都創(chuàng)建一個衍生時鐘,但這兩個衍生時鐘屬于physical_exclusive。

審核編輯:劉清

-

時鐘

+關(guān)注

關(guān)注

11文章

1879瀏覽量

132834 -

選擇器

+關(guān)注

關(guān)注

0文章

109瀏覽量

14759 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17519

原文標(biāo)題:經(jīng)過BUFGMUX的時鐘該如何約束

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

FPGA時序約束之衍生時鐘約束和時鐘分組約束

源同步的約束該怎么加?

FPGA時鐘約束問題

BUFGMUX出現(xiàn)錯誤:地點:1108幫助/原因?

BUFGMUX定時時鐘偏差太大

為什么使用并發(fā)賦值語句而不是BUFGMUX原語?

詳解數(shù)字設(shè)計中的時鐘與約束

經(jīng)過BUFGMUX的時鐘該如何約束

時序約束一主時鐘與生成時鐘

FPGA時序約束之設(shè)置時鐘組

經(jīng)過BUFGMUX的時鐘該如何約束呢?

經(jīng)過BUFGMUX的時鐘該如何約束呢?

評論