由于芯片的集成度和性能越來越高,傳統的封裝技術已經無法滿足新一代芯片的封裝要求,而3D Cu-Cu混合鍵合技術提供了一種高密度、低成本、高性能的方案,有助于提高封裝的可靠性和穩定性,實現高速、低延遲的芯片互連。

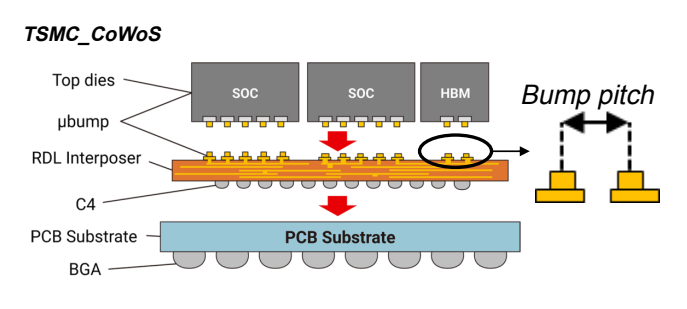

凸點間距與先進半導體封裝

1965年發明了第一個半導體封裝,此后封裝技術不斷發展。現在,有許多封裝技術,從最廣泛使用的引線鍵合到最先進的3DIC。之所以叫先進半導體封裝,一種分類方法是看凸點間距的大小。較小的凸點間距意味著更多的I/O數,即更高的互連密度,這是許多高計算應用所必需的。通常,我們將先進半導體封裝定義為凸點間距小于100μm的任何封裝。

凸點間距

I/O數是隨著凸點間距的減小而增加的,例如:10μm凸點間距封裝技術可以提供大約400倍于200μm凸點間距封裝技術的I/O數。

Cu-Cu混合鍵合的典型應用

Cu-Cu混合鍵合技術可以提高封裝的可靠性和穩定性。在傳統的封裝技術中,芯片與基板之間的連接通常采用引線或載帶等方式,這些連接方式容易受機械振動、溫度變化等因素的影響,導致連接失效或損壞。而Cu-Cu混合鍵合的連接具有更高的強度和穩定性,可有效地提高封裝的可靠性和穩定性。

此外,Cu-Cu混合鍵合技術的制造工藝相對簡單,可實現晶圓級大規模生產,從而降低成本并提高效率。該技術可應用于不同類型的芯片和基板材料,具有廣泛的適用性,特別是在高密度、高性能的封裝中具有顯著優勢。Cu-Cu混合鍵合的典型應用包括:

倒裝芯片封裝(FC):在倒裝芯片封裝中,通過Cu-Cu混合鍵合實現芯片的凸點與基板的相應觸點互連。這種封裝方式具有高密度、高性能的特點,廣泛應用于高性能計算、通信、軍事等領域。

3D封裝:在芯片堆疊封裝中,通過Cu-Cu混合鍵合實現芯片之間的互連,將多個芯片堆疊在一起,從而在有限的空間內增加更多的功能和性能。這種封裝方式在智能手機、平板電腦等便攜式設備中應用很廣。

晶圓級封裝:將整個晶圓封裝在一起,通過Cu-Cu混合鍵合實現芯片之間的互連。這種封裝方式具有高密度、低成本、小型化的特點,廣泛應用于各種高性能集成電路。

傳統凸點工藝難以縮小間距

在傳統的倒裝芯片焊接工藝中,凸點間距被限制在40μm-50μm,無鉛焊料和Cu在230℃左右熔化后可形成穩定的接點,接點間需要底部填充物來提高其機械性能。不過,熱膨脹失配可能導致翹曲和管芯移位等可靠性問題。

當凸點間距減小到大約10μm時,焊球尺寸的減小增加了形成金屬間化合物(IMC)的風險,降低了IMC點的導電值和機械性能。此外,如果凸點間距太小,相鄰的焊球可能會接觸到,在回流焊過程中出現橋接現象導致芯片故障。而焊料和IMC的電阻率大約是Cu的十倍,不適合高性能組件封裝。

另外,隨著焊料凸點間距的縮小,用于接合的凸點高度和表面積的減小使得建立可靠的電連接變得越來越困難,需要精確的制造工藝來避免誤差。為此,關鍵的共面性和表面粗糙度變得至關重要,因為即使是微小的不規則性也會影響鍵合的成功。

由于采用較小的Cu柱和凸點直徑,制造中面臨蝕刻困難等障礙,更有可能發生過腐蝕(undercutting)。另外,由于有效確保均勻性和控制共面性變得更加困難,電化學沉積(ECD)鍍層的復雜性也會增加。而且,隨著凸點尺寸的不斷縮小,鍵合質量對凸點共面性、表面粗糙度和硬度等因素的敏感性使其對溫度、時間和壓力等參數的調整變得更加復雜。

為了解決倒裝焊的局限性難題,行業提出了Cu-Cu混合鍵合技術。該技術是在介電材料之間嵌入金屬觸點,并使用熱處理使Cu原子固態擴散將材料連接在一起,消除了焊接時遇到的橋接問題。Cu工藝是半導體行業中公認的技術,可以實現小于1μm的凸點間距。

與倒裝焊相比,混合焊的優點顯而易見。首先,它實現了超細間距和小接點尺寸,有助于實現高I/O數。因為器件需要越來越多的連接來滿足性能要求,這對現代半導體封裝至關重要;其次,與通常依賴于底部填充材料的倒裝焊不同,Cu-Cu混合鍵合無需進行底部填充,降低了寄生電容、電阻和電感及熱阻;最后,Cu-Cu混合鍵合中減小了連接厚度,幾乎消除了倒裝芯片技術中10-30μm厚度的焊球,為更緊湊、更高效的半導體封裝開辟了新的可能性。

Cu-Cu混合鍵合面臨的挑戰

Cu-Cu混合鍵合技術為先進半導體封裝帶來了巨大的前景,但它也帶來了一系列挑戰,需要有針對未來發展的創新解決方案。

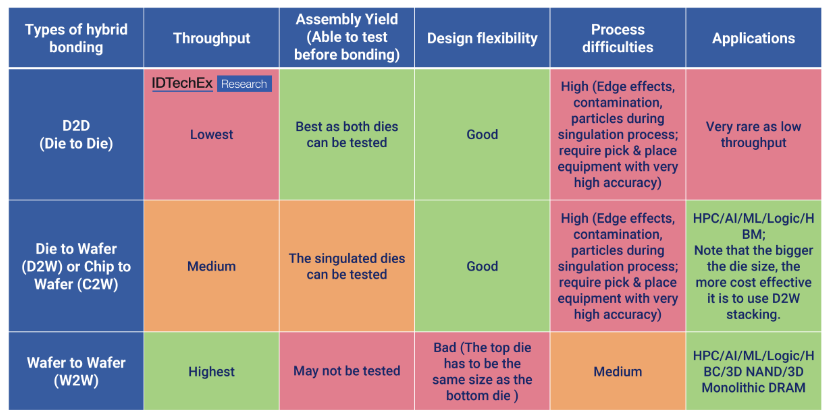

目前有三種Cu-Cu混合鍵合方式:晶圓對晶圓(W2W)工藝是最常用的工藝;管芯對晶圓(D2W)或芯片對晶圓(C2W)工藝正處于密集研發中,因為這兩種方法可以滿足更多需要集成不同尺寸管芯的應用。

Cu-Cu混合鍵合的三種方法和應用

對于這三種方式,制造中的一個關鍵是鍵合環境,通過化學機械拋光(CMP)優化實現平坦清潔的介電表面至關重要。此外,介電材料能夠承受較低退火溫度和較短持續時間,對于最大限度地減少鍵合過程中晶圓變形和翹曲的可能性也很重要。Cu解決方案的優化電化學沉積(ECD)還可以減少退火時間并降低退火溫度,從而提高效率。

在D2W/C2W工藝的情況下,重要的是解決與劃片(die singulation)和邊緣效應相關的挑戰,并最大限度地減少對管芯和晶圓的污染。高精度貼片機對于確保精確的管芯放置非常必要,可以將誤差縮小到0.2μm。為了適應可能的放置誤差,必須有更大的Cu焊盤。此外,先進的薄晶圓處理技術將在確保成功實現Cu-Cu混合鍵合方面發揮重要作用。

Cu-Cu混合鍵合的步驟

Cu-Cu混合鍵合的實現需要經過幾個步驟。首先,按照芯片大小將晶圓分割成單一的晶粒,以用于隨后的芯片貼裝、引線鍵合等工序。第二步是表面處理,使用化學等手段對晶圓表面進行清潔、去氧化層等處理,以去除表面的污染物和氧化層,提高鍵合質量。然后對晶圓表面進行研磨拋光,以去除表面的粗糙度和缺陷,提高表面平整度和鍵合可靠性。切割和研磨拋光操作需要精確控制,以確保晶圓的尺寸和厚度符合要求。

前期處理是Cu-Cu混合鍵合的重要步驟之一,其目的是為了確保晶圓的表面狀態和尺寸精度符合要求,以提高鍵合質量和可靠性。

在進行鍵合準備時,需要進行預熱和壓力調節。首先將芯片和基板分別放置在預熱爐中進行預熱,以達到適宜的鍵合溫度。預熱溫度的選擇應根據芯片和基板材料的特性合理調整;同時還需要調整鍵合機壓力,使其能夠正確施加在芯片和基板之間,以確保鍵合的牢固性和穩定性。

在鍵合操作過程中,需要嚴格控制鍵合溫度、壓力和時間等參數,以確保鍵合的質量和可靠性。

總之,Cu-Cu混合鍵合作為一種先進的芯片連接技術,在微電子封裝領域具有廣泛的應用前景。Cu-Cu混合鍵合的未來發展可能將集中在精煉和優化工藝方面,包括CMP、介電材料、ECD(電化學沉積)解決方案、貼片機的進步,以及處理薄晶圓的創新。克服這些挑戰將為在先進半導體封裝中更廣泛地采用Cu-Cu混合鍵合鋪平道路,從而能夠制造出更小、功能更強大、更節能的電子器件。

-

晶圓

+關注

關注

52文章

5111瀏覽量

129133 -

封裝

+關注

關注

128文章

8459瀏覽量

144720 -

先進半導體

+關注

關注

0文章

14瀏覽量

2293

原文標題:化解先進半導體封裝挑戰,有一個工藝不能不說

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

芯和半導體將參加重慶半導體制造與先進封測產業發展論壇

TLV320AIC3106音頻芯片采樣數據或者DA轉換時能不能不需要CPU的參與?

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

齊力半導體先進封裝項目一期工廠啟用

芯和半導體將參加2024集成電路特色工藝與先進封裝測試產業技術論壇

人工智能半導體及先進封裝技術發展趨勢

化解先進半導體封裝挑戰,有一個工藝不能不說

化解先進半導體封裝挑戰,有一個工藝不能不說

評論