嵌入式硬件專家瑞薩電子宣布推出首款基于免費(fèi)開放的 RISC-V 指令集架構(gòu) (ISA) 的完全自主研發(fā)的處理器內(nèi)核。

眾所周知,在過去,該公司已經(jīng)推出了采用晶心科技RISC-V內(nèi)核的產(chǎn)品,如32位語音控制ASSP、電機(jī)控制ASSP和64位通用微處理器“RZ/Five”,但它還沒有利用通過這項(xiàng)技術(shù),該公司計劃提高其在 RISC-V 市場的地位。

瑞薩電子的 Giancarlo Parodi 在談到該技術(shù)時表示:“RISC-V ISA 在半導(dǎo)體行業(yè)中的日益普及是創(chuàng)新的福音。它為設(shè)計人員提供了前所未有的靈活性,并將緩慢而穩(wěn)定地挑戰(zhàn)和改變嵌入式系統(tǒng)的當(dāng)前格局。”該公司最新的微控制器的背后。“過去,瑞薩電子已經(jīng)采用了 RISC-V 技術(shù),引入了基于 Andes Technology Corp 開發(fā)的 CPU 內(nèi)核構(gòu)建的用于語音控制和電機(jī)控制的 32 位 ASSP 器件。令人興奮的下一步是[我們的]首款內(nèi)置 -內(nèi)部設(shè)計的 CPU 核心。

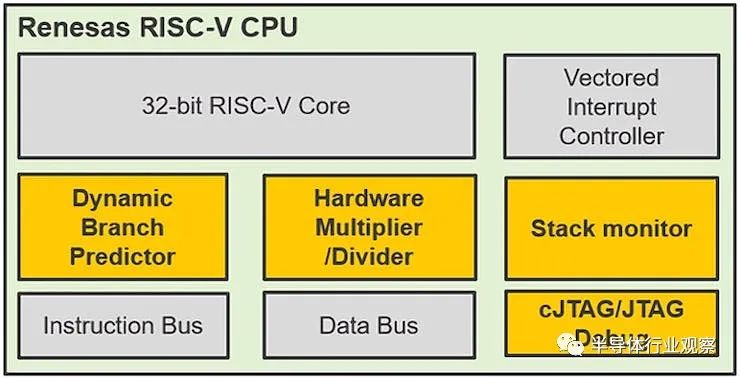

雖然瑞薩電子尚未透露將使用其內(nèi)部核心的部件的完整產(chǎn)品細(xì)節(jié),但它已經(jīng)確認(rèn)了有關(guān)核心本身的一些技術(shù)細(xì)節(jié)。框圖顯示了單個 32 位 RISC-V 內(nèi)核,具有性能提升的動態(tài)分支預(yù)測器、硬件乘法器/除法器、向量中斷控制器、堆棧監(jiān)視器寄存器、獨(dú)立的指令和數(shù)據(jù)總線以及緊湊型 JTAG (cJTAG)/ JTAG 調(diào)試功能。它還承諾 3.27 CoreMark/MHz)的性能水平——盡管時鐘速度尚不清楚。

“該 CPU 適用于許多不同的應(yīng)用環(huán)境。它可以用作主 CPU 或管理片上子系統(tǒng),甚至嵌入到專門的 ASSP [特定應(yīng)用標(biāo)準(zhǔn)產(chǎn)品] 設(shè)備中,”Parodi 聲稱。“顯然它非常靈活。其次,在硅片面積方面,該實(shí)施非常高效,除了對成本影響較小的明顯效果之外,還有助于降低待機(jī)期間的工作電流和漏電流。第三,盡管針對小型嵌入式系統(tǒng),但它提供了令人驚訝的高水平計算吞吐量,甚至可以滿足深度嵌入式應(yīng)用日益苛刻的性能要求。”

該核心利用免費(fèi)開放的 RISC-V 指令集架構(gòu)及其多個擴(kuò)展:Parodi 表示,該核心實(shí)現(xiàn)了帶有乘法 (M)、原子訪問 (A)、壓縮指令 (C) 的 RV32I 或 RV32E ISA ,以及位操作 (B) 擴(kuò)展。Parodi 聲稱:“這就是 RISC-V ISA 概念的美妙之處,它是從頭開始構(gòu)建的,允許設(shè)計人員根據(jù)目標(biāo)用例選擇要包含在處理器中的元素,并最終優(yōu)化由此產(chǎn)生的功耗、性能和芯片占用空間之間的權(quán)衡。”

瑞薩電子表示,目前正在向“精選客戶”提供帶有新內(nèi)核的芯片樣品,首批商用芯片將于明年第一季度推出。

RISC-V 的核心:新視野

RISC-V ISA 在半導(dǎo)體行業(yè)中的日益普及是創(chuàng)新的福音。它為設(shè)計人員提供了前所未有的靈活性,并將緩慢而穩(wěn)定地挑戰(zhàn)和改變嵌入式系統(tǒng)的當(dāng)前格局。過去,瑞薩電子曾采用 RISC-V 技術(shù),推出基于晶心科技開發(fā)的 CPU 內(nèi)核的 32 位 ASSP 設(shè)備,用于語音控制和電機(jī)控制。

令人興奮的下一步是第一個內(nèi)部設(shè)計的 CPU 內(nèi)核的推出。CPU 的高級框圖如下所示:

但它有什么特別之處呢?首先,該CPU適用于許多不同的應(yīng)用環(huán)境。它可以用作主 CPU 或管理片上子系統(tǒng),甚至嵌入到專用 ASSP 設(shè)備中。顯然它非常靈活。其次,該實(shí)施方案在硅面積方面非常高效,除了成本影響較小的明顯效果外,還有助于降低待機(jī)期間的工作電流和漏電流。第三,盡管它針對的是小型嵌入式系統(tǒng),但它提供了令人驚訝的高水平計算吞吐量,甚至可以滿足深度嵌入式應(yīng)用日益苛刻的性能要求。

在此基礎(chǔ)上,實(shí)施者可以在 RV32“I”或“E”選項(xiàng)之間進(jìn)行選擇,以優(yōu)化通用寄存器的可用數(shù)量。例如,在小型子系統(tǒng)不需要處理復(fù)雜的堆棧和應(yīng)用程序但專用于服務(wù)特定外圍設(shè)備或執(zhí)行內(nèi)務(wù)任務(wù)的情況下。

RISC-V ISA 還預(yù)見了幾種“擴(kuò)展”,它們以比使用標(biāo)準(zhǔn)強(qiáng)制 ISA 更好或更有效的方式實(shí)現(xiàn)特定功能。瑞薩電子選擇整合其中的幾個:

M擴(kuò)展–加速并優(yōu)化乘法(和除法)運(yùn)算,利用硬件乘法器和除法器單元實(shí)現(xiàn)最快的指令執(zhí)行;

A擴(kuò)展–支持原子訪問指令,可作為并發(fā)和獨(dú)占訪問管理的基礎(chǔ)(通常在基于 RTOS 的系統(tǒng)中);

C 擴(kuò)展–定義僅以 16 位編碼的壓縮指令,特別有趣,因?yàn)樗鼈兛梢暂p松地為常見和頻繁指令節(jié)省內(nèi)存空間,從而允許編譯器在可能的情況下選擇這些優(yōu)化;一個簡單的技巧,可以縮小代碼并同時提高性能;

B 擴(kuò)展–添加了多個位操作指令,這對于基于位域編碼值管理外設(shè)寄存器、協(xié)議和數(shù)據(jù)結(jié)構(gòu)的應(yīng)用程序來說具有位優(yōu)勢,其中一組組成的通用指令的功能通常可以由單個專用指令代替;

這就是 RISC-V ISA 概念的美妙之處,它是從頭開始構(gòu)建的,允許設(shè)計人員根據(jù)其目標(biāo)用例選擇要包含在處理器中的元素,從而優(yōu)化由此產(chǎn)生的功耗、性能和芯片占用空間。從工程角度來看,這是一種非常優(yōu)雅的方式,可以確保您只為那些您真正想要實(shí)現(xiàn)的事情“付出代價”。

為了增強(qiáng)應(yīng)用軟件的魯棒性,添加了堆棧監(jiān)控寄存器。這對于檢測和防止堆棧內(nèi)存溢出非常有用,這是非常常見的問題,但有時很難僅通過測試覆蓋率來發(fā)現(xiàn)。由于這些問題可能會損害系統(tǒng)的完整性并在運(yùn)行時產(chǎn)生應(yīng)用程序錯誤行為,因此這是一個非常好的功能,也是控制此類不可預(yù)見事件的基本安全網(wǎng)。

即使是最簡單的控制系統(tǒng)通常也必須管理多個決策路徑來為應(yīng)用程序提供服務(wù)并隨時調(diào)用適當(dāng)?shù)奶幚砝獭;蛘邔?shù)據(jù)緩沖區(qū)反復(fù)執(zhí)行一些重復(fù)計算。因此,實(shí)現(xiàn)的代碼將具有多個分支、循環(huán)和決策點(diǎn),其中程序流程可能會根據(jù)上下文而改變。由于這種模式很常見,CPU 還具有動態(tài)分支預(yù)測單元,以使此類處理更加高效。分支預(yù)測器的作用是觀察代碼行為,然后動態(tài)推斷在此類控制循環(huán)期間最有可能執(zhí)行的下一條指令。如果我們假設(shè)它在這方面做得很好,那么在選擇下一條要獲取執(zhí)行的指令時做出正確的猜測,它將顯著提高平均代碼執(zhí)行吞吐量。

下一個要提到的構(gòu)建塊與調(diào)試功能有關(guān)。除了標(biāo)準(zhǔn)Jtag外,CPU還支持兩線緊湊型Jtag調(diào)試接口,非常適合用戶應(yīng)用引腳數(shù)量有限的最小微控制器封裝。CPU 中還實(shí)現(xiàn)了多個性能監(jiān)視器寄存器,從而可以輕松地對所執(zhí)行代碼的運(yùn)行時行為進(jìn)行基準(zhǔn)測試。

任何嵌入式系統(tǒng)的另一個關(guān)鍵因素是對事件的響應(yīng)能力,在微控制器級別的深度嵌入式設(shè)備中,硬實(shí)時行為是強(qiáng)制要求的,這意味著應(yīng)用程序有有限的時間來響應(yīng)特定事件。低響應(yīng)延遲可以帶來許多不同的好處:允許應(yīng)用程序?yàn)楦嗖l(fā)事件提供服務(wù),提供合理的時間裕度以確保正確的任務(wù)處理,或者可能限制 CPU 速度以節(jié)省更多電量。

在架構(gòu)層面,瑞薩電子的實(shí)現(xiàn)添加了寄存器組保存功能,以改善延遲并使開發(fā)人員能夠享受其優(yōu)勢。在中斷服務(wù)的情況下,或者當(dāng)嵌入式 RTOS 必須交換當(dāng)前執(zhí)行的線程以響應(yīng)事件時,可以備份和恢復(fù) CPU 工作寄存器并加速上下文切換,舉兩個幾乎直接的例子。

為了進(jìn)一步幫助開發(fā)人員對應(yīng)用程序進(jìn)行基準(zhǔn)測試并驗(yàn)證其行為,還可以使用高效且緊湊的指令跟蹤單元,該單元可以進(jìn)一步深入了解系統(tǒng)的運(yùn)行時行為。

這概述了有關(guān) CPU 功能的詳細(xì)信息,其中一些功能可以根據(jù)應(yīng)用和市場要求進(jìn)行選擇。但是,在評估和制造基于這種新技術(shù)的實(shí)際產(chǎn)品時,還應(yīng)該考慮什么?首先,所需的工具鏈可作為開發(fā)和部署解決方案所需基礎(chǔ)設(shè)施的一部分。客戶將能夠受益于帶有配置插件的 Renesas e 2 studio 環(huán)境或任何支持基于 RISC-V 的 MCU 的主要商業(yè)第三方 IDE。這些都可以使用了。

其次,CPU 實(shí)現(xiàn)不僅僅是模擬的,其功能已經(jīng)在真實(shí)的硅產(chǎn)品實(shí)現(xiàn)中進(jìn)行了設(shè)計和驗(yàn)證。使用基于 LLVM 的開源編譯器工具鏈時,初始基準(zhǔn)測試顯示出令人印象深刻的 3.27 CoreMark/MHz 性能,優(yōu)于市場上的同類架構(gòu)。一旦第一個產(chǎn)品于 2024 年初推出,有關(guān)這一優(yōu)異成績的更多詳細(xì)信息將在EEMBC 網(wǎng)站上找到。正如許多人所指出的,專有商業(yè)編譯器的性能一旦經(jīng)過驗(yàn)證,預(yù)計將比初步結(jié)果更高。

這款新 CPU 是后續(xù)步驟的基石,為現(xiàn)有瑞薩 MCU 產(chǎn)品組合創(chuàng)建了一個額外的補(bǔ)充選項(xiàng)。瑞薩電子已準(zhǔn)備好為客戶提供最廣泛的解決方案,其中包括不斷發(fā)展的創(chuàng)新 RISC-V 架構(gòu)。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19804瀏覽量

233528 -

RISC-V

+關(guān)注

關(guān)注

46文章

2480瀏覽量

48263

原文標(biāo)題:瑞薩推出首款自研RISC-V內(nèi)核

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

瑞薩推出首款基于RISC-V指令集架構(gòu)的處理器內(nèi)核

瑞薩推出首款基于RISC-V指令集架構(gòu)的處理器內(nèi)核

評論