作為一名驗證工程師

你一定經歷過下面的靈魂拷問

”

驗證網表和RTL代碼是否一致?邏輯仿真是否為最優解?

每一個步驟后都有新的邏輯加入到netlist中,但新的邏輯的加入不能改變原netlist的邏輯功能,如何能進一步保證綜合后的網表與RTL之間的邏輯一致性?

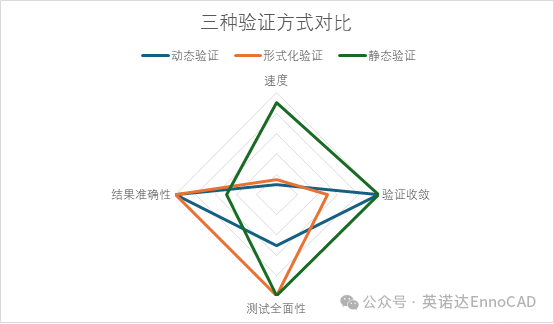

當芯片規模越來越大,設計復雜性的不斷增加,BUG表現的方式各不相同帶來驗證周期大幅增長,設計過程中的實際調試工作耗費大量的時間和精力,為了能夠最大程度的使得驗證收斂,我們也有越來越多的驗證方法..

相比邏輯仿真,形式驗證更適用于哪些場景?

形式驗證如何比較兩個設計是否等價?

本期的技術視頻將圍繞形式化驗證工具和大家展開分享等價性驗證GalaxEC如何有效提升設計和驗證效率,你想了解的知識點這里都有!

Part 1 : 4mins

芯華章數字驗證全流程工具平臺介紹

芯華章提供完整的數字驗證全流程工具平臺以滿足不同階段和不同需求的驗證。通過多工具融合與協同,提高驗證效率和準確性,從而縮短芯片設計周期和降低成本。

Part 2:4mins

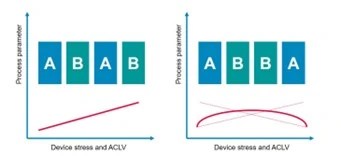

從RTL到門級網表的等價性驗證

在完整的芯片設計流程中,等價性驗證工具被廣泛應用到設計流程中的各個不同階段。諸如系統C模型級對RTL級、RTL級對RTL級、RTL級對門級以及門級實現之間,工程師需要檢驗變換前后的功能一致性,證明設計的變換或優化沒有產生功能的變化。

Part 3:12mins

貫穿IC設計全流程的三大等價檢查功能

SEC、LEC、HEC

GalaxEC已具備當下各類主流等價性驗證工具的所有核心功能,服務場景貫穿于數字芯片設計從系統級到前后端設計的各個階段,可一站式滿足用戶全流程等價性驗證需求,避免多工具切換成本,幫助工程師確保不同層次設計之間的一致性,支持遍歷式驗證,發現深層次的臨界設計錯誤,確保設計的正確性并實現正式簽核。

Part 4:3mins

GalaxEC深度結合芯華章智V驗證平臺各工具

芯華章智V驗證平臺提供的統一底層框架、統一覆蓋率數據庫和調試系統,Fusion Debug可直接支持GalaxEC等價性的結果調試,自動載入雙設計數據對比,在SEC場景中進行源和目標的代碼對比,從LEC報告中選擇有差異的邏輯錐并進行電路對比。

如果你對形式化驗證產品有更多興趣,歡迎點擊“閱讀原文”進入芯華章穹鵬GalaxEC產品介紹下載頁面,并與我們取得進一步聯系!

- 隱藏福利-

歡迎大家在學習知識點的同時

給我們的視頻一鍵三連

(點贊、推薦、分享)

截圖發至公眾號后臺

我們將挑選5位送出芯華章定制工程師頸枕!

-

芯華章

+關注

關注

0文章

179瀏覽量

11559

原文標題:技術分享 | 全面解讀貫穿IC設計全流程的三大等價性驗證功能

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子利用AI來縮小行業的IC驗證生產率差距

通過交互式對稱性校驗提升集成電路設計流程

智能無人設備從IP核到系統的全流程功能安全問題初探

西門子推出Questa One智能驗證解決方案

芯知識|廣州唯創電子語音芯片開發全流程解析:從選型到量產的實踐指南

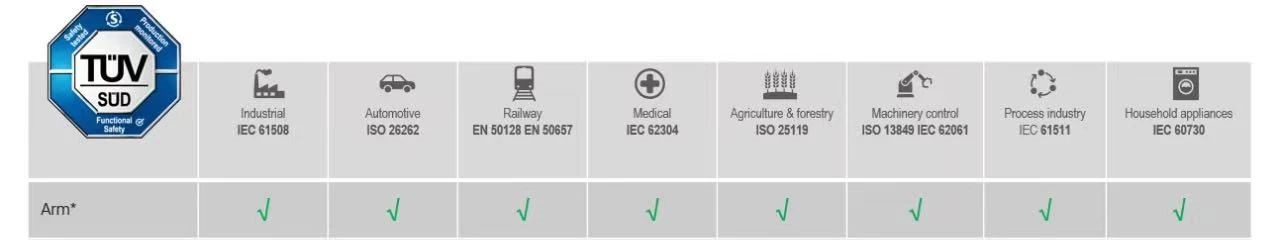

匯川技術機器人斬獲德國TUV功能安全認證

是德科技與Mavenir合作驗證32TRX mMIMO技術

充分考慮設備的體驗性易用性 藍鵬設計部將這一理念貫穿于整個研發過程

智能IC卡測試設備的技術原理和應用場景

【「數字IC設計入門」閱讀體驗】+ 數字IC設計流程

Lint靜態驗證工具如何助力IC設計

一文了解芯片測試的重要性

芯華章為產業提供覆蓋RISC-V全流程的驗證方案

大規模 SoC 原型驗證面臨哪些技術挑戰?

技術分享 | 全面解讀貫穿IC設計全流程的三大等價性驗證功能

技術分享 | 全面解讀貫穿IC設計全流程的三大等價性驗證功能

評論