線交互式UPS逆變器在主交流市電正常情況下是不向負載輸出功率的,處于熱備份狀態(tài),這是它與后備式UPS的根本區(qū)別。

2011-11-16 11:41:51 1450

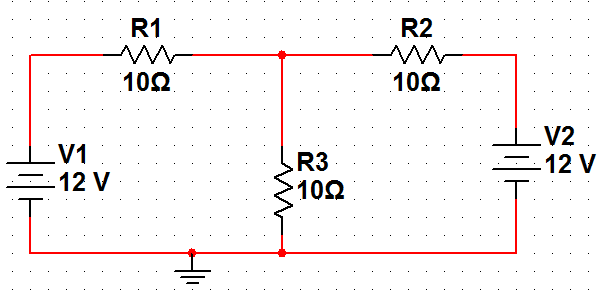

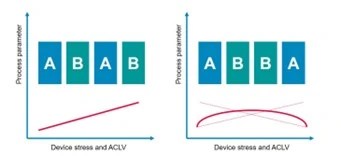

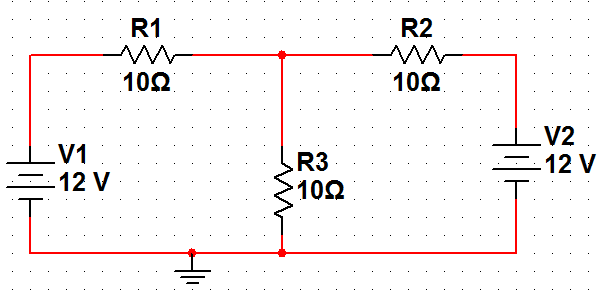

1450 進行電路分析時,有些電路具有對稱性。 利用其對稱性可以化簡電路求解。 如圖1所示電路,沿中間R3支路對折后,兩部分電路完全重合,這樣的電路就是對稱電路,R3支路為其對稱軸。 對稱電路對折后,重合的點為對稱點,對稱點的電位相等。

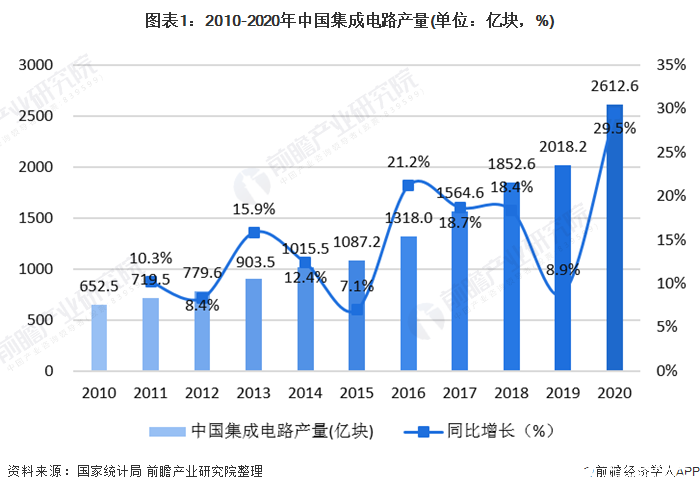

2023-03-09 14:38:30 5563

5563

交互式高速PCB設(shè)計

2013-08-16 16:00:51

對稱性加密算法:對稱式加密就是加密和解密使用同一個密鑰。信息接收雙方都需事先知道密匙和加解密算法且其密匙是相同的,之后便是對數(shù)據(jù)進行加解密了。對稱加密算法用來對敏感數(shù)據(jù)等信息進行加密。非對稱算法

2021-07-19 06:32:17

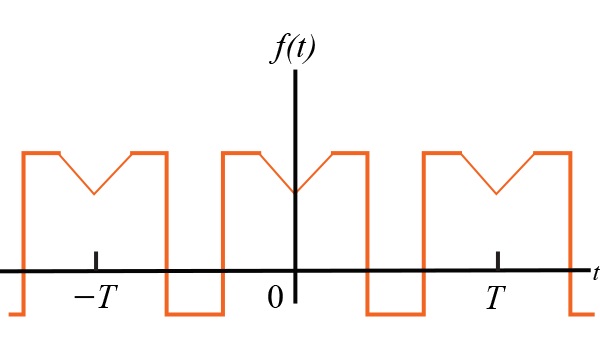

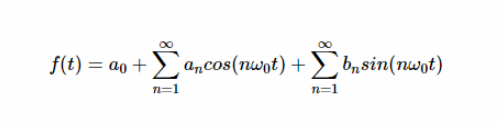

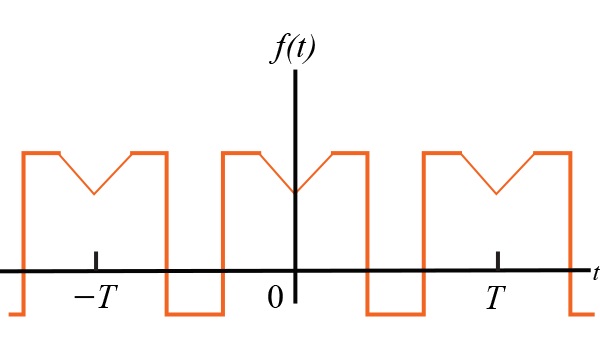

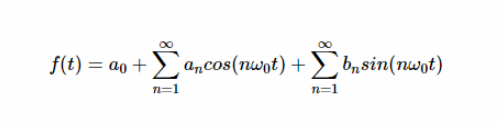

了解信號的對稱性如何可以簡化計算傅里葉系數(shù)時,用來找到電路的穩(wěn)態(tài)響應(yīng)求一個波形的傅里葉級數(shù)系數(shù)往往涉及一些相對繁瑣的計算。只有通過目視檢查波形,不執(zhí)行一個單一的計算,有時是可能的,以確定哪些系數(shù)將

2022-06-21 12:00:33

1、集成電路前段設(shè)計流程,寫出相關(guān)的工具數(shù)字集成電路設(shè)計主要分為前端設(shè)計和后端設(shè)計兩部分,前端以架構(gòu)設(shè)計為起點,得到綜合后的網(wǎng)表為終點。后端以得到綜合后的網(wǎng)表為起點,以生成交付Foundry進行流片

2021-07-23 10:15:40

基礎(chǔ)理論,能熟練使用EDA軟件軟件進行基本版圖設(shè)計。 培養(yǎng)對象 1.理工科背景,有志于數(shù)字集成電路設(shè)計工作的學(xué)生和轉(zhuǎn)行人員;2.需要充電,提升技術(shù)水平和熟悉設(shè)計流程的在職人員;3.集成電路設(shè)計企業(yè)的員工

2012-05-16 14:57:10

隨著集成電路制造技術(shù)的進步,人們已經(jīng)能制造出電路結(jié)構(gòu)相當復(fù)雜、集成度很高、功能各異的集成電路。但是這些高集成度,多功能的集成塊僅是通過數(shù)目有限的引腳完成和外部電路的連接,這就給判定集成電路的好壞帶來不少困難。

2019-08-21 08:19:10

(layout data)。集成電路設(shè)計技術(shù)實現(xiàn)的是一種轉(zhuǎn)換:把通訊、計算機等學(xué)科領(lǐng)域知識通過微電子 技術(shù)轉(zhuǎn)換成提高人類現(xiàn)實生活質(zhì)量的電子類產(chǎn)品。如果說集成電路技術(shù)推動了整個信息技術(shù) 領(lǐng)域的快速發(fā)展

2018-05-04 10:20:43

來源 電子發(fā)燒友網(wǎng)集成電路設(shè)計的流程一般先要進行軟硬件劃分,將設(shè)計基本分為兩部分:芯片硬件設(shè)計和軟件協(xié)同設(shè)計。芯片硬件設(shè)計包括:1.功能設(shè)計階段。設(shè)計人員產(chǎn)品的應(yīng)用場合,設(shè)定一些諸如功能、操作速度

2016-06-29 11:27:02

正規(guī)的集成電路設(shè)計公司在進行片上系統(tǒng)(SoC)設(shè)計時都有明確的崗位分工,甚至?xí)圆块T的形式來區(qū)分各部分的職責(zé),而且很多時候集成電路設(shè)計公司還會提供整體解決方案,包括芯片、軟件和硬件,生產(chǎn)商直接按這個

2018-08-15 09:25:59

什么是集成電路設(shè)計?集成電路設(shè)計可以大致分為哪幾類?其設(shè)計流程是如何進行的?

2021-06-22 07:37:26

。同時,集成電路設(shè)計進入了超深亞微米領(lǐng)域,金屬層增加、線寬減小,串擾延遲、噪聲等信號完整性問題(SI)對工程師的時序分析能力和水平要求越來越高,在一些大的芯片設(shè)計企業(yè)會設(shè)置有專門的信號完整性工程師崗

2020-09-01 16:51:01

LDO模擬集成電路設(shè)計

2022-05-09 00:52:51

LabVIEW MathScript交互式窗口加載錯誤,重新安裝還是出現(xiàn)同樣的錯誤

2014-11-05 17:40:33

什么是UVM交互式調(diào)試庫

2020-12-17 07:34:46

最小占板面積來對相似的設(shè)計進行分類。你還可以在產(chǎn)品文件夾內(nèi)的同一彈出窗口中背靠背的查看每一款設(shè)計的電路原理圖、物料清單 (BOM)、操作圖、以及工作值。你可以通過單擊頂部的交互式設(shè)計圖標或者是

2018-09-05 15:37:15

altium designer 10 怎么沒智能交互式布線啊? 前兩天看網(wǎng)上出altium designer 10 了,就下了個裝上了,但是用的時候發(fā)現(xiàn)沒有智能交互式布線的菜單,由于剛學(xué)這個軟件不久,想請問各位大蝦是怎么回事啊??

2011-04-29 22:32:45

Candence 16.5已經(jīng)發(fā)布了一段時間了,但總發(fā)現(xiàn)問題不斷.其實很多問題都是可以解決的,只是我們習(xí)慣了以前的操作而已,比如很多人都發(fā)現(xiàn)在16.5中,交互式布居然不能使用了,其實只是我們默認沒有

2012-04-19 22:11:11

的考慮、微電子器件基礎(chǔ)、模擬電路基本模塊、負反饋理論、電路設(shè)計和保護電路設(shè)計等多方面內(nèi)容,以直觀的方式,充分考慮了整體系統(tǒng)目標、集成電路開發(fā)流程和電路的可靠性,而且各章節(jié)獨立性較強,可以滿足不同讀者的需求

2017-10-27 18:25:56

數(shù)字計算等。在這種情況下,獲得不依賴集成芯片的電子產(chǎn)品的可能性很小。

集成電路還有助于電子產(chǎn)品的小型化、提高其性能、降低成本等。

例如,集成電路的成本降低功能是通過提供相對成本有效的選擇來實現(xiàn)的,即

2023-08-01 11:23:10

。模擬集成電路的主要構(gòu)成電路有:放大器、濾波器、反饋電路、基準源電路、開關(guān)電容電路等。模擬集成電路設(shè)計主要是通過有經(jīng)驗的設(shè)計師進行手動的電路調(diào)試,模擬而得到,與此相對應(yīng)的數(shù)字集成電路設(shè)計大部分是通過使用硬件描述語言在EDA軟件的控制下自動的綜合產(chǎn)生。

2011-11-14 14:04:28

大四了,保研,在選導(dǎo)師這邊糾結(jié)了一邊是集成電路設(shè)計,有數(shù)字,有模擬的一邊是嵌入式我對這兩方面都還感興趣,我想問問這兩個今后的發(fā)展趨勢是什么?做這兩個的利弊都有哪些?一學(xué)長說,嵌入式現(xiàn)在比較流行ARM

2011-09-30 16:28:53

關(guān)于TTL集成電路與CMOS集成電路看完你就懂了

2021-09-28 09:06:34

CMOS模擬集成電路該如何去設(shè)計?這里有一份CMOS模擬集成電路設(shè)計手冊請查收。

2021-06-22 06:27:16

在電子電路設(shè)計中,開始通常假設(shè)元器件在室溫下工作。單片微波集成電路設(shè)計,尤其是,當直流電流流過體積日益縮小的器件時導(dǎo)致熱量成兩倍,三倍甚至四倍高于室溫,就違反了元器件在室溫下工作的假設(shè)。此種情況下

2019-07-04 06:47:35

]。 由于圖像的類型和內(nèi)容多種多樣,自動分割方法對多目標或背景復(fù)雜的圖像很難奏效。因此,往往需要一定的人工干預(yù)。目前,交互式圖像分割方法在醫(yī)療及臨床等領(lǐng)域有著廣泛的應(yīng)用。然而,通過人工目測的方式進行圖像分割

2009-09-19 09:19:45

迅速發(fā)展的射頻集成電路為從事各類無線通信的工程技術(shù)人員提供了廣闊的前景。但同時, 射頻電路的設(shè)計要求設(shè)計者具有一定的實踐經(jīng)驗和工程設(shè)計能力。本文總結(jié)的一些經(jīng)驗可以幫助射頻集成電路開發(fā)者縮短開發(fā)周期, 避免走不必要的彎路, 節(jié)省人力物力。

2019-08-30 07:49:43

微波集成電路設(shè)計Smith圓圖與阻抗匹配網(wǎng)絡(luò)李芹,王志功東南大學(xué)射頻與光電集成電路研究所

2009-08-24 01:39:22

我想使用交互式IO命令打開/關(guān)閉電源輸出(N8738A和N5765A)。我可以使用Agilent Connection Expert查看我的電源......但我找不到任何交互式IO命令來打開/關(guān)閉

2018-11-19 10:48:59

` 本帖最后由 gk320830 于 2015-3-4 20:25 編輯

數(shù)字集成電路設(shè)計流程設(shè)計輸入:以電路圖或HDL語言的形式形成電路文件;輸入的文件經(jīng)過編譯后,可以形成對電路邏輯模型的標準

2011-11-22 15:57:06

數(shù)字集成電路設(shè)計流程中一般有幾種類型的仿真,其區(qū)別是什么?

2015-10-29 22:25:12

模擬集成電路設(shè)計中有哪些設(shè)計工具包?

2020-12-21 06:30:10

CMOS模擬集成電路設(shè)計,一共5個部分

2016-05-15 09:30:43

模擬CMOS集成電路設(shè)計

2019-03-13 15:34:10

請問哪位大佬整理過模擬射頻集成電路設(shè)計的一些基本入門詞以及專業(yè)解釋?

2021-06-22 07:11:27

求助誰有何樂年《模擬集成電路設(shè)計與仿真 》的習(xí)題答案?

2021-06-22 06:19:30

運放的對稱性在溫度低的時候可能不是很明顯,影響也不大,但是隨著溫度的升高(例如從25度~~120度),溫度升高輸出方波的上述時間跟下降時間偏差也會越大,提高運放的SR能相對的減弱這種不對稱的影響,但是導(dǎo)致這種不對稱的根本原因是什么?運放的哪些參數(shù)可以反映出它的不對稱性?

2024-09-10 08:12:10

cmos射頻集成電路設(shè)計這本被譽為射頻集成電路設(shè)計指南的書全面深入地介紹了設(shè)計千兆赫(GHz)CMOS射頻集

2008-09-16 15:43:18 317

317 顱骨圖像在幾何上具有對稱性特征,根據(jù)轉(zhuǎn)動慣量在幾何對稱性對象上所具有的良好性質(zhì),提出一種改進的計算對稱軸的算法,該算法利用計算機語言編程實現(xiàn)。結(jié)果表明,利用改

2009-04-14 08:42:20 36

36 對稱性和格點理論在矩量法中的應(yīng)用:本文闡述了一種基于矩量法基本原理和格點理論,利用研究對象自身形狀的對稱性,減少矩陣存儲量的方法。利用該法,求解了方形導(dǎo)體板、球

2009-10-23 16:48:01 11

11 通過SPICE交互式仿真探討了一些運算放大器電路。主題包括反相和非反相設(shè)計,以及峰值探測器。Chapter 5 of the NI Multisim Fundamental Circuits

2010-03-29 09:18:03 34

34 提供了一些詳細的電路,通過交互式SPICE仿真研究基本的電子學(xué)定律和無源器件的設(shè)計。

2010-03-29 09:27:21 1

1 等成本也在不斷上漲,如何降低經(jīng)營成本,提升生產(chǎn)效率,優(yōu)化資源配置等,是目前不少集成電路生產(chǎn)企業(yè)面臨的難題。 同期也有很多的集成電路生產(chǎn)企業(yè)通過ERP系統(tǒng)實現(xiàn)縮短

2023-12-12 11:33:20

對稱性

對稱操作

對稱要素

2010-08-26 15:51:19 0

0 關(guān)于射頻(RF) 關(guān)于射頻集成電路 無線通信與射頻集成電路設(shè)計 課程相關(guān)信息 RFIC相關(guān)IEEE/IEE期刊和會議• 是什么推動了RFIC 的發(fā)展?• Why

2010-10-02 10:48:02 135

135 什么是IPTV(交互式網(wǎng)絡(luò)電視)

IPTV(InternetProtocolTVorInteractivePersonalTV)也叫交互式網(wǎng)絡(luò)電視,是利用寬帶網(wǎng)的基礎(chǔ)設(shè)施,以家用電視機或

2008-10-27 08:52:59 7833

7833 選購交互式白板的心得

在選購交互式白板的過程中,許多人對于交互式白板的硬件、軟件、服務(wù)都不可能做到面面俱到,于

2010-02-09 10:00:23 758

758 集成電路設(shè)計流程 集成電路設(shè)計方法 數(shù)字集成電路設(shè)計流程 模擬集成電路設(shè)計流程 混合信號集成電路設(shè)計流程 SoC芯片設(shè)計流程

2011-03-31 17:09:12 381

381 本內(nèi)容詳細介紹了集成電路設(shè)計方法概論

2011-05-23 16:40:51 125

125 集成電路設(shè)計導(dǎo)論內(nèi)容有數(shù)位電路分析與設(shè)計,集成電路設(shè)計導(dǎo)論,類比電路分析與設(shè)計等。

2011-08-28 12:06:42 0

0 集成電路設(shè)計的流程一般先要進行軟硬件劃分,將設(shè)計基本分為兩部分:芯片硬件設(shè)計和軟件協(xié)同設(shè)計。

2011-10-28 09:48:37 24011

24011 炬力集成電路設(shè)計有限公司,炬力集成是一家致力于集成電路設(shè)計與制造的大型半導(dǎo)體技術(shù)集團,美國的納斯達克上市公司

2012-05-24 14:40:16 1457

1457 CMOS射頻集成電路設(shè)計介紹。

2016-03-24 17:15:11 4

4 模擬CMOS集成電路設(shè)計經(jīng)典書籍,值得一看。

2016-04-06 17:24:26 55

55 集成電路設(shè)計基礎(chǔ),有需要的朋友下來看看。

2016-07-20 16:40:29 0

0 射頻集成電路設(shè)計基礎(chǔ)講義原理詳解!適合新人和初學(xué)者!

2016-09-09 16:58:09 0

0 WebServer的嵌入式實現(xiàn)與交互式設(shè)計_高翔峰

2017-03-19 11:28:02 1

1 針對現(xiàn)代網(wǎng)絡(luò)教育師生交互性差的問題給出解決方案。采用當前流行的MVC模式的Django框架開發(fā)了一個B/S結(jié)構(gòu)的基于Web的交互式教學(xué)平臺系統(tǒng)。交互式課程評價體系以及自動分組算法可以使得學(xué)生以團隊協(xié)作方式學(xué)習(xí),教師進行監(jiān)測和評分。

2017-11-13 10:45:22 12

12 在電子電路設(shè)計中,開始通常假設(shè)元器件在室溫下工作。單片微波集成電路設(shè)計,尤其是,當直流電流流過體積日益縮小的器件時導(dǎo)致熱量成兩倍,三倍甚至四倍高于室溫,就違反了元器件在室溫下工作的假設(shè)。此種情況下

2017-11-24 07:13:01 1048

1048

數(shù)據(jù)庫中待挖掘的數(shù)據(jù)模糊化處理,借助關(guān)聯(lián)規(guī)則挖掘方法Apriori算法對預(yù)處理后的數(shù)據(jù)庫進行了挖掘。挖掘出了結(jié)構(gòu)對稱性和產(chǎn)品功能區(qū)間、性能區(qū)間及約束區(qū)間之間的模糊關(guān)聯(lián)規(guī)則。結(jié)果表明:通過對結(jié)構(gòu)對稱性實例進行數(shù)據(jù)挖掘,

2018-03-10 10:49:50 0

0 本文檔內(nèi)容介紹了基于CMOS模擬集成電路設(shè)計,供參考

2018-03-26 15:21:11 62

62 鰭式場效晶體管集成電路設(shè)計與測試 鰭式場效晶體管的出現(xiàn)對 集成電路 物 理設(shè)計及可測性設(shè)計流程具有重大影響。鰭式場效晶體管的引進意味著在集成電路設(shè)計制程中互補金屬氧化物( CMOS )晶體管必須被建模成三維(3D)的器件,這就包含了各種復(fù)雜性和不確定性。

2018-05-25 09:26:00 5620

5620

TriQuint公司中國區(qū)總經(jīng)理熊挺先生為大家?guī)?b class="flag-6" style="color: red">集成電路設(shè)計介紹及最新技術(shù)解析

2018-07-02 11:25:28 5504

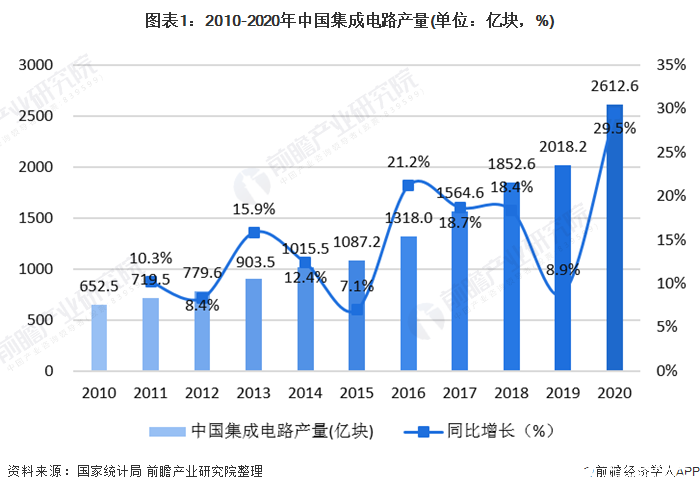

5504 中國集成電路設(shè)計業(yè)的狀況分析閔鋼摘要:自“十二五”以來,中國集成電路設(shè)計業(yè)持續(xù)快速發(fā)展。2017 年中國集成

2019-03-16 10:36:10 8136

8136 本文檔的主要內(nèi)容詳細介紹的是集成電路設(shè)計教程之集成電路版圖設(shè)計基礎(chǔ)的詳細資料說明免費下載。

2019-04-24 16:07:41 0

0 芯片設(shè)計包含很多流程,每個流程的順利實現(xiàn)才能保證芯片設(shè)計的正確性。因此,對芯片設(shè)計流程應(yīng)當具備一定了解。本文將講解芯片設(shè)計流程中的數(shù)字集成電路設(shè)計、模擬集成電路設(shè)計和數(shù)模混合集成電路設(shè)計三種設(shè)計流程。

2019-08-17 11:26:16 16315

16315 傅立葉級數(shù)函數(shù)用于查找電路的穩(wěn)態(tài)響應(yīng)。有四種不同類型的對稱性可用于簡化評估傅里葉系數(shù)的過程。

2019-09-01 09:43:03 5912

5912

集成電路設(shè)計:該專業(yè)學(xué)生主要學(xué)習(xí)電子信息類基本理論和基本知識,重點接受集成電路設(shè)計與集成系統(tǒng)方面的基本訓(xùn)練,具有分析和解決實際問題等方面的基本能力。

2020-07-13 08:56:09 29691

29691 芯片設(shè)計包含很多流程,每個流程的順利實現(xiàn)才能保證芯片設(shè)計的正確性。因此,對芯片設(shè)計流程應(yīng)當具備一定了解。本文將講解芯片設(shè)計流程中的數(shù)字集成電路設(shè)計、模擬集成電路設(shè)計和數(shù)模混合集成電路設(shè)計三種設(shè)計流程

2020-10-30 17:13:49 1404

1404 集成電路設(shè)計(Integrated circuit design, IC design),亦可稱之為超大規(guī)模集成電路設(shè)計(VLSI design),是指以集成電路、超大規(guī)模集成電路為目標的設(shè)計流程

2021-02-18 16:31:23 4826

4826

針對已有多數(shù)交互式分割方法交互方式單一、預(yù)測結(jié)果精度較低的問題,構(gòu)建一種基于雙階段網(wǎng)絡(luò)的目標分割模型 Scribner,以實現(xiàn)更完整和精細的交互式目標分割。采用靈活涂畫的交互方式,通過編碼形成交互

2021-03-11 11:48:45 11

11 模擬集成電路設(shè)計說明。

2021-03-22 13:54:28 49

49 集成電路設(shè)計概述說明。

2021-04-09 14:10:56 40

40 SHARC-Request評估碼的DTS對稱性

2021-06-04 11:47:20 2

2 用于功能性核磁共振數(shù)據(jù)的交互式可視分析系統(tǒng)

2021-06-29 16:46:23 63

63 orcad與Cadence Allegro的交互式操作應(yīng)該怎么處理? 答:orcad與Cadence Allegro的交互式操作需要滿足以下兩個要求才可以實現(xiàn): ??Orcad輸出的是Allegro

2021-11-17 11:11:57 12086

12086

《模擬CMOS集成電路設(shè)計》.pdf

2022-01-20 10:02:30 0

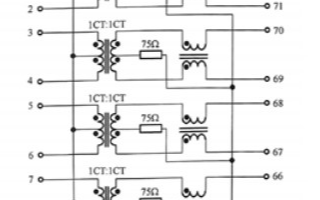

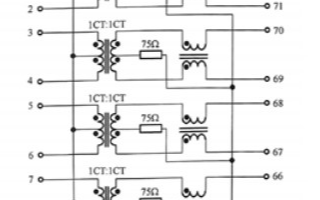

0 盈盛(華強盛)電子導(dǎo)讀:上一個節(jié)點給大家分享了網(wǎng)絡(luò)變壓器典型類型線圈(2.6.3)通過BL檢測能檢查出線圈的那些錯誤,接下來再給大家來介紹:BL檢測由四個單元電路組成的網(wǎng)絡(luò)變壓器的對稱性的原理。

2022-02-24 09:33:27 3168

3168

CMOS集成電路設(shè)計基礎(chǔ)免費下載。

2022-03-03 10:06:12 0

0 了解信號的對稱性如何可以簡化計算傅里葉系數(shù)時,用來找到電路的穩(wěn)態(tài)響應(yīng)

2022-06-21 14:38:57 4805

4805

集成電路設(shè)計的流程一般先要進行軟硬件劃分,將設(shè)計基本分為兩部分:芯片硬件設(shè)計和軟件協(xié)同設(shè)計。

2022-09-08 16:37:28 2386

2386 內(nèi)容提要8nm 射頻集成電路流程支持射頻集成電路設(shè)計過程的所有階段,包括建模、兼顧電磁影響的 RF 仿真和完整簽核驗證流程該流程加速了射頻集成電路設(shè)計,有助于驅(qū)動廣泛的 5G 應(yīng)用中國上海,2022

2022-10-18 14:16:56 1805

1805 CP對稱的破缺與我們宇宙中物質(zhì)-反物質(zhì)不對稱性密切相關(guān)。在我們周圍,地球上,太陽系等都是由物質(zhì)構(gòu)成,這是一個眾人知曉的事實。

2022-10-25 16:23:41 2394

2394 該報告綜述了麥克斯韋方程的對稱性,包括對偶對稱、空間平移對稱、時間平移對稱、旋轉(zhuǎn)對稱、鏡像(宇稱)對稱、時間反演對稱、規(guī)范對稱、洛倫茲(相對論)對稱,及計算電磁中的對稱性。

2022-11-07 10:20:18 1387

1387 電子發(fā)燒友網(wǎng)站提供《交互式LED名稱.zip》資料免費下載

2022-11-11 09:12:11 0

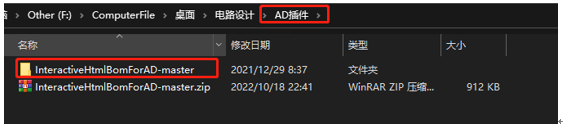

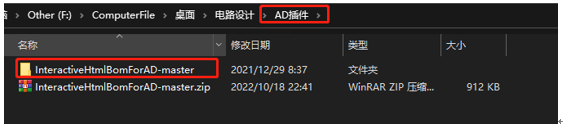

0 介紹一個開源的制作交互式BOM的AD插件

2023-01-30 15:09:49 6135

6135

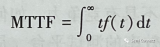

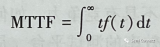

集成電路可拿性是指.在規(guī)定的條件下和規(guī)定的時問內(nèi),集成電路完成規(guī)定功能的能力。可通過可靠度、失效率、平均無故障工作時間、平均失效時間等來評價集成電路的可靠性。可靠性包含耐久性、可維修性和設(shè)計可靠性三

2023-06-14 09:26:46 2144

2144

EDA有著“芯片之母”稱號,一個完整的集成電路設(shè)計和制造流程主要包括工藝平臺開發(fā)、集成電路設(shè)計和集成電路制造三個階段,三個設(shè)計與制造的主要階段均需要對應(yīng)的EDA工具作為支撐。

2023-09-28 14:31:23 2678

2678

如何證明波導(dǎo)正規(guī)模的電場磁場具有時間對稱性和反對稱性? 波導(dǎo)是一種承載電磁波的結(jié)構(gòu),是電磁波導(dǎo)管的一種。其中,波在導(dǎo)管內(nèi)傳輸時,其電場和磁場可以表現(xiàn)出時間對稱性和反對稱性。 時間對稱性可以用

2023-10-19 17:21:46 1110

1110 Pivottablejs是一個通過IPython widgets集成到Python中的JavaScript庫,允許用戶直接從DataFrame數(shù)據(jù)創(chuàng)建交互式和靈活的匯總報表。可以進行高效、清晰的數(shù)據(jù)分析和表示,幫助將數(shù)據(jù)從Pandas DataFrame轉(zhuǎn)換為易于觀察的交互式數(shù)據(jù)透視表。

2023-11-21 16:15:59 1178

1178

專用集成電路設(shè)計流程是指通過設(shè)計和制造一種特定功能的芯片,以滿足特定應(yīng)用場景的要求。專用集成電路(Application Specific Integrated Circuit,簡稱ASIC

2024-05-04 17:20:00 2123

2123 專用集成電路(ASIC)設(shè)計流程是指將特定應(yīng)用需求轉(zhuǎn)化為硅芯片的過程。下面將詳細介紹ASIC設(shè)計流程,并進一步探討ASIC的特點。 一、ASIC設(shè)計流程: 需求分析:確定設(shè)計要求和功能需求。 架構(gòu)

2024-05-04 15:00:00 877

877 應(yīng)用需求進行優(yōu)化的特點,具備了更高的性能、更低的功耗和更小的尺寸。 專用集成電路的設(shè)計流程主要包括需求分析、系統(tǒng)設(shè)計、電路設(shè)計、物理設(shè)計、驗證測試和制造流程。 需求分析:在這一階段,首先需要明確設(shè)計的應(yīng)用需求,在了解并分析應(yīng)用場景和功能要求后,確定集成電路的性能指標

2024-05-04 15:02:00 1234

1234 集成電路設(shè)計流程是一個復(fù)雜且精細的過程,主要包括以下幾個關(guān)鍵步驟: 一、規(guī)格定義 需求分析 :明確電路的需求、功能和性能指標,如成本、功耗、算力、接口方式、安全等級等。這是設(shè)計流程的基礎(chǔ),為后續(xù)

2024-09-04 18:20:56 2307

2307 ASIC(Application Specific Integrated Circuit)即專用集成電路,是指應(yīng)特定用戶要求和特定電子系統(tǒng)的需要而設(shè)計、制造的集成電路。ASIC集成電路設(shè)計流程可以

2024-11-20 14:59:34 1665

1665 其中之一。 據(jù)了解,集成電路設(shè)計園二期由海淀區(qū)政府和中關(guān)村發(fā)展集團聯(lián)合打造,ICPARK運營服務(wù)。作為北京集成電路產(chǎn)業(yè)的核心承載區(qū),集成電路設(shè)計園二期揭牌啟動,標志著海淀區(qū)在推動產(chǎn)業(yè)創(chuàng)新能級提升、構(gòu)建高精尖產(chǎn)業(yè)生態(tài)方面邁出了重要一

2025-03-12 10:18:22 306

306

電子發(fā)燒友App

電子發(fā)燒友App

評論