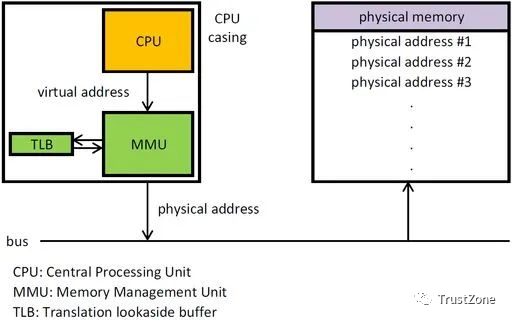

TLB 是 translation lookaside buffer 的簡稱。首先,我們知道 MMU 的作用是把虛擬地址轉換成物理地址。

虛擬地址和物理地址的映射關系存儲在頁表中,而現在頁表又是分級的。

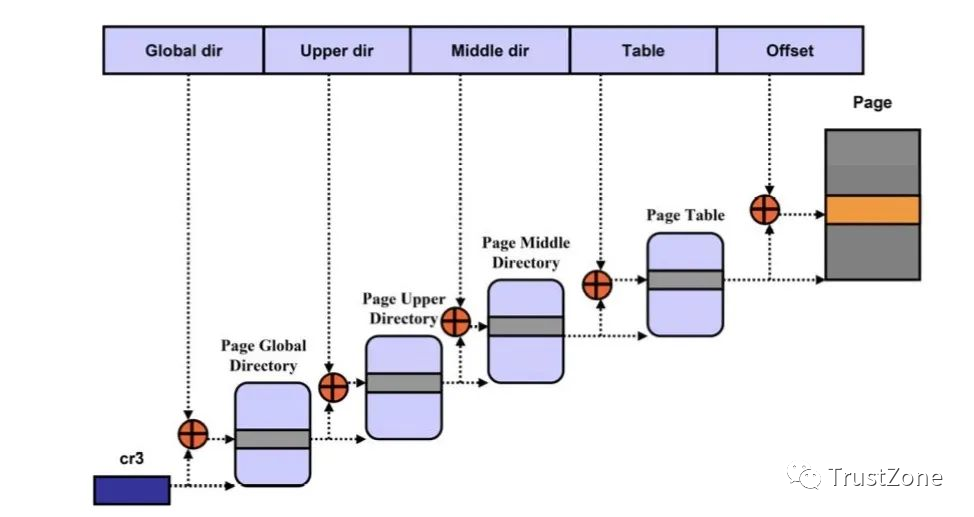

64 位系統一般都是 3~5 級。

常見的配置是 4 級頁表,就以 4 級頁表為例說明。

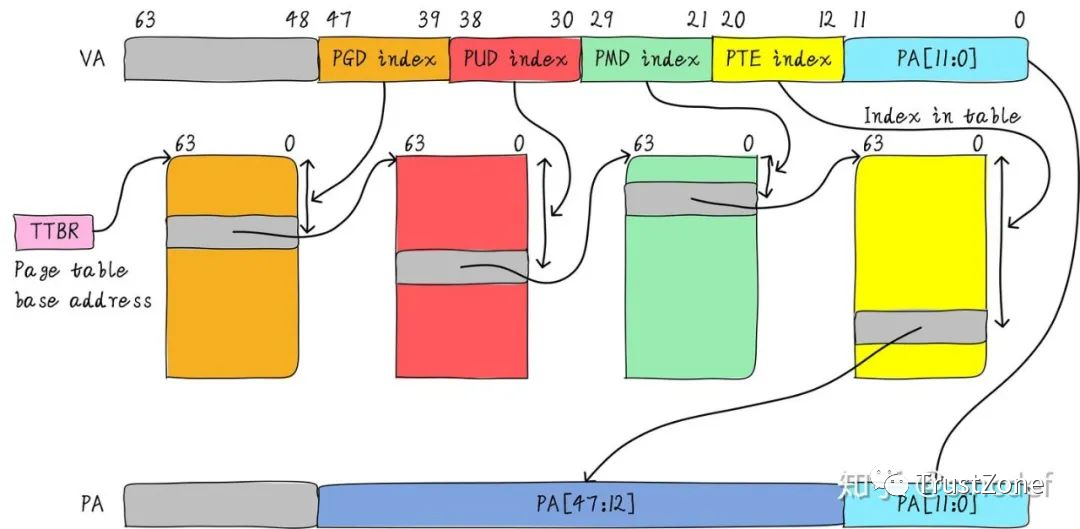

分別是 PGD、PUD、PMD、PTE 四級頁表。

在硬件上會有一個叫做頁表基地址寄存器,它存儲 PGD 頁表的首地址。

MMU 就是根據頁表基地址寄存器從 PGD 頁表一路查到 PTE,最終找到物理地址(PTE頁表中存儲物理地址)。

這就像在地圖上顯示你的家在哪一樣,我為了找到你家的地址,先確定你是中國,再確定你是某個省,繼續往下某個市,最后找到你家是一樣的原理。一級一級找下去。(這個比喻真的不錯)

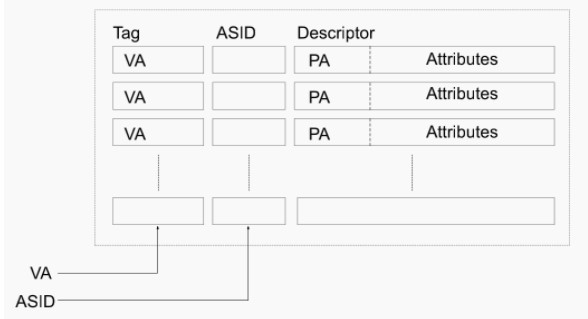

這個過程你也看到了,非常繁瑣。如果第一次查到你家的具體位置,我如果記下來你的姓名和你家的地址。下次查找時,是不是只需要跟我說你的姓名是什么,我就直接能夠告訴你地址,而不需要一級一級查找。

四級頁表查找過程需要四次內存訪問。延時可想而知,非常影響性能。頁表查找過程的示例如下圖所示。以后有機會詳細展開,這里了解下即可。

-

寄存器

+關注

關注

31文章

5421瀏覽量

123332 -

內存

+關注

關注

8文章

3108瀏覽量

74987 -

硬件

+關注

關注

11文章

3461瀏覽量

67193 -

MMU

+關注

關注

0文章

92瀏覽量

18639

發布評論請先 登錄

詳解TLB的作用及工作原理

請問AM335 u-boot 中的MMU,gd->arch.tlb_addr是在哪里初始化的?

labview2015調用tlb庫錯誤信息:LabVIEW: 輸入為空引用句柄或之前已刪除的引用句柄。

FIDEMAILATION中的TLB異常

以Freescale的E500內核為例簡單介紹TLB Entry基本組成結構

看一條關于TLB維護的指令

P2020 TLB0/TLB1失效的原因?怎么解決?

嵌入式處理器的TLB電路設計

CPU場景下的TLB相關細節

為什么要有TLB

為什么要有TLB

評論