《A 14 Bit 1 GSs RF Sampling Pipelined ADC With Background Calibration》所述的開關(guān)電容比較器結(jié)構(gòu)關(guān)注幾個(gè)點(diǎn):

1.Flash通路的上極板采樣開關(guān)為  Latch放開輸出復(fù)位,Latch立即進(jìn)行正反饋放大,加快了比較器的速度,給MDAC建立留更多時(shí)間。

Latch放開輸出復(fù)位,Latch立即進(jìn)行正反饋放大,加快了比較器的速度,給MDAC建立留更多時(shí)間。

2.輸入到Latch的輸入有兩級衰減,即開關(guān)電容處有 的衰減和pre-amp的增益小于1,前者利用開關(guān)電容電路實(shí)現(xiàn)電壓相減功能而無法避免,后者目的減小返回到輸入端的kick-back噪聲。衰減特性使得Latch級的noise和offset被放大。

的衰減和pre-amp的增益小于1,前者利用開關(guān)電容電路實(shí)現(xiàn)電壓相減功能而無法避免,后者目的減小返回到輸入端的kick-back噪聲。衰減特性使得Latch級的noise和offset被放大。

3.Latch級Cc電容存在有兩個(gè)好處:輸入AC耦合,再生相位輸入管gm=gmn+gmp,增加帶寬,減小延時(shí)時(shí)間;復(fù)位相位,避免由于復(fù)位開關(guān)關(guān)斷引入的時(shí)鐘饋通通過NMOS寄生電容耦合而使輸入電壓幅度下降過多,使NMOS偏離正確工作狀態(tài)。

仿真分析

仿真顯示比較器輸入越小,延時(shí)越大。此外看到,輸入比較大時(shí),復(fù)位相位Latch的輸出不會(huì)相等。

小輸入情況下,仿真延時(shí)接近 2tD ;大輸入情況下,仿真延時(shí)呈現(xiàn)線性特性意味著Latch級進(jìn)入了大信號工作區(qū)間。

-

電路分析

+關(guān)注

關(guān)注

62文章

523瀏覽量

99514 -

NMOS

+關(guān)注

關(guān)注

3文章

364瀏覽量

35648 -

比較器

+關(guān)注

關(guān)注

14文章

1845瀏覽量

109099 -

開關(guān)電容

+關(guān)注

關(guān)注

0文章

103瀏覽量

18762

發(fā)布評論請先 登錄

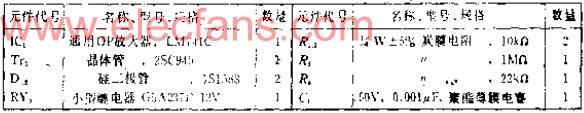

高速比較器電路的設(shè)計(jì)實(shí)現(xiàn)和仿真實(shí)驗(yàn)分析

【原創(chuàng)精心制作】高速AD、DA和高速比較器模塊電路設(shè)計(jì)

請教高速比較器輸入阻抗?

高速比較器技術(shù)

AN-352: 如果使用得當(dāng),高速比較器可提供許多有用的電路功能

AN-352: 如果使用得當(dāng),高速比較器可提供許多有用的電路功能

開關(guān)電容高速比較器電路分析

開關(guān)電容高速比較器電路分析

評論