作者:劉松,文章來源: 松哥電源微信公眾號

美國計劃禁止用于Gate-all-around GAA新技術制造芯片所必需的EDA軟件出口到中國大陸,GAA(環繞柵極)是GAA FET,那么,什么是GAA FET(環繞柵極場效應晶體管)?

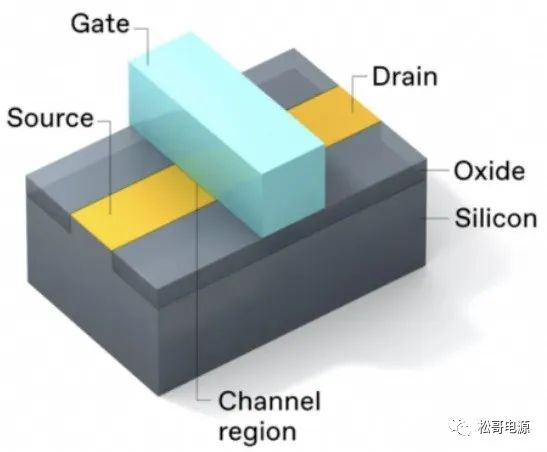

數字芯片最基本單元是MOSFET,其工藝發展到7nm、3nm、2nm,這個半導體工藝尺寸是MOSFET柵極(溝槽)寬度。早期MOSFET使用平面結構,溝槽寬度越小,漏極到源極距離越小,載流子流動跨越溝道導通時間減小,工作頻率越高;同時,溝道完全開通所加柵極電壓越低,開關損耗越低;而且,溝道導通電阻降低,導通損耗也降低。

但是,工藝尺寸越低,短溝道效應越明顯。短溝道效應就是晶胞單元漏極到源極間距不斷減小,柵極下部接觸面積越來越小,柵極難以耗盡溝道載流子,其對溝道控制力不斷減弱;因此,器件處于截止狀態時漏電流會急劇增加,惡化其性能,靜態功耗增加。

圖1:平面MOSFET結構

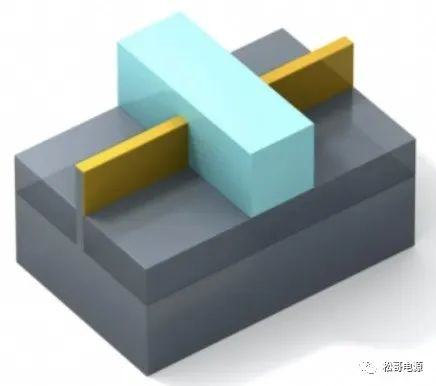

如果采用立體結構,增加柵極和溝道接觸面積,如新的FinFET鰭型三維結構,就是將柵極包裹三個側面溝道,就可以解決上述問題,如圖2所示。

圖2 FinFET鰭型結構

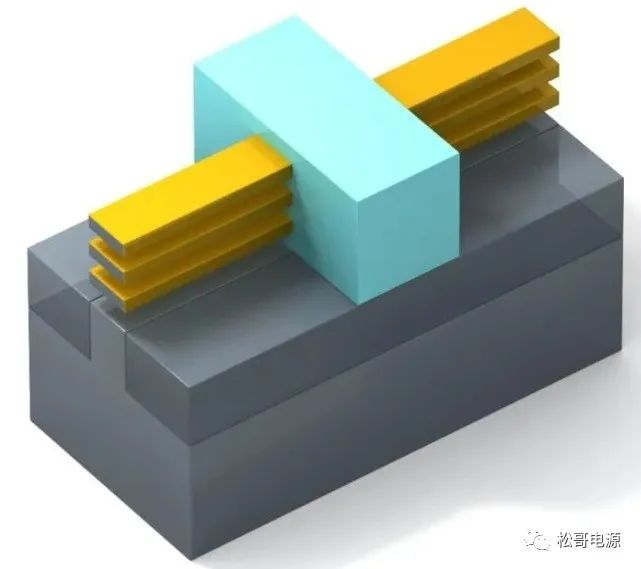

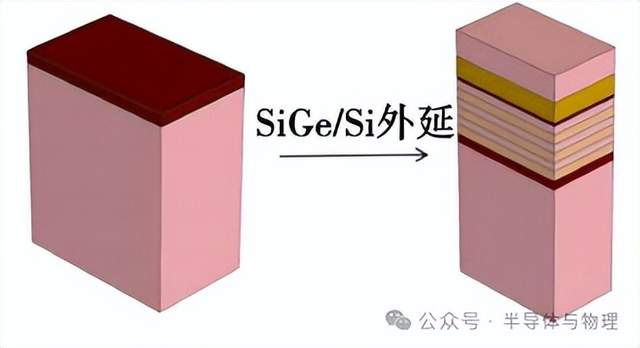

為了進一步提高柵極對溝道控制能力,縮小單元尺寸,降低電壓,GAA柵極環繞結構被開發出來,如圖3所示。

圖3 柵極環繞結構

GAA柵極環繞晶體管結構的柵極在垂直方向被分成幾個條帶RibbonFET,在其溝道區域,大幅增強對載流子控制,從而實現更好性能,同時也更容易優化工藝。

?免責聲明:本文為網絡轉載文章,轉載此文目的在于傳播相關技術知識,版權歸原作者所有,如涉及侵權,請聯系小編刪除。

審核編輯 黃宇

-

eda

+關注

關注

71文章

2881瀏覽量

176413 -

柵極

+關注

關注

1文章

184瀏覽量

21269

發布評論請先 登錄

工藝升級是否必要性,EUV和GAAFET技術解讀

三星推GAAFET技術 將基于它打造3nm芯片

三星將EUV與10nm工藝結合推出LPDDR5內存芯片

硬創早報:三星全球首秀3nm!電壓只需0.23V

臺積電為發展2nm制程竟計劃投入2300億!為的就是保全領先地位

臺積電:2nm工藝將使用GAAFET技術,預計2025年實現量產

臺積電2nm工藝最新消息 臺積電2nm芯片什么時候上市

臺積電2nm芯片計劃于2025年實現量產

臺積電2nm和3nm制程工藝

臺積電2nm芯片將采用GAAFET技術

臺積電2nm先進制程首次亮相

美國斷供“芯片之母”EDA,中國語音芯片或將陷入發展困境

SiGe與Si選擇性刻蝕技術

GAAFET,是什么技術?

GAAFET,是什么技術?

評論