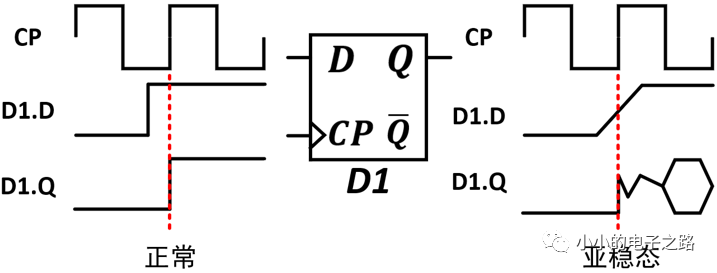

亞穩(wěn)態(tài)是指觸發(fā)器的輸入信號無法在規(guī)定時間內(nèi)達(dá)到一個確定的狀態(tài),導(dǎo)致輸出振蕩,最終會在某個不確定的時間產(chǎn)生不確定的輸出,可能是0,也可能是1,導(dǎo)致輸出結(jié)果不可靠。

1、亞穩(wěn)態(tài)產(chǎn)生原因

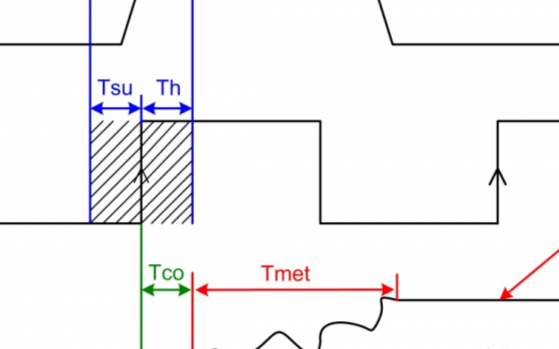

亞穩(wěn)態(tài)的產(chǎn)生是 輸入信號違背了觸發(fā)器的建立時間和保持時間導(dǎo)致的 。建立時間是指在時鐘邊沿到來之前輸入信號必須保持穩(wěn)定的時間。保持時間是指在時鐘邊沿到來之后數(shù)據(jù)必須保持穩(wěn)定的時間。輸入信號如果在這兩個時間段內(nèi)沒有保持穩(wěn)定,就將產(chǎn)生亞穩(wěn)態(tài)現(xiàn)象。

2、同步機(jī)制

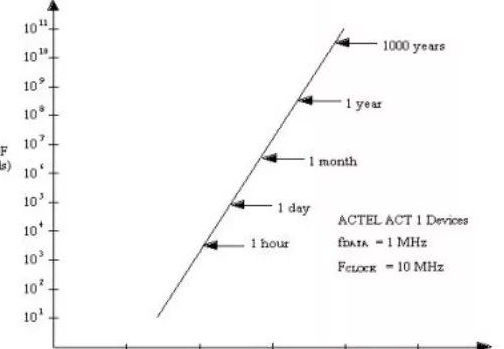

亞穩(wěn)態(tài)無法避免,只能通過一定方法阻止其向后級傳播,避免其對后級電路產(chǎn)生影響。主要方法有: 引入同步機(jī)制 、 采用響應(yīng)更快的觸發(fā)器 、降低時鐘頻率等。接下來介紹一下如何通過同步機(jī)制阻斷亞穩(wěn)態(tài)的傳播。

如下圖所示,如果觸發(fā)器出現(xiàn)亞穩(wěn)態(tài)現(xiàn)象,該電路將無法準(zhǔn)確檢測輸入信號是否出現(xiàn)上升沿。

(1)若D1.Q穩(wěn)定在低電平,能夠檢測出上升沿;

(2)若D1.Q穩(wěn)定在高電平,不能檢測出上升沿;

但是,如果采用兩個觸發(fā)器級聯(lián)的方式引入同步機(jī)制,情況就不一樣了,電路將準(zhǔn)確檢測輸入信號是否出現(xiàn)上升沿。

(3)若D1.Q穩(wěn)定在低電平,在輸入信號上升沿出現(xiàn)兩個時鐘周期后,檢測出上升沿;

(4)若D1.Q穩(wěn)定在高電平,在輸入信號上升沿出現(xiàn)一個時鐘周期后,檢測出上升沿。

總而言之,該電路始終能夠檢測出上升沿,只是時間問題。

-

時鐘頻率

+關(guān)注

關(guān)注

0文章

50瀏覽量

20624 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81612 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61895 -

亞穩(wěn)態(tài)

+關(guān)注

關(guān)注

0文章

47瀏覽量

13478 -

輸入信號

+關(guān)注

關(guān)注

0文章

472瀏覽量

12839

發(fā)布評論請先 登錄

減少亞穩(wěn)態(tài)導(dǎo)致錯誤,提高系統(tǒng)的MTBF

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

亞穩(wěn)態(tài)問題解析

在FPGA復(fù)位電路中產(chǎn)生亞穩(wěn)態(tài)的原因

FPGA--中復(fù)位電路產(chǎn)生亞穩(wěn)態(tài)的原因

在FPGA中,同步信號、異步信號和亞穩(wěn)態(tài)的理解

今日說“法”:讓FPGA設(shè)計中的亞穩(wěn)態(tài)“無處可逃”

一種消除異步電路亞穩(wěn)態(tài)的邏輯控制方法

FPGA中復(fù)位電路產(chǎn)生亞穩(wěn)態(tài)概述與理論分析

數(shù)字電路中何時會發(fā)生亞穩(wěn)態(tài)

亞穩(wěn)態(tài)產(chǎn)生原因、危害及消除方法

什么是亞穩(wěn)態(tài)?如何克服亞穩(wěn)態(tài)?

FPGA設(shè)計中的亞穩(wěn)態(tài)解析

數(shù)字電路中的亞穩(wěn)態(tài)產(chǎn)生原因

數(shù)字電路中的亞穩(wěn)態(tài)產(chǎn)生原因

評論