點(diǎn)擊上方“泰克科技” 關(guān)注我們!

點(diǎn)擊上方“泰克科技” 關(guān)注我們!■雙脈沖測(cè)試

雙脈沖測(cè)試中一個(gè)重要目標(biāo)是,準(zhǔn)確測(cè)量能量損耗。在示波器中進(jìn)行準(zhǔn)確的功率、能量測(cè)試,關(guān)鍵的一步是在電壓探頭和電流探頭之間進(jìn)行校準(zhǔn),消除時(shí)序偏差。

泰克今年推出的雙脈沖測(cè)試軟件(WBG-DPT)在4系、5系和6系示波器上均可使用,該軟件包括一種新的專為雙脈沖測(cè)試設(shè)計(jì)的消除時(shí)序偏差(deskew)的校準(zhǔn)技術(shù)。這種新的方法與傳統(tǒng)方法大有不同,測(cè)試速度顯著加快,縮短了測(cè)試時(shí)間。

該技術(shù)適用于使用場(chǎng)效應(yīng)晶體管或IGBT的功率轉(zhuǎn)換器。在本篇文章中,我們將使用FET術(shù)語,來使得描述簡單明了。

為什么要消除時(shí)序偏差(deskew)?

在設(shè)計(jì)任意一種功率變換器時(shí),都必須盡量減少開關(guān)過程中的能量損耗。這種能量損耗可以使用示波器進(jìn)行測(cè)量。一般方法是將同一時(shí)刻的電壓和電流采樣相乘,生成功率波形。

p(t) = v(t)*i(t)

由于功率波形表示隨時(shí)間變化的能量消耗,因此可以通過對(duì)功率波形進(jìn)行積分來確定能量:

E = ∫p(t)dt

要準(zhǔn)確測(cè)量能量損耗,電流和電壓波形的轉(zhuǎn)換應(yīng)在時(shí)間上保持一致。因此,為了準(zhǔn)確進(jìn)行能量損耗測(cè)量,設(shè)計(jì)者必須矯正測(cè)試夾具和探頭造成的延遲。

一般來講,在測(cè)試裝置上開始任何測(cè)量之前都要計(jì)算探頭之間的偏差。對(duì)于低電壓應(yīng)用,可以使用函數(shù)發(fā)生器和時(shí)序偏差校準(zhǔn)夾具(deskew夾具)(Tektronix P/N 067-1686-03)進(jìn)行校準(zhǔn)。但是,這種方法對(duì)于高電壓和大電流應(yīng)用而言,并非最佳選擇。

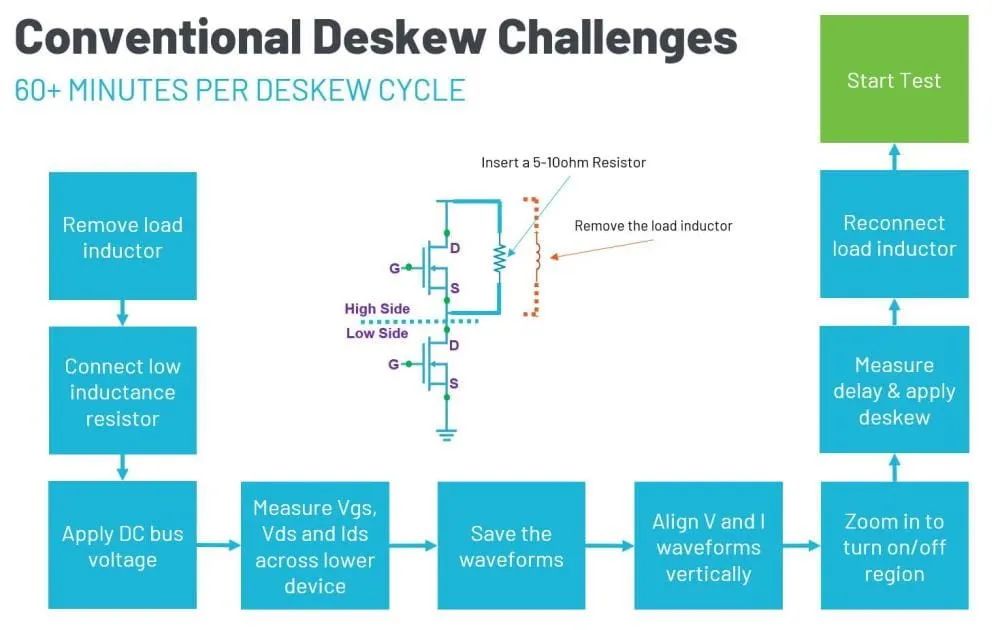

為了匹配更高功率下低壓漏-源極電壓(VDS)和漏極電流(ID)的測(cè)量,傳統(tǒng)技術(shù)需要重新布線測(cè)試裝置。這要求移除負(fù)載電感,并用電阻取而代之。接下來進(jìn)行測(cè)量,需要匹配VDS和ID測(cè)量值。這個(gè)過程可能需要一個(gè)小時(shí)或更長時(shí)間。

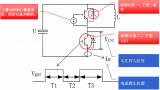

圖1. 傳統(tǒng)的deskew方法是移除負(fù)載電感,用電阻替代

一種新的時(shí)序偏差校準(zhǔn)(deskew)方法

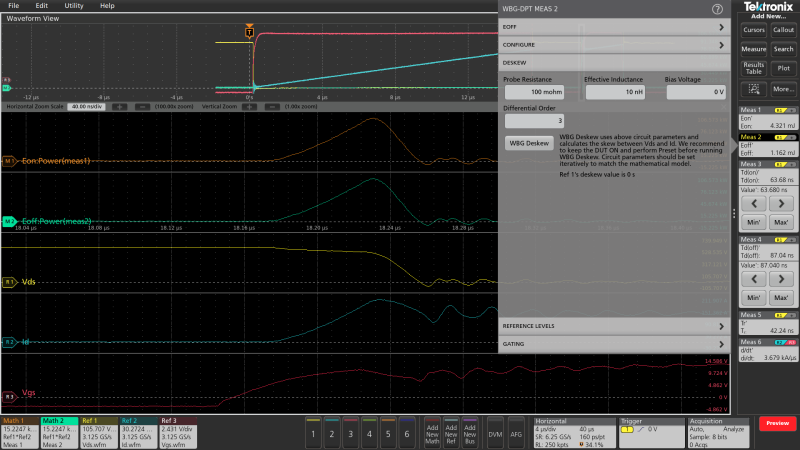

泰克WBG-DPT解決方案是業(yè)內(nèi)首創(chuàng)的基于軟件的時(shí)序偏差校準(zhǔn)(deskew)技術(shù),無需重新布線,只需在進(jìn)行雙脈沖測(cè)量后即可執(zhí)行。在新方法中,采集漏極電流(ID)用作參考波形。在導(dǎo)通期間,利用測(cè)試電路的參數(shù)模型計(jì)算出低壓側(cè)VDS對(duì)齊波形,其計(jì)算后的波形參考ID波形,相對(duì)于ID沒有時(shí)序偏移。消除時(shí)序偏差的算法確定計(jì)算出的VDS波形與測(cè)量出的VDS波形之間的時(shí)序偏差。然后將deskew校準(zhǔn)的數(shù)據(jù)修正到VDS測(cè)量通道。

圖2. 在新方法中,時(shí)序偏差校準(zhǔn)是在測(cè)試后進(jìn)行的,

參數(shù)在deskew菜單中設(shè)定

時(shí)序偏差校準(zhǔn)過程

如上所述,時(shí)序偏差校準(zhǔn)可在測(cè)量后進(jìn)行。在開始雙脈沖測(cè)試時(shí),無需擔(dān)心VDS和ID之間的偏差,隨后選擇deskew設(shè)置并提供以下參數(shù):

?探頭阻抗 - 在本文中假定為電流檢測(cè)電阻(CVR)或分流電阻

?有效"回路"電感

?偏置電壓(低壓側(cè)FET關(guān)斷時(shí)兩端的平均VDS)

?差分階數(shù)(模型用于平滑的濾波器階數(shù))

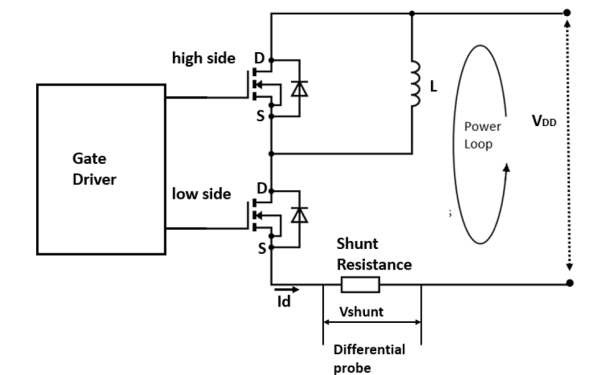

圖3. 用于建立VDS_low對(duì)齊波形的等效電路

該電路假定使用一個(gè)電流觀察電阻來測(cè)量ID

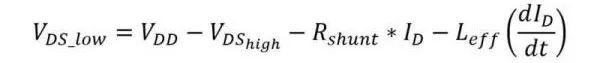

在deskew菜單中輸入的參數(shù)用于構(gòu)建VDS對(duì)應(yīng)波形。波形使用基爾霍夫電壓定律建立:

其中VDD - VDS_high表示電源軌電壓和高壓端場(chǎng)效應(yīng)晶體管FET上的壓降。需要注意,在開啟期間,由于VDD是固定的,而VDS_high是高壓端場(chǎng)效應(yīng)晶體管FET本體二極管上的電壓,所以這個(gè)量是恒定的。

■Rshunt是分流電阻

■ID是根據(jù)Rshunt上的壓降測(cè)得的漏極電流

■dID/dt 是測(cè)得的漏極電流變化率

■Leff是整個(gè)電源回路的有效電感

如上所述,在開啟期間,VDD-VDS_high實(shí)際上是恒定的。Rshunt和Leff也是恒定的。這意味著模擬的VDS_low走線波形是ID的函數(shù)。

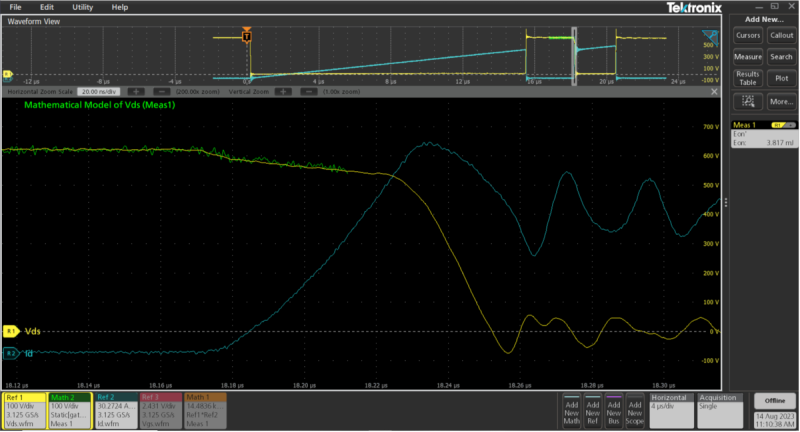

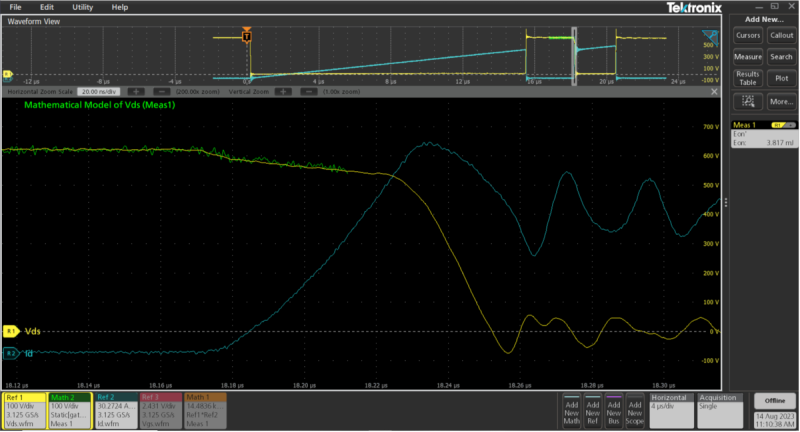

配置完參數(shù)后,用戶按下WBG的deskew按鈕。系統(tǒng)將根據(jù)指定的參數(shù)和漏極電流生成VDS的數(shù)學(xué)模型。該波形將顯示在屏幕上。

圖4. 根據(jù)ID計(jì)算出的VDS對(duì)齊波形與測(cè)量的VDS波形進(jìn)行比較。偏移是對(duì)齊波形和測(cè)量波形之間的時(shí)間差。計(jì)算出偏斜后,就可以從ID波形中去除偏斜

如上圖所示,有效電感Leff考慮到了整個(gè)環(huán)路的“疊加”。因此,Leff通常是未知的,而這個(gè)參數(shù)需要反復(fù)調(diào)整。簡單地將糾偏過程反復(fù)運(yùn)行,并對(duì)Leff進(jìn)行調(diào)整,直到計(jì)算出的對(duì)齊波形和測(cè)量出的VDS波形具有相同的形狀。如果計(jì)算出的VDS對(duì)齊波形與測(cè)量的VDS波形在形狀上存在差異,可以調(diào)整參數(shù)并再次運(yùn)行校準(zhǔn)時(shí)間偏差。

一旦參數(shù)設(shè)置準(zhǔn)確,對(duì)齊波形和測(cè)量波形將具有相同的形狀,系統(tǒng)就能確定并糾正偏斜。偏斜值顯示在Deskew設(shè)置中,并自動(dòng)應(yīng)用于連接VDS信號(hào)的通道。

這一新流程可以準(zhǔn)確地計(jì)算偏斜值,并將時(shí)序偏差校準(zhǔn)時(shí)間從一小時(shí)或更長時(shí)間縮短到5至10分鐘。

點(diǎn)擊閱讀原文,

了解更多雙脈沖測(cè)試知識(shí)!

欲知更多產(chǎn)品和應(yīng)用詳情,您還可以通過如下方式聯(lián)系我們:

網(wǎng)址:tek.com.cn

電話:400-820-5835(周一至周五900)

將您的靈感變?yōu)楝F(xiàn)實(shí)

我們提供專業(yè)的測(cè)量洞見信息,旨在幫助您提高績效以及將各種可能性轉(zhuǎn)化為現(xiàn)實(shí)。

泰克設(shè)計(jì)和制造能夠幫助您測(cè)試和測(cè)量各種解決方案,從而突破復(fù)雜性的層層壁壘,加快您的全局創(chuàng)新步伐。我們攜手共進(jìn),一定能夠幫助各級(jí)工程師更方便、更快速、更準(zhǔn)確地創(chuàng)造和實(shí)現(xiàn)技術(shù)進(jìn)步。

掃碼添加“泰克工程師小助手”

立享1對(duì)1專屬服務(wù)!

點(diǎn)擊“閱讀原文”了解更多!

原文標(biāo)題:一種新的軟件時(shí)序偏差校準(zhǔn)方法,加速雙脈沖測(cè)試進(jìn)程!

文章出處:【微信公眾號(hào):泰克科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

泰克科技

+關(guān)注

關(guān)注

2文章

198瀏覽量

19845

原文標(biāo)題:一種新的軟件時(shí)序偏差校準(zhǔn)方法,加速雙脈沖測(cè)試進(jìn)程!

文章出處:【微信號(hào):泰克科技,微信公眾號(hào):泰克科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

泰克科技功率器件雙脈沖測(cè)試解決方案

EXR小故事 – 雙脈沖測(cè)試雙管齊下

雙極性脈沖恒流源:高效測(cè)試解決方案

SiC碳化硅MOSFET功率器件雙脈沖測(cè)試方法介紹

IGBT雙脈沖測(cè)試原理和步驟

絕緣電阻測(cè)試儀的校準(zhǔn)方法 絕緣電阻測(cè)試儀的工作原理

雙色led燈突然一種顏色不亮的原因及解決辦法

寬帶隙功率半導(dǎo)體雙脈沖測(cè)試解決方案

時(shí)序邏輯電路的五種描述方法

TS RadiMation測(cè)試軟件如何在脈沖抗擾度測(cè)試中發(fā)揮作用?

rup是一種什么模型

電源時(shí)序器的原理及使用方法是什么

采用羅氏線圈來測(cè)試脈沖磁場(chǎng)的方法

步入式恒溫恒濕試驗(yàn)房的校準(zhǔn)步驟和方法

一種新的軟件時(shí)序偏差校準(zhǔn)方法,加速雙脈沖測(cè)試進(jìn)程!

一種新的軟件時(shí)序偏差校準(zhǔn)方法,加速雙脈沖測(cè)試進(jìn)程!

評(píng)論