Cu-Clip技術

Cu-Clip技術,它可以應用在很多模塊封裝形式當中。它的特點有:降低寄生電感和電阻,增加載流能力,相應地提高可靠性,以及靈活的形狀設計。當芯片面積越來越小(比如IGBT 7 和SiC),這限制了常規(guī)綁定線的數(shù)量,但Cu-Clip技術相應地緩解了這方面的問題。

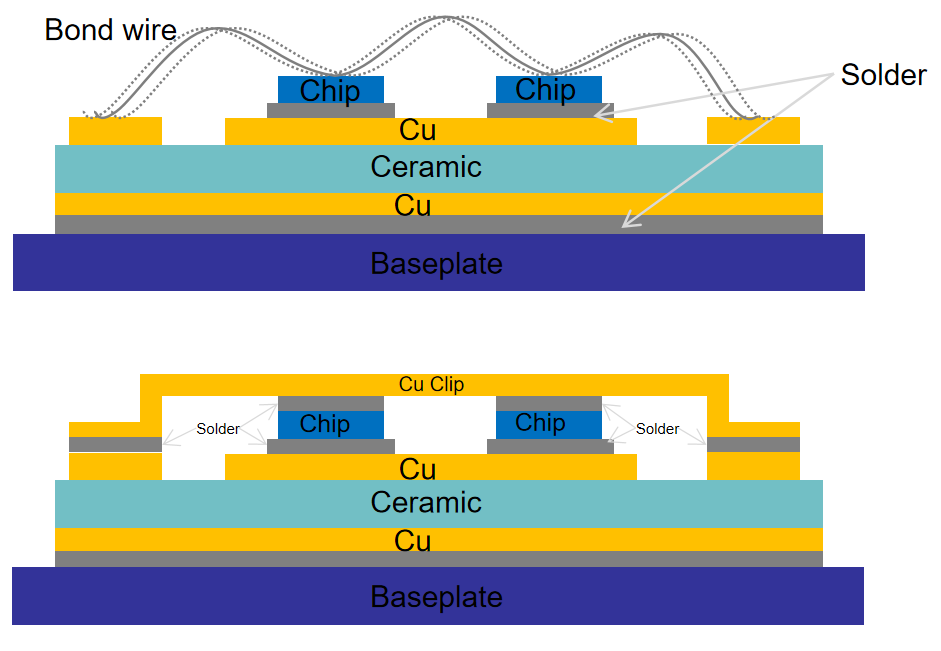

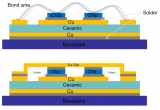

上面是綁定線和Cu-Clip的簡單示意圖。

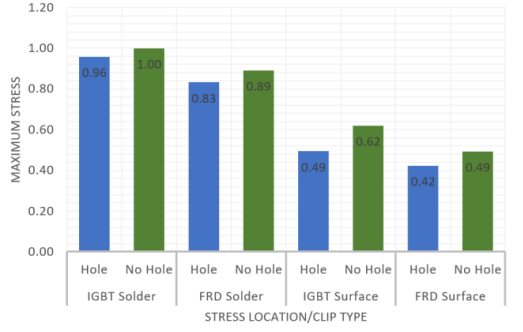

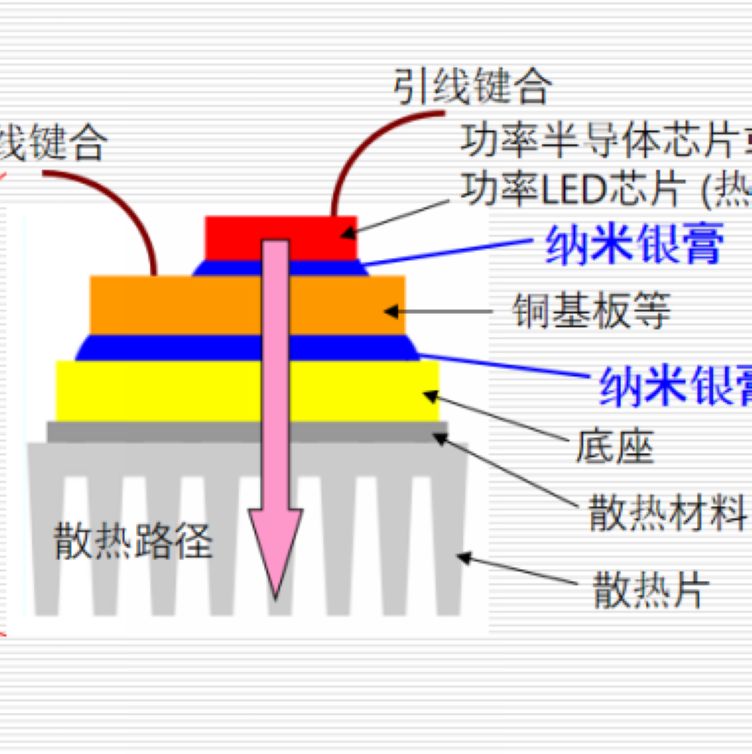

功率半導體器件結構可以分為好多層,其中影響長期可靠性的因素是CTE(熱膨脹系數(shù))的匹配,CTE失配而引起的應力對可靠性產(chǎn)生很大的影響,鋁綁定線脫落就是其中較為典型的例子。這是鋁綁定線和半導體材料之間CTE(鋁:23ppm/K,Si:3ppm/K)差異較大導致的。而銅的CTE約為16.5ppm/K,相應地可以減輕CTE失配帶來的熱機械應力問題,同樣又可以降低回路電感和電阻。

Cu-Clip粘接到其他表面的方式也有很多種,包括傳統(tǒng)的焊接,銀燒結以及銅燒結技術。當然這其中又牽扯到焊料,燒結工藝等,這些又都是復雜且不斷發(fā)展的領域。

就像綁定線有著材料、長度、直徑、彎曲度等等因素的考量,Cu-Clip也相應的會有厚度,材料,形狀等等考量。

Clip的厚度

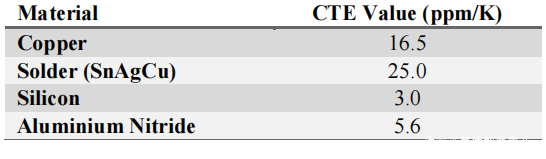

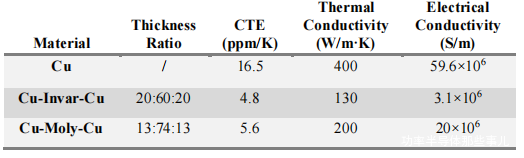

采用AlN基板,三芯片(IGBT和FRD)并聯(lián),焊料采用SnAgCu,來比較Clip厚度0.5mm和1.5mm在一定溫度差下的熱機械應力,檢測位置為Clip和芯片之間的焊接層,以及芯片表面。下面是材料CTE的參數(shù):

進行了歸一化處理,我們可以看到,使用較薄的Clip,連接的位置應力會更小,但滿足必要的載流能力的同時,盡量使用較薄的Clip。

應力緩解

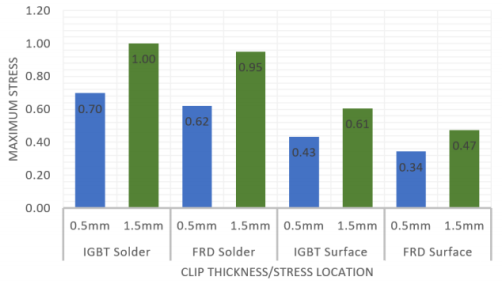

上面的模塊圖片中,我們可以看到Clip上有開孔,主要便是為了緩解應力,而相比于不開孔,應力具體會怎么樣呢?從下面的仿真結果我們可以看到。

結果顯然,可以通過開孔來緩解應力,但孔的形狀大小和位置又有所考究,這需要我們結合實際來具體設計完善的。

Clip材料

這里,作者提出了兩種材料,一個上面說到的CMC,一個是CIC,Invar是一種鎳鐵合金,以低CTE而聞名,下面是它們的相關參數(shù):

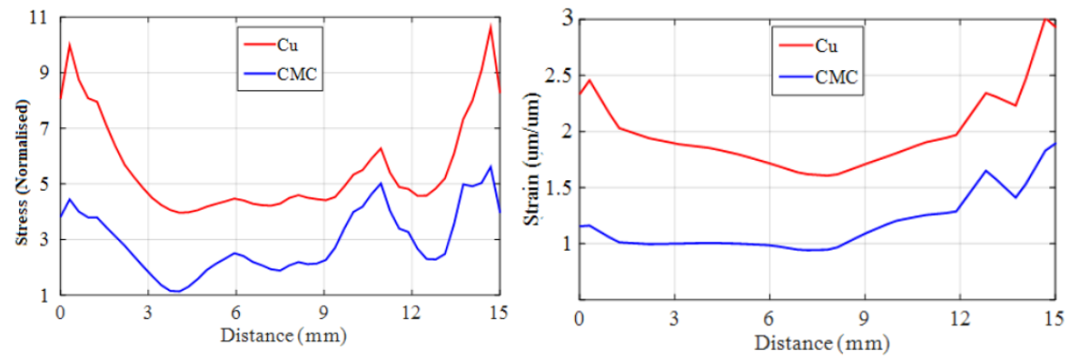

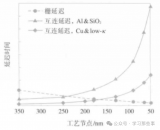

但是由于CIC的導電率較低,雖然CTE和Si更為接近,但是溫升卻很高,并不是一個理想的Clip材料,所以這里作者只比較了純銅和CMC。

從相同芯片表面的應力和應變曲線來看,CMC由于和Si較小的CTE差異而產(chǎn)生更小的應力。同時我們可以看到最大的應力和應變出現(xiàn)在芯片邊緣位置,所以又回到上一個問題,緩解應力的開孔放在和芯片接觸的邊緣位置會更好一些。

審核編輯:劉清

-

IGBT

+關注

關注

1277文章

4027瀏覽量

253482 -

CMC

+關注

關注

0文章

34瀏覽量

16965 -

寄生電感

+關注

關注

1文章

159瀏覽量

14833 -

功率半導體

+關注

關注

23文章

1281瀏覽量

43857

原文標題:Cu-Clip互連技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

AL-CU互連導線側壁孔洞形成機理及改進方法

光互連技術

光互連技術的研究進展

光互連技術發(fā)展面臨的難點

光互連技術的展望

直流和脈沖電鍍Cu互連線的性能比較

什么是UVLED點光源及其特點和應用有哪些呢?

什么是 Cu clip 封裝

Cu-Cu Hybrid Bonding技術在先進3D集成中的應用

揭秘Cu Clip封裝:如何助力半導體芯片飛躍

Cu-Clip互連技術有哪些特點呢?

Cu-Clip互連技術有哪些特點呢?

評論