AWorksLP 對外設進行了高度抽象化,為同一類外設提供了相同的接口,應用程序可以輕松跨平臺。本文以MR6750平臺為例,介紹AWorksLP 雙核調試的基本用法。

簡介MR6750 雙核是集成了兩個RISC-V處理器,是兩個完全獨立的CPU,故HPM雙核工程是Core0工程和Core1工程兩個獨立的工程。因此HPM雙核工程編譯,其實是兩個獨立的單核工程的編譯。用戶只需要建立core0和core1的各自工程編譯調試即可。 ?多核調試

?多核調試

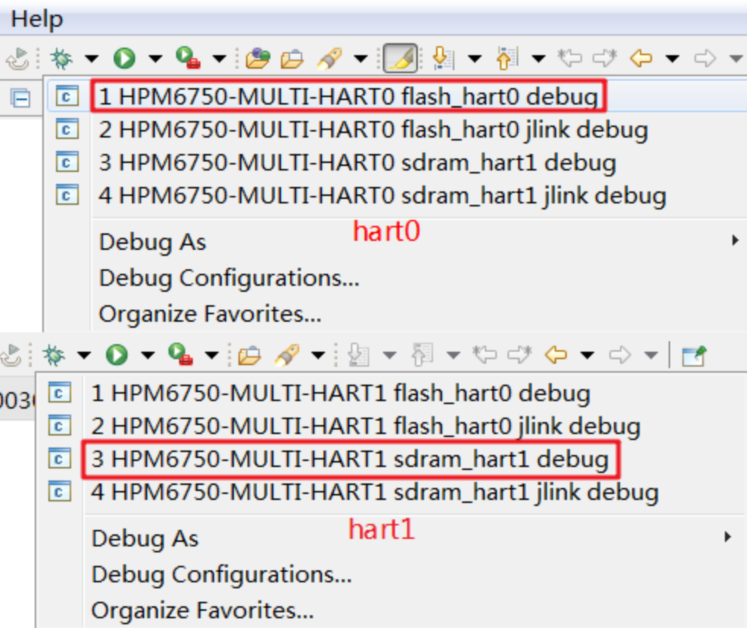

1. 修改默認工程配置

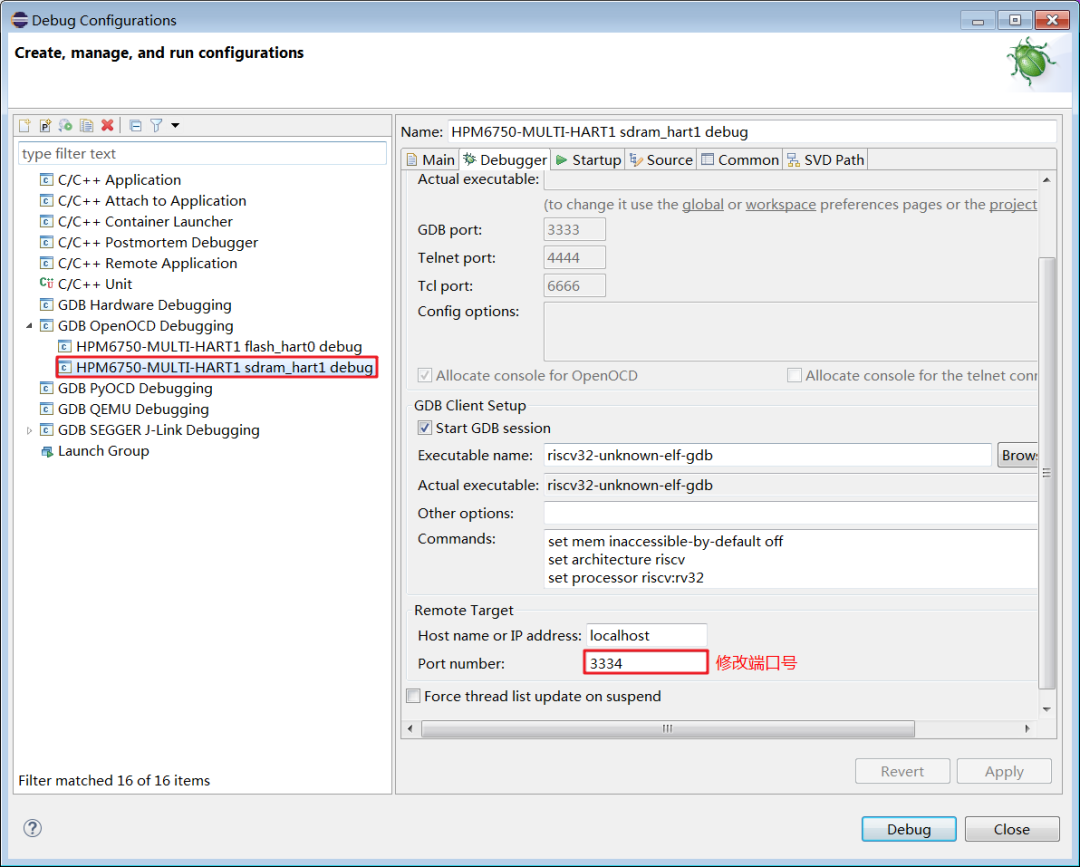

修改hart1工程OpenOCD的調試配置中的端口號。

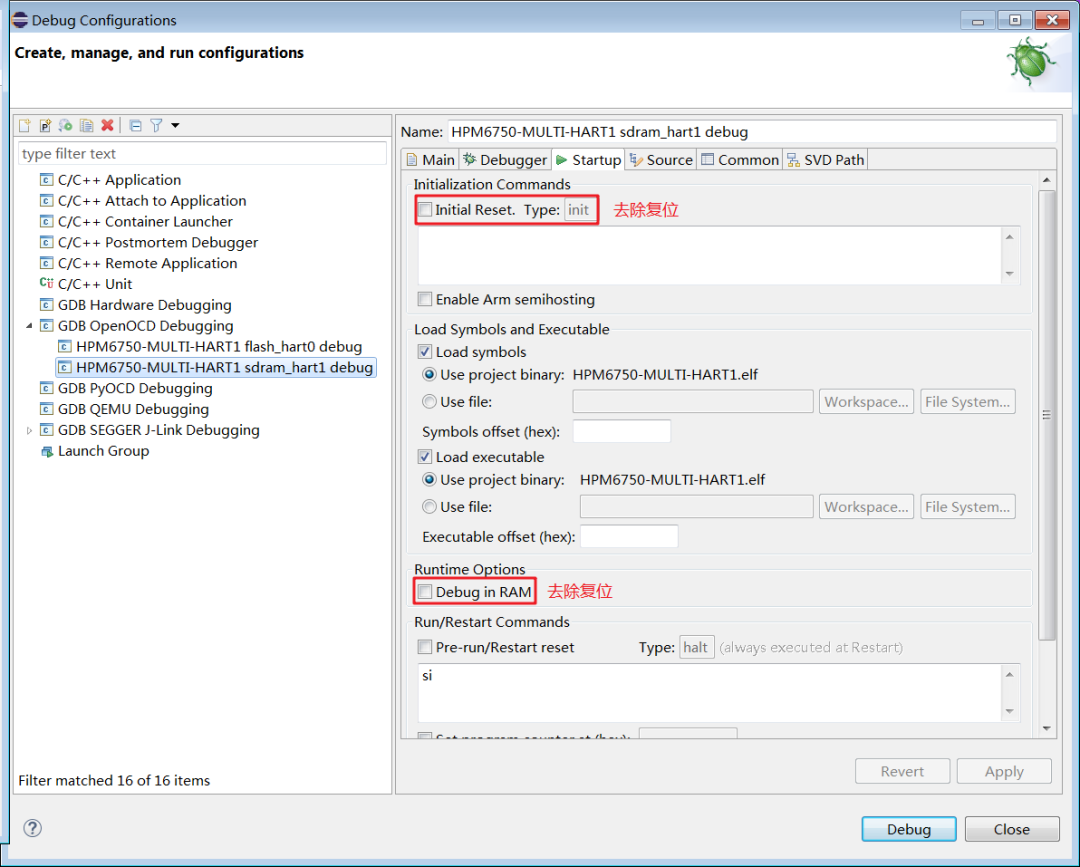

圖1修改端口號在Startup配置欄中去除復位選項。

圖2去除復位選項2. OpenOCD調試

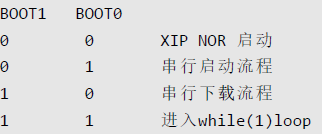

在多核調試前建議將啟動方式設置為串行啟動流程或者串行下載流程。

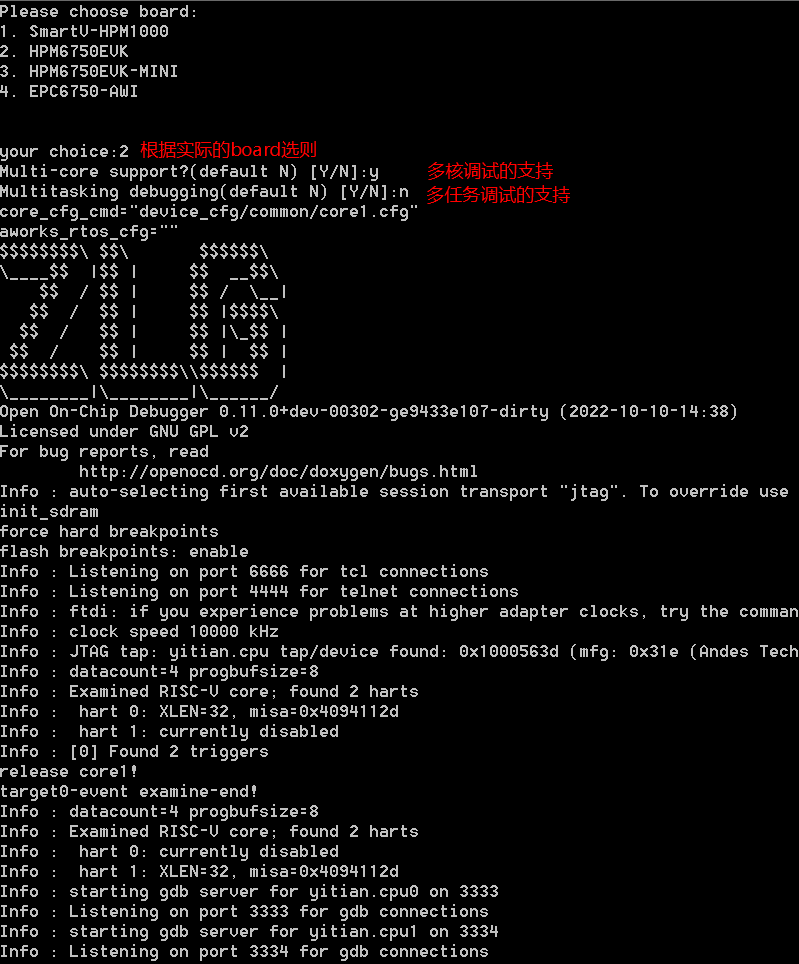

圖3啟動方式多核調試下會分配兩個gdb 端口,分別是3333 與3334 分別對應hart0與hart1 ,端口配置參考4.1小節。

圖3啟動方式多核調試下會分配兩個gdb 端口,分別是3333 與3334 分別對應hart0與hart1 ,端口配置參考4.1小節。 圖4 OpenOCD調試

圖4 OpenOCD調試

先下載hart0的固件,再下載hart1 的固件。注意順序不能錯。

注: 在調試狀態下,hart0 不會將hart1 的固件加載到相應的內存上,所以這里需要分別下載。

圖5OpenOCD下載

圖5OpenOCD下載

-

處理器

+關注

關注

68文章

19813瀏覽量

233615 -

cpu

+關注

關注

68文章

11040瀏覽量

216042 -

調試

+關注

關注

7文章

608瀏覽量

34531 -

編譯

+關注

關注

0文章

676瀏覽量

33761

發布評論請先 登錄

STM32H745XIH6不能進行雙核調試,CM4不能進行在線調試怎么解決?

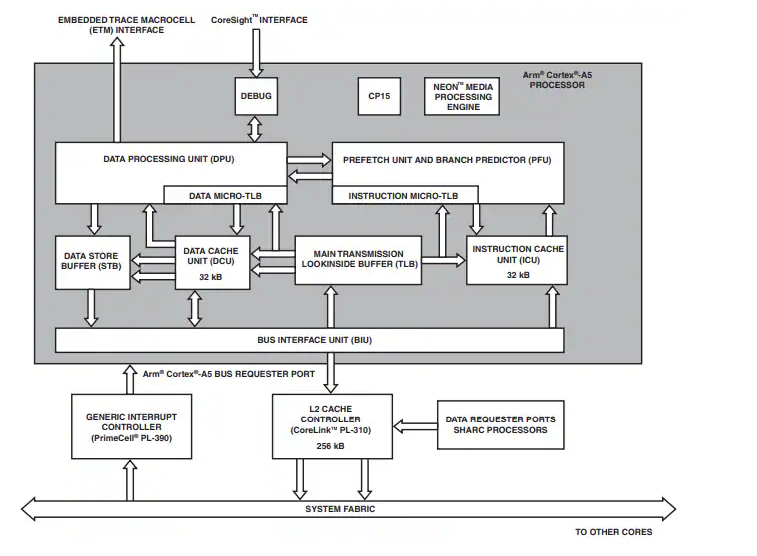

Analog Devices Inc. ADSP-SC592 SHARC+?雙核DSP數據手冊

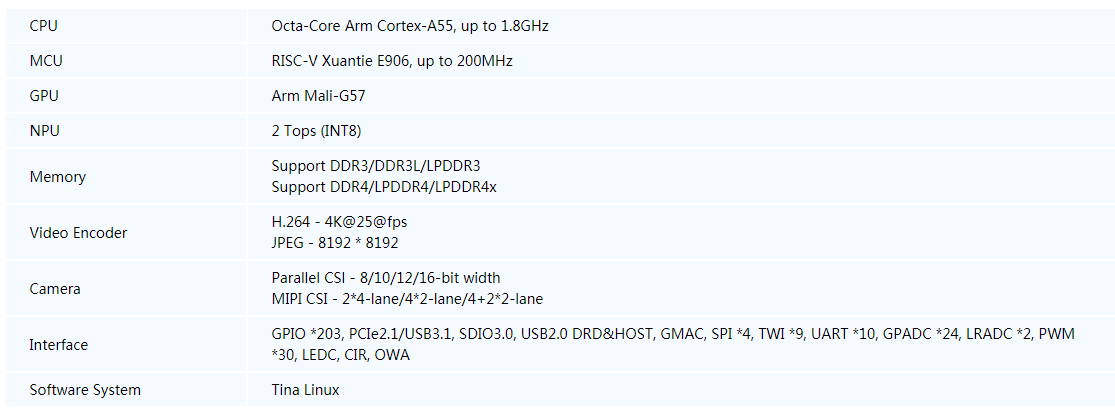

全志科技機器人專用芯片MR527與MR813特性概述

雙核鎖步技術在汽車芯片軟錯誤防護中的應用詳解

STM32H745的FreeRTOS是單核工作還是雙核工作?

RK3036:高效能雙核處理器詳解

全志T113雙核異構處理器的使用基于Tina Linux5.0——異構雙核通信驗證

在FPGA里面例化了8個jesd204B的ip核同步接收8塊AFE芯片的信號,怎么連接設備時鐘和sysref到AFE和FPGA?

HPM6750 Bootloader設計

雙核dsp和單核dsp的區別

MCUXpresso IDE下在線聯合調試雙核MCU工程的三種方法

AWorksLP 樣例詳解(MR6750)——雙核調試

AWorksLP 樣例詳解(MR6750)——雙核調試

評論