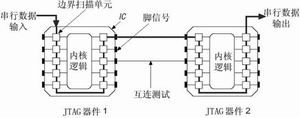

上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應用,演示了TopJTAG Probe軟件的應用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應用,兩者幾乎是一樣。

1. 獲取芯片的BSDL文件

FPGA的BSDL文件獲取方式,可以參考之前的文章:BSDL文件獲取。 以Xilinx Kintex-7系列FPGA XC7K325T為例,可以在BSDL Library網站獲取,或者在ISE、Vivado的安裝目錄獲取,

D:ProgramXilinx14.7ISE_DSISEkintex7data D:ProgramXilinxVivadoVivado2018.3ids_liteISEkintex7data

2. 硬件連接

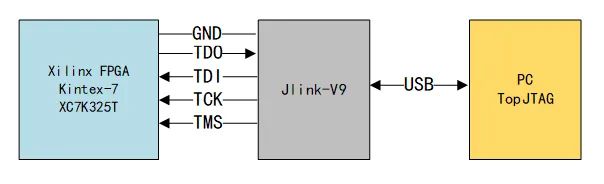

首先需要準備好以下硬件:

JTAG調試器,如JLink V9標準版

一塊FPGA板子,如Xilinx XC7K325T

Xilinx的JTAG接口和Jlink的JTAG接口線序不一致,需要使用單獨的杜邦線分別連接TCK、TMS、TDI、TDO和VREF、GND信號。

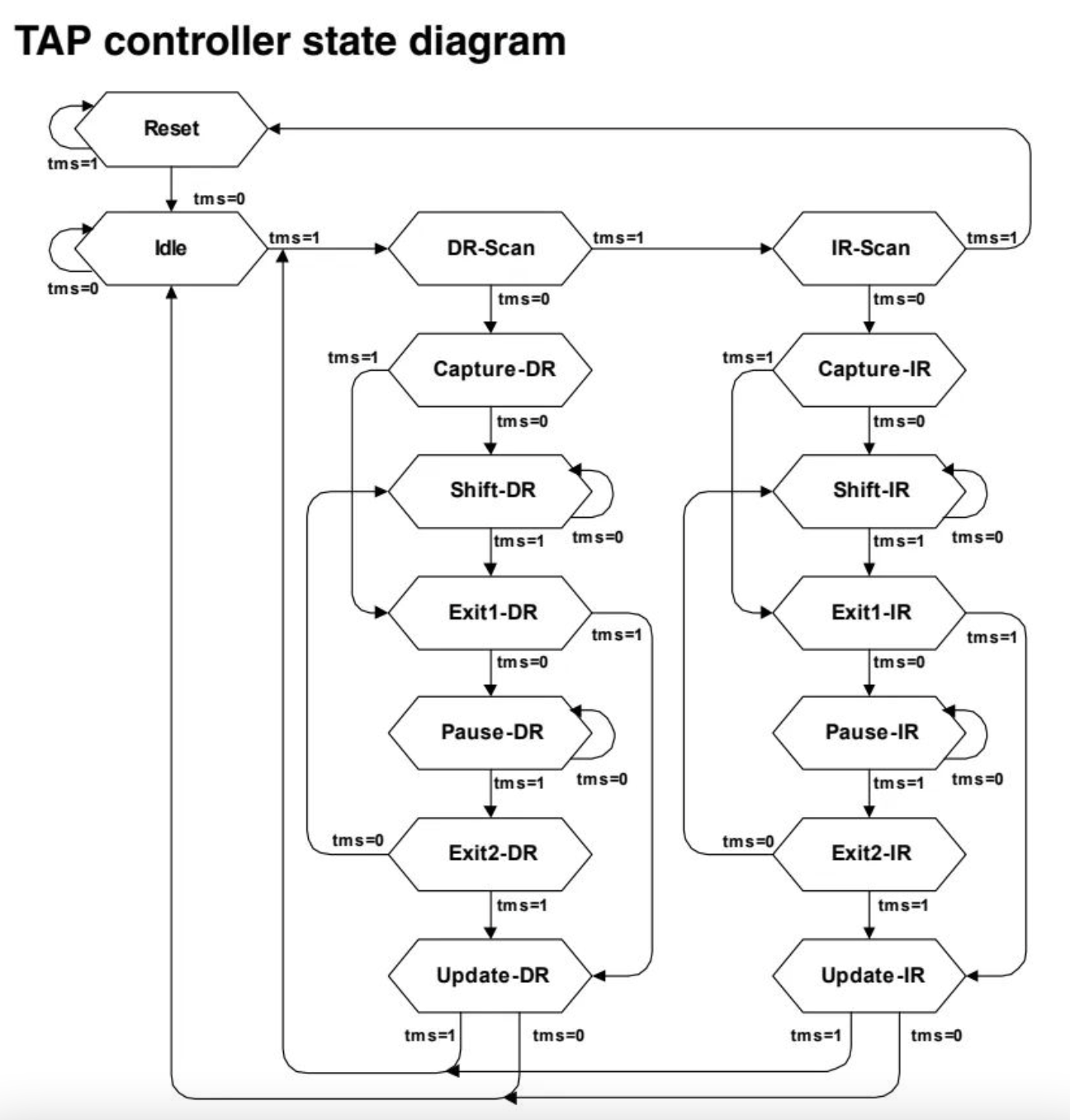

3. 邊界掃描測試

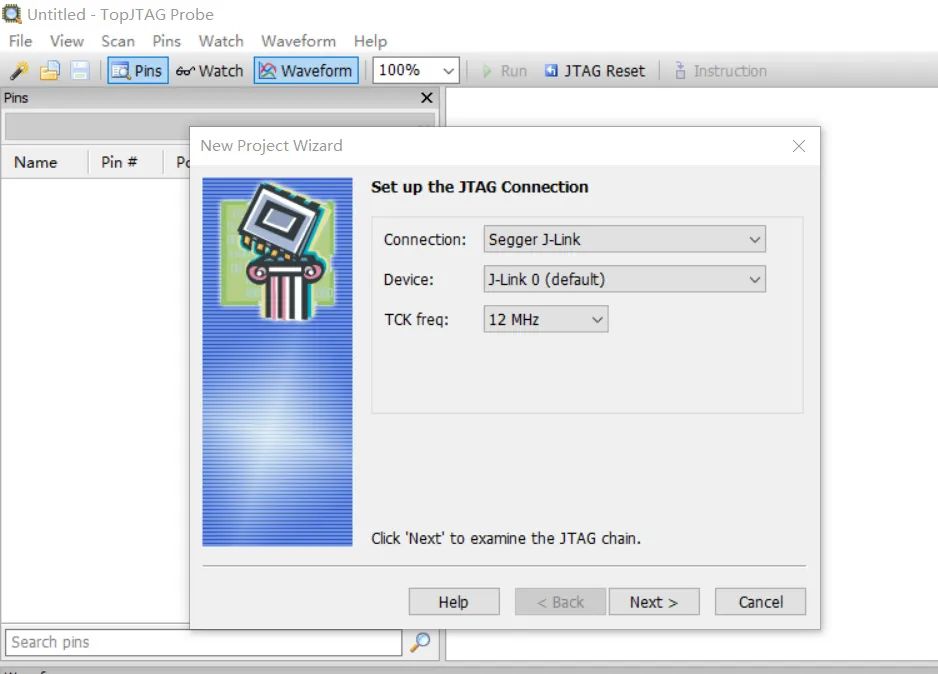

打開TopJTAG新建工程,選擇JTAG設備為JLink

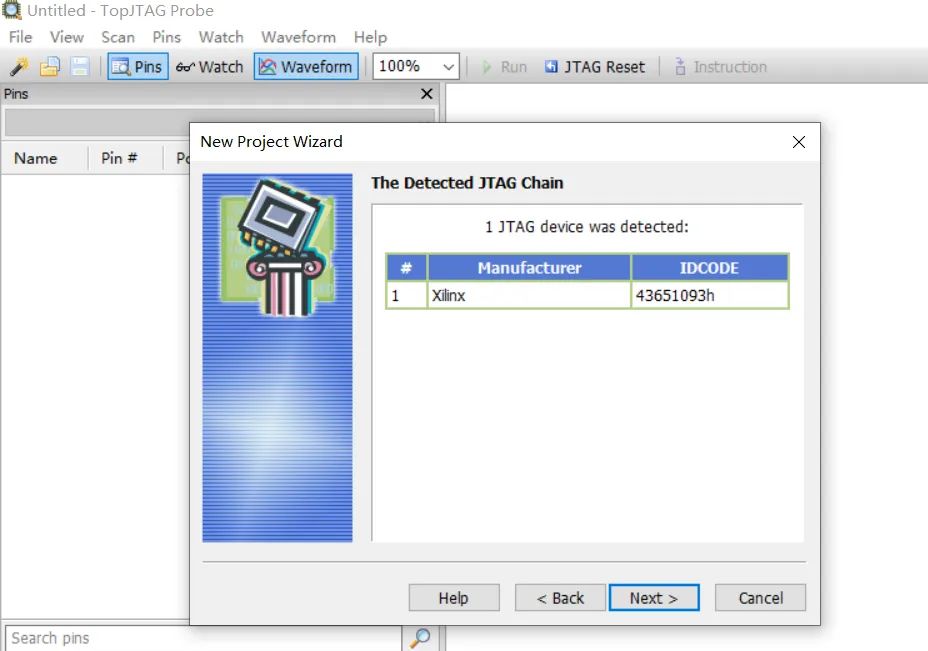

如果連接正常,會顯示當前連接芯片的IDCODE

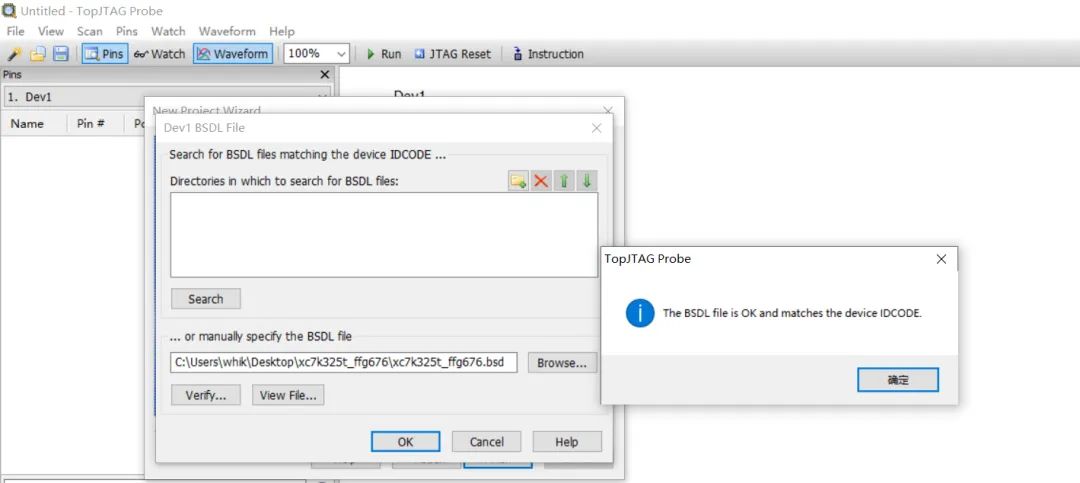

指定BSDL文件路徑,并進行IDCODE校驗。

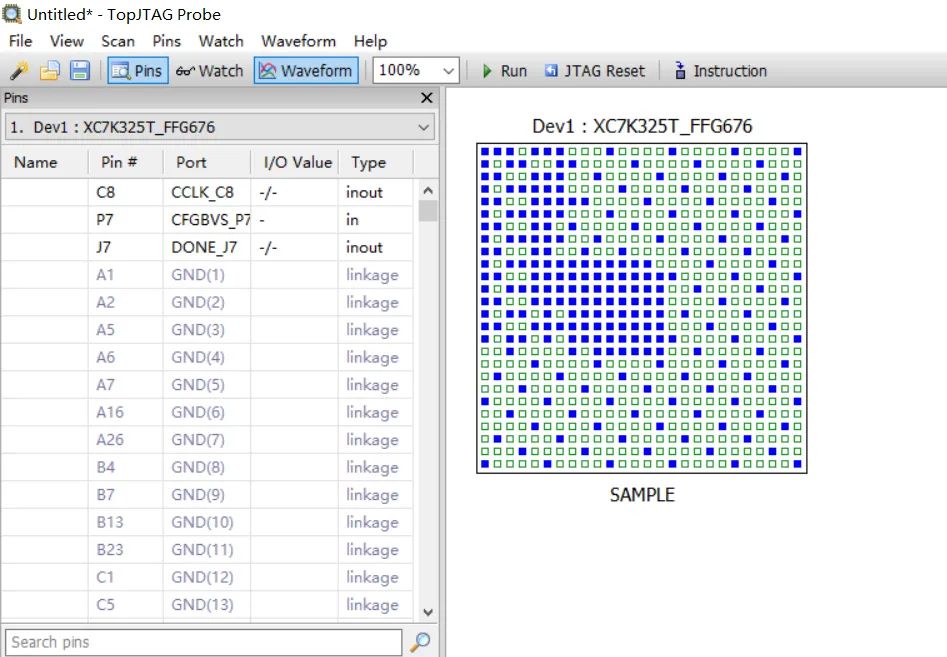

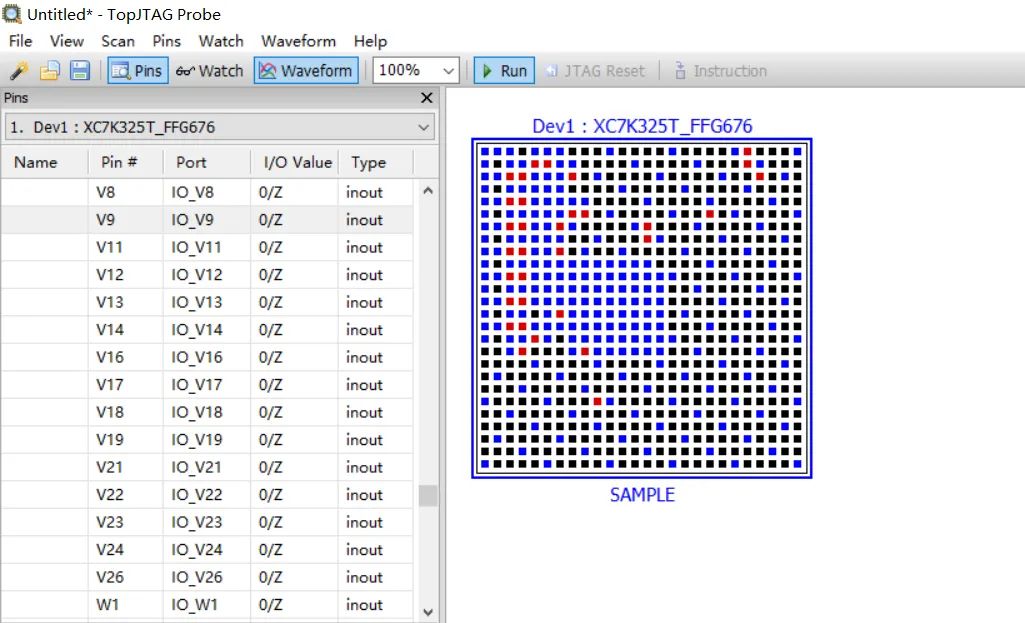

初始狀態為stop狀態,

初始默認為Sample狀態,點擊RUN按鈕,就可以看到所有管腳的實時狀態,黑色的是電源管腳,黑色的是高電平,藍色的是低電平。閃爍的說明當前為高低電平翻轉狀態。

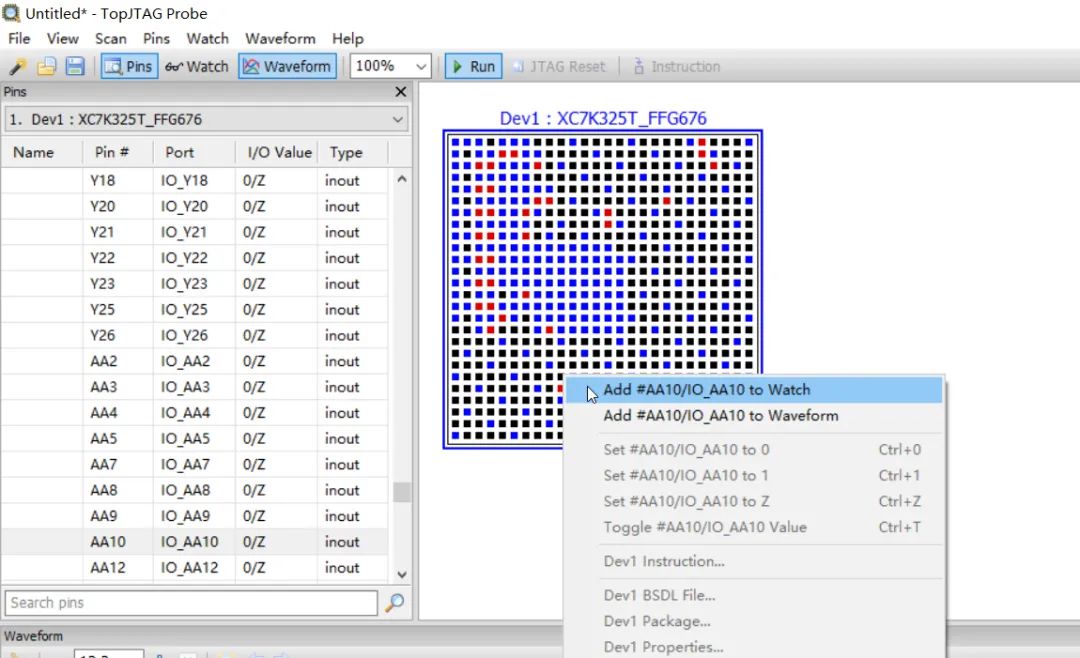

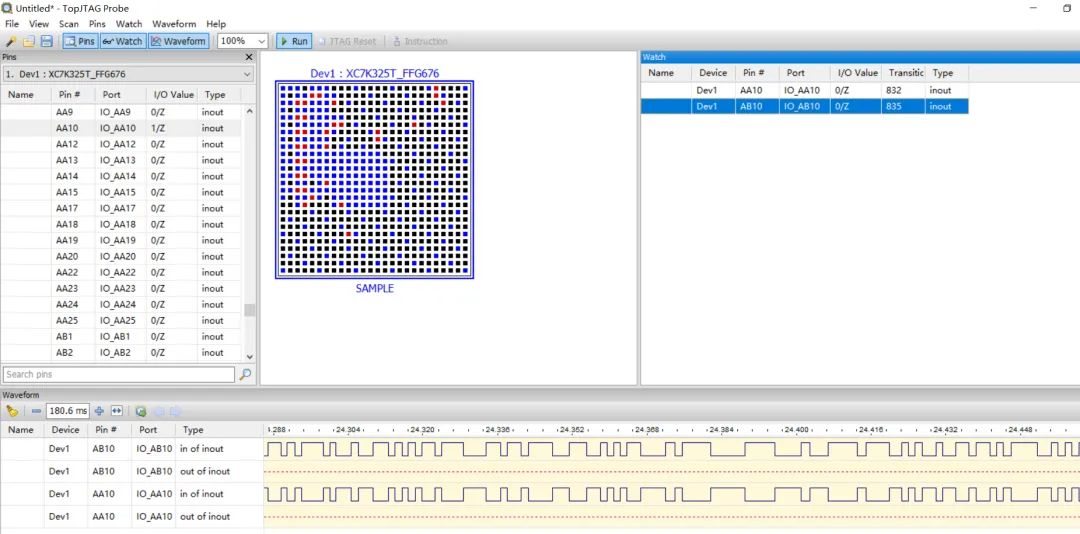

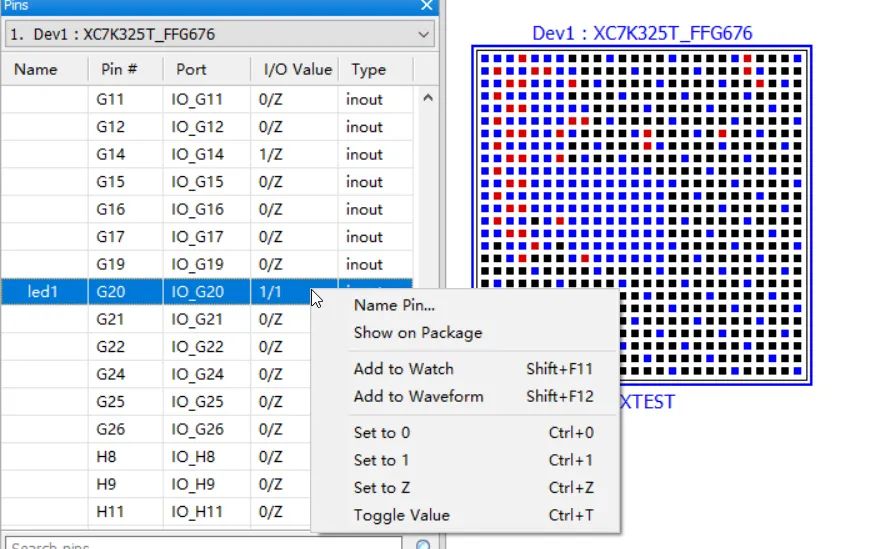

在左側Pins窗口或右側芯片視圖,選擇一個芯片管腳,右鍵,可以選擇添加到Watch窗口或Waveform窗口

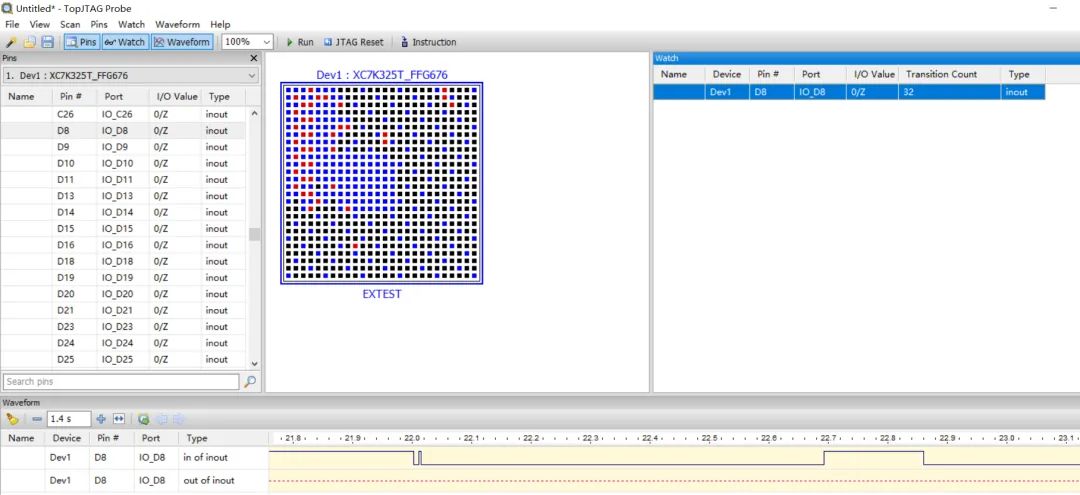

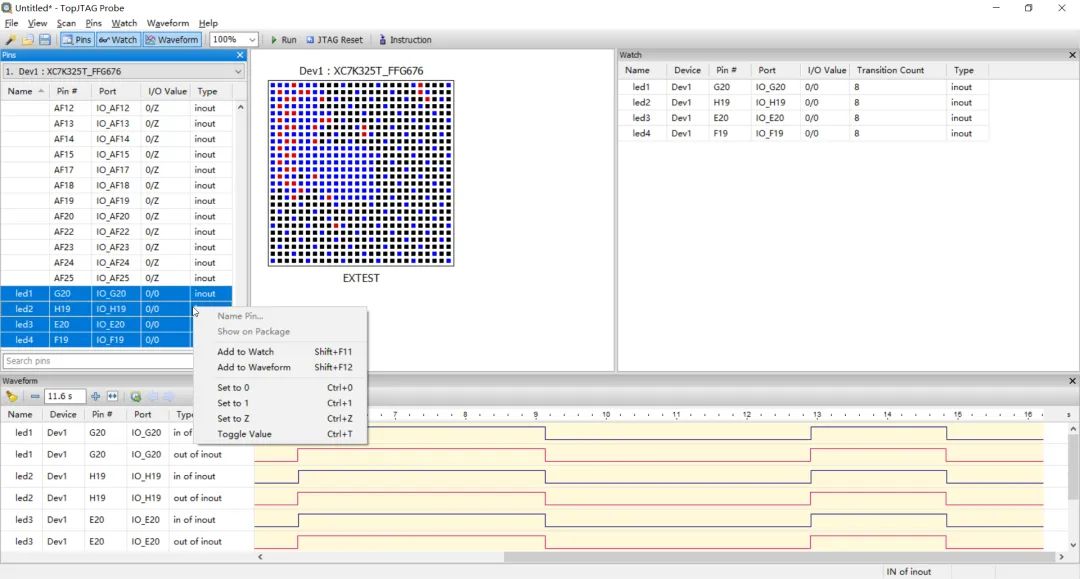

Watch窗口可以看到管腳實時狀態,并且可以統計電平翻轉的次數,Waveform窗口可以顯示實時的波形。

Waveform支持放大、縮小、暫停等基本操作。

Pins窗口,選擇一個管腳右鍵之后,可以進行命名,輸出高、低電平或高阻狀態。

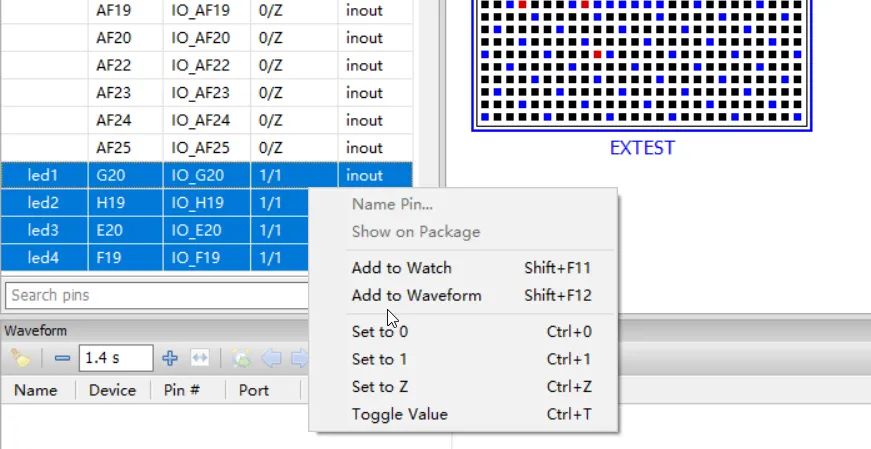

支持多選之后,批量控制電平狀態

支持多選之后,批量添加到Waveform窗口

4. 總結

和單片機不同,大多數FPGA芯片都是BGA封裝的,管腳個數從200至1000不等,這也就意味著需要多層PCB來進行硬件設計,密集的引腳和PCB的內層走線,會導致故障的排查越來越困難,通過邊界掃描,可以方便、快捷的判斷出故障點,在產品研發、生產、測試階段可以大大提高效率。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1644文章

22009瀏覽量

616591 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124807 -

JTAG

+關注

關注

6文章

403瀏覽量

73116 -

STM32F103

+關注

關注

33文章

483瀏覽量

65317 -

邊界掃描

+關注

關注

1文章

32瀏覽量

15164

原文標題:強大的JTAG邊界掃描5-FPGA邊界掃描應用

文章出處:【微信號:mcu149,微信公眾號:電子電路開發學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA邊界掃描模式可以串接兩個FPGA嗎

邊界掃描測試技術介紹

VXI邊界掃描模塊接口電路的設計

應用于FPGA的邊界掃描設計

邊界掃描與電路板測試技術

基于USB總線的邊界掃描測試系統

簡述BSDL邊界掃描語言,BSDL邊界掃描語言的應用

邊界掃描測試的基本原理及其測試系統的設計

邊界掃描技術的詳細資料描述

JTAG(四) 邊界掃描測試技術

基于Xilinx FPGA的邊界掃描應用

基于Xilinx FPGA的邊界掃描應用

評論