什么引入interface?

將設計和驗證從邏輯上和時間上分開,使得兩個小組可以相對獨立;

IC 設計的復雜度逐漸增加,模塊之間的連接也逐漸復雜,傳統的 Verilog信號連接方式代碼量太大,容易出錯,且不易于復用。

Interface的優勢

簡潔:

1、使用 Interface 在驗證中添加、刪除和修改信號時只需要修改 Interface 和使用該 Interface 的模塊,怎么理解?

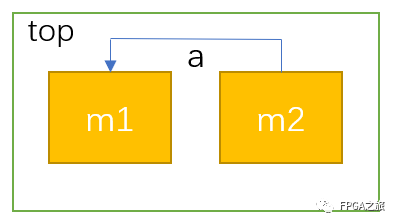

如圖所示:頂層模塊top例化了模塊m1和m2,a信號從m2經過頂層模塊到m1。假設現需將信號a修改為b,不使用接口的情況下,m1、m2及top模塊都應該做出相應的修改;若使用接口,top例化的是接口,接口內的信號修改只需要修改m1、m2相關部分即可。

2、兩個塊之間有兩個以上的信號連接,并且使用特定的協議時,使用接口更利于復用。

軟硬件域的橋梁:

Interface 是硬件域( module、設計中使用)和軟件域( class、驗證環境中使用)交互的唯一方式。

定義要點

Interface 的定義與 Module 類似,可以參考 Module 的定義方法;由于接口直接與DUT打交道,因此變量建議聲明為四值邏輯logic;同時為了防止驗證環境帶來的競爭問題,驅動硬件的信號應使用非阻塞賦值;Interface端口列表中只需要定義時鐘、復位等公共信號,或者不定義任何端口信號。

使用示例

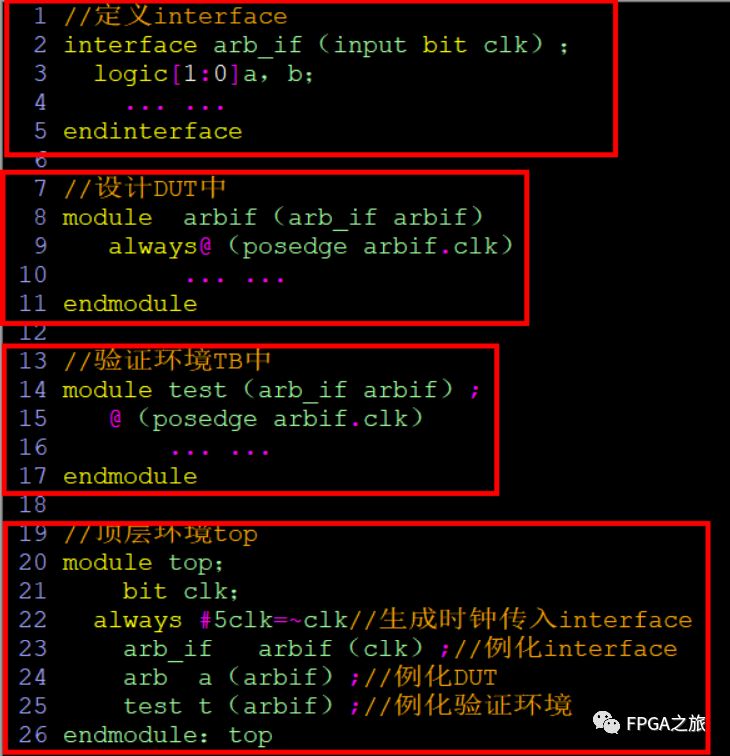

首先定義interface,然后在頂層例化后作為module的端口列表分別傳入DUT和TB中。

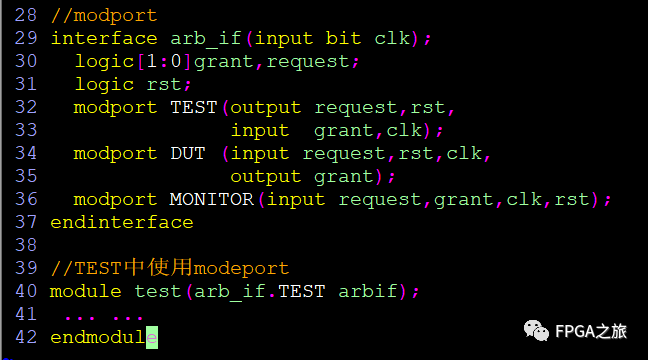

接口中的modport

前一個例子中使用了點對點無信號方向的連接方式。在使用該端口的原始網單里包含了方向信息,編譯器依次來檢查連線錯誤。也可以通過modport來進一步限定信號傳輸的方向,避免端口連接的錯誤。

需要注意的是modport中的input和output方向是調用該modport模塊的輸入輸出方向,比如TEST的modport內聲明的方向,就是調用它的test模塊輸入輸出。

事實上modport在驗證環境中使用并不多,因為下文提到的不但clocking塊包含了modport的方向信息,同時clocking塊也可作為同步信號的驅動。

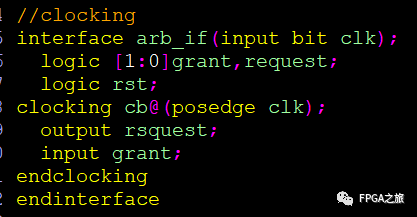

接口中的clocking塊

clocking 塊,用來對同步信號進行采樣和驅動,可以避免設計和驗證的競爭。clocking block需要指定一個觸發時鐘,比如posedge clk、negedge clk。

同若驗證環境中需要同步驅動,利用“arb_if.cb.*”的方式利用clocking塊中的信號進行驅動即可。

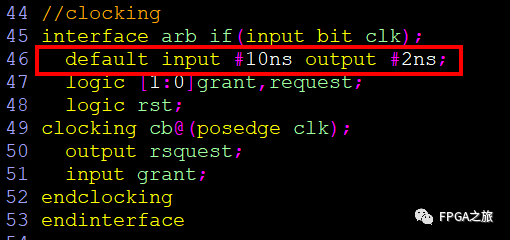

同時可以為clocking塊中信號設置建立和保持時間,若未設置建立時間或保持時間時則會默認在clocking事件前1step輸入采樣,在事件后#0對輸出驅動。

標注的語句表示在時鐘上升沿前10ns進行采樣,在時鐘上升沿2ns后進行驅動。怎么理解?事實上這個步驟主要是為了模擬實際的硬件行為,感興趣的可以自己畫幾級觸發器來分析,TB對DUT的驅動一側相當于DUT的上一級觸發器,采樣DUT數據一側的TB相當于DUT的下一級寄存器。

幾點注意:clocking不是interface獨有的,module、program也可以聲明clocking模塊;clocking中列舉的信號都是由interface、module、program等聲明了clocking的模塊定義的,cloking自身不聲明信號;一個interface中可以定義多個clocking,同一個變量可以在多個clocking塊中被應用,且可以聲明不同的輸入輸出方向。

完結。

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8952瀏覽量

153223 -

IC設計

+關注

關注

38文章

1349瀏覽量

105276 -

Verilog

+關注

關注

29文章

1366瀏覽量

111869 -

Interface

+關注

關注

0文章

103瀏覽量

38993

原文標題:Interface in systemverilog

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

串行外設接口(Serial Peripheral Interface Master) Xilinx提供

合并SLaveFIFO接口和GPIFtoStAGGE FX3固件示例出現錯誤:未定義引用

帶LCD的PIC接口示例代碼

可以獲得Cyconsole的EZ-USB接口示例項目嗎?

SCSI接口的具體使用和優勢

Gowin DDR Memory Interface IP參考設計

什么是BRI (Basic Rate Interface)

DVI接口端子定義

IEEE1149.1標準JTAG接口與ISP接口,ISP interface

AHB Slave Decoder和AHB Slave Interface接口的使用說明

開發接口協議DIA應用場景示例

C#-Interface接口實現

代碼的黑盒測試(下)|?庫接口測試Library Interface Testing

Interface接口的優勢和使用示例

Interface接口的優勢和使用示例

評論