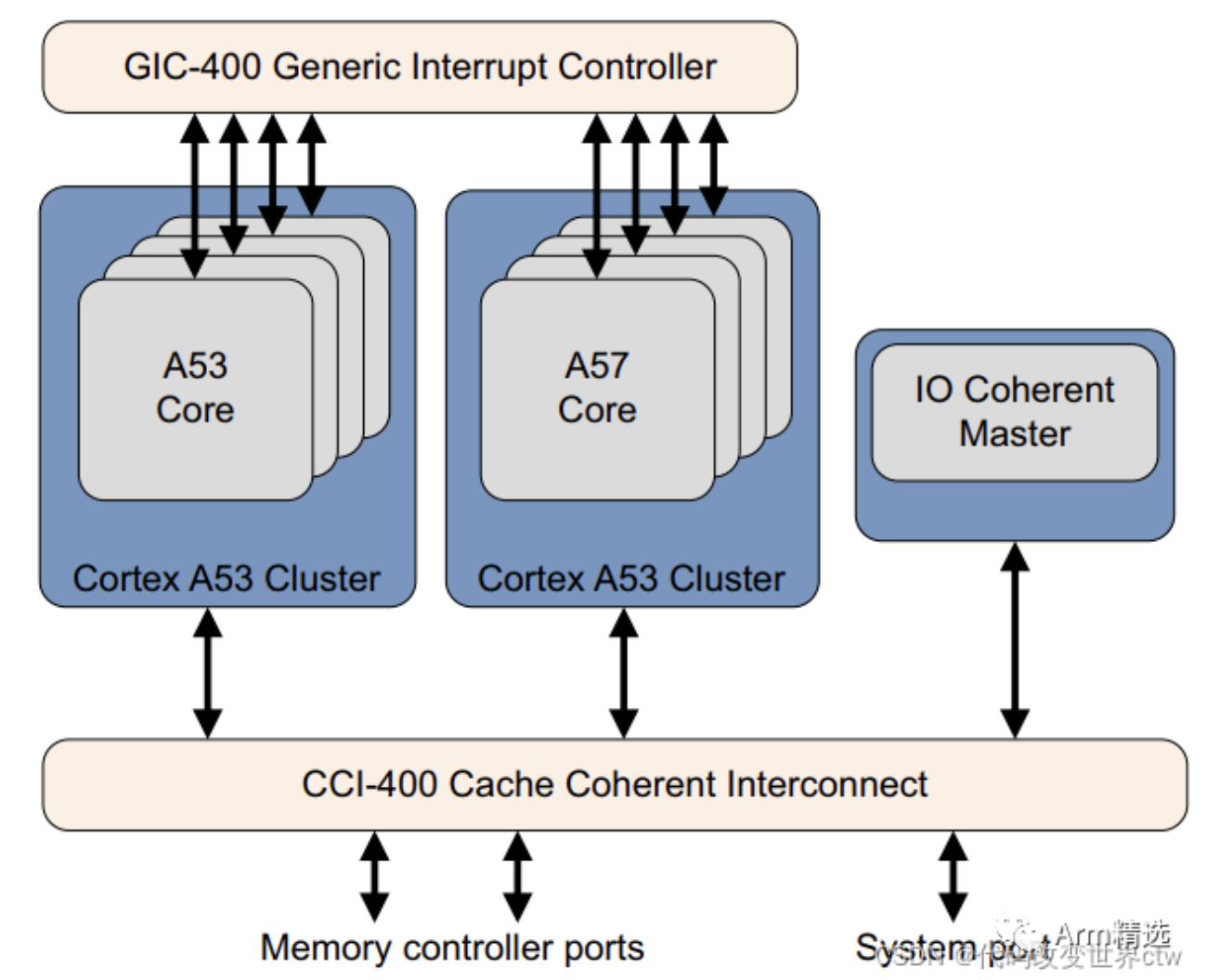

一 A53使用經典的big-LITTLE架構

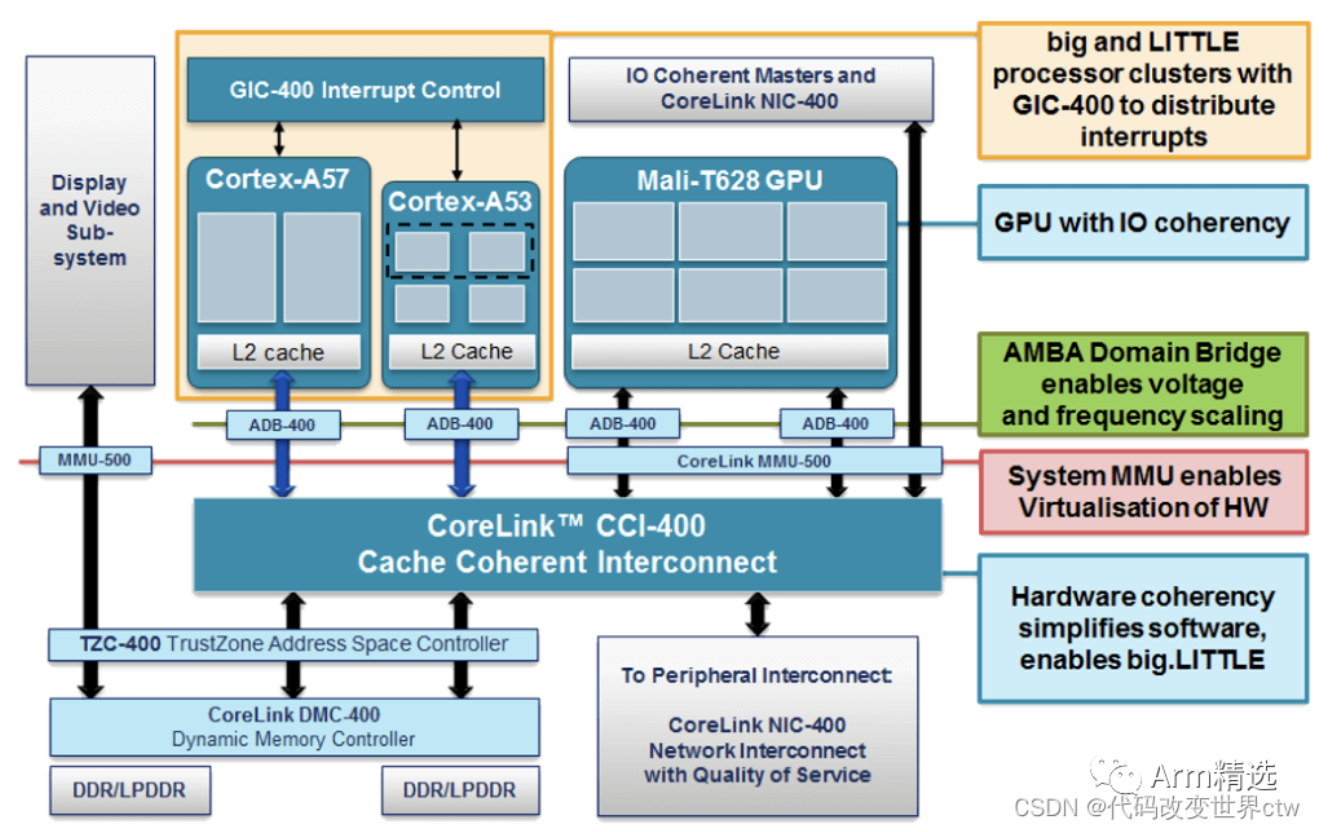

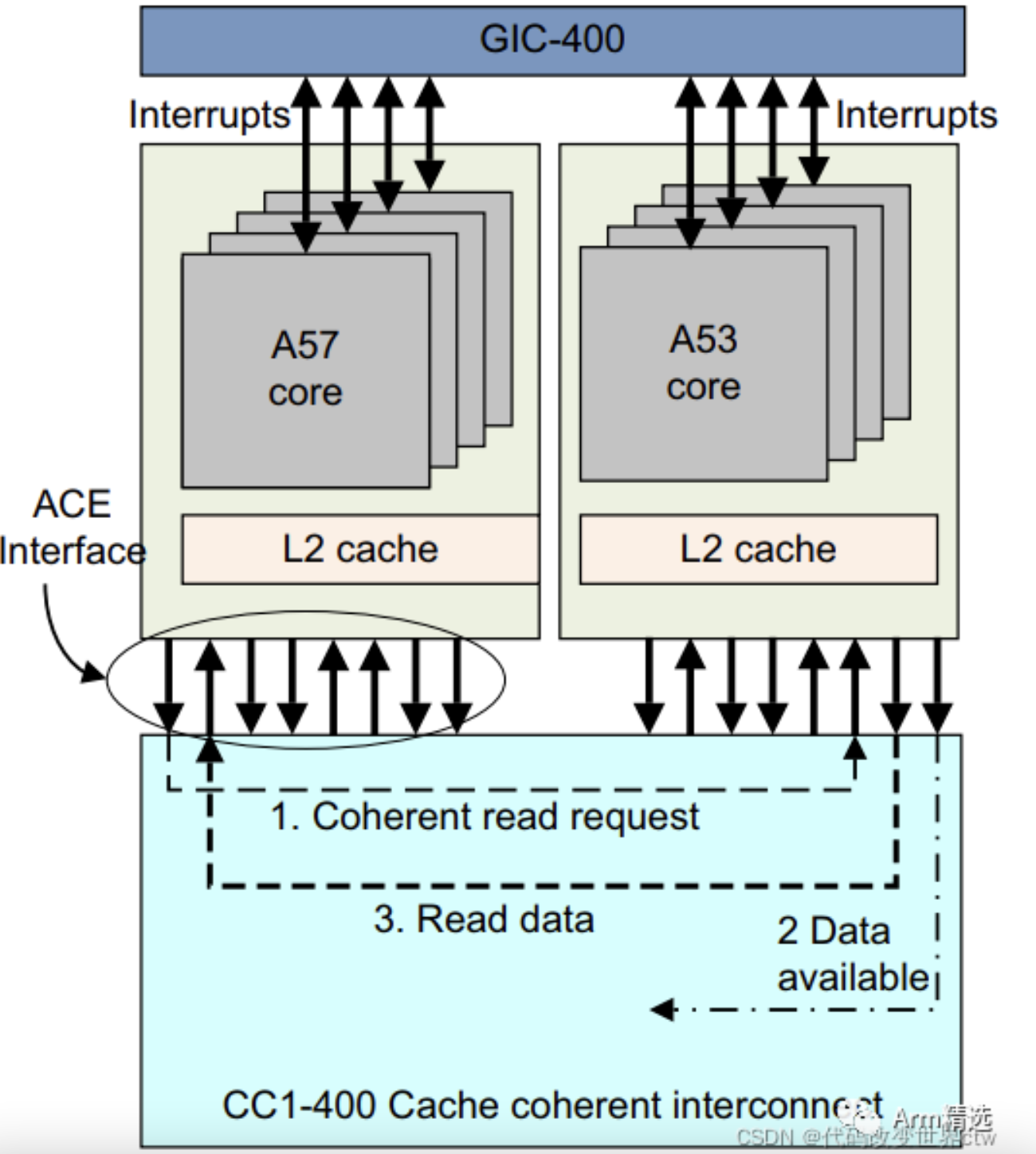

以下是一張比較早期的經典的big-LITTLE的架構圖。

圖1

圖2

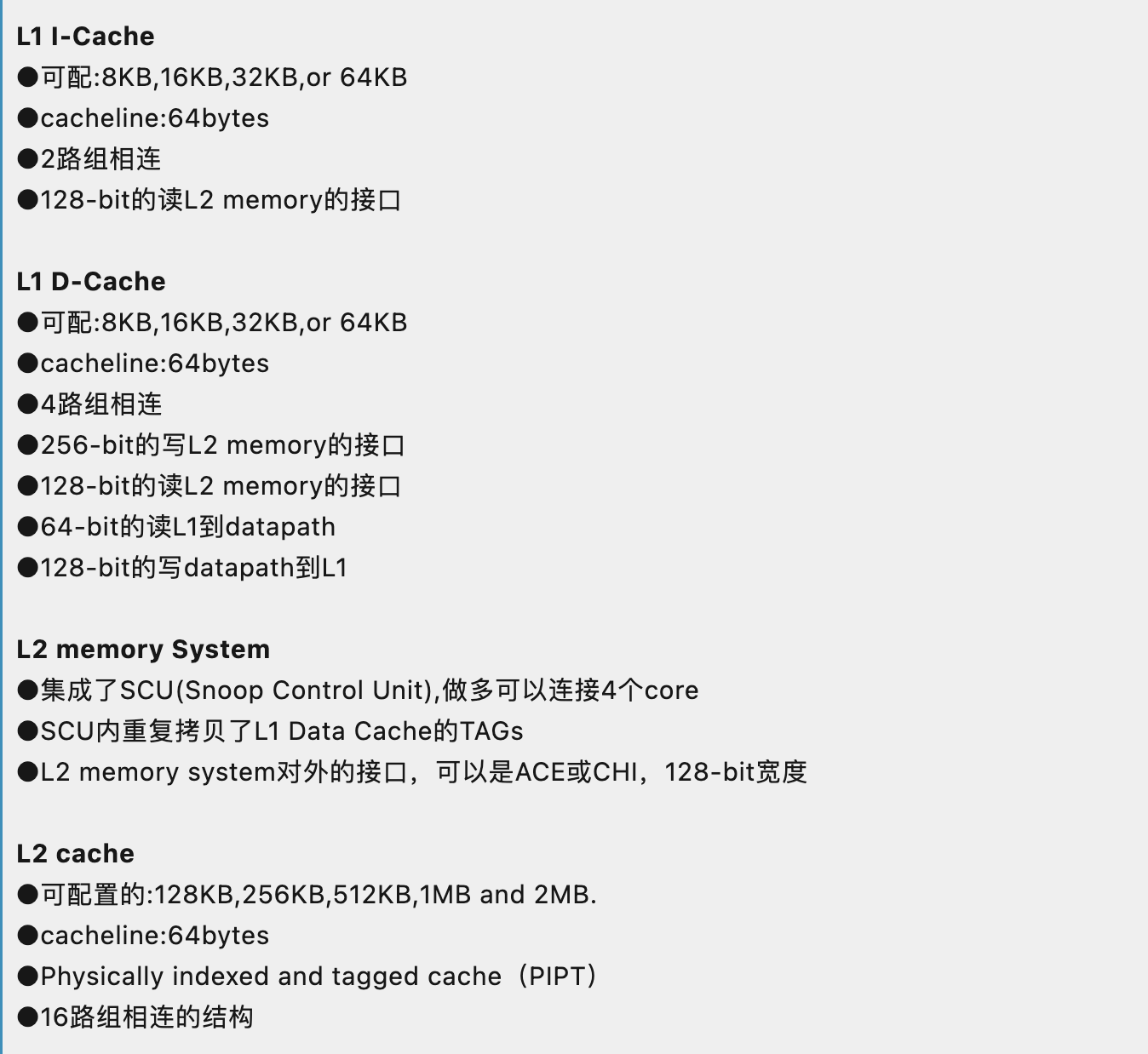

二 A53的cache配置

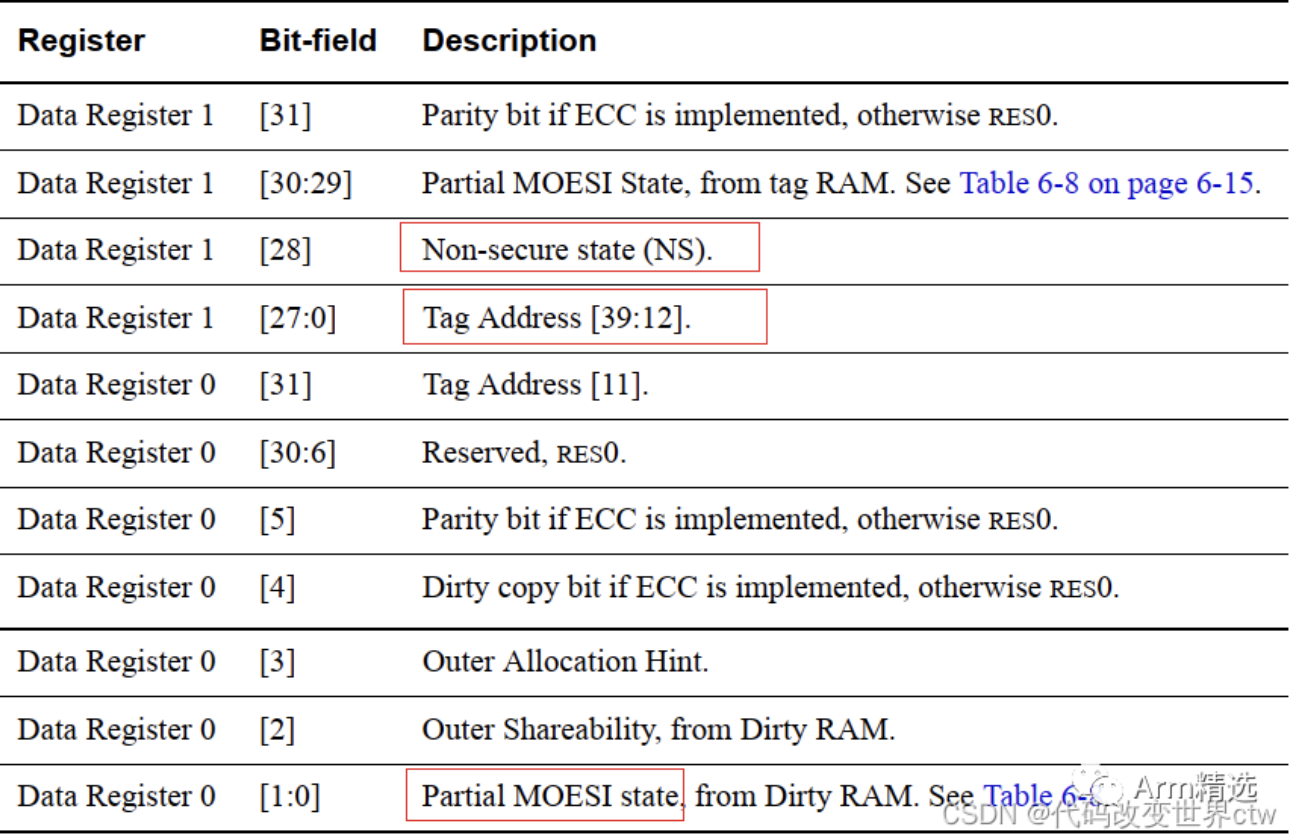

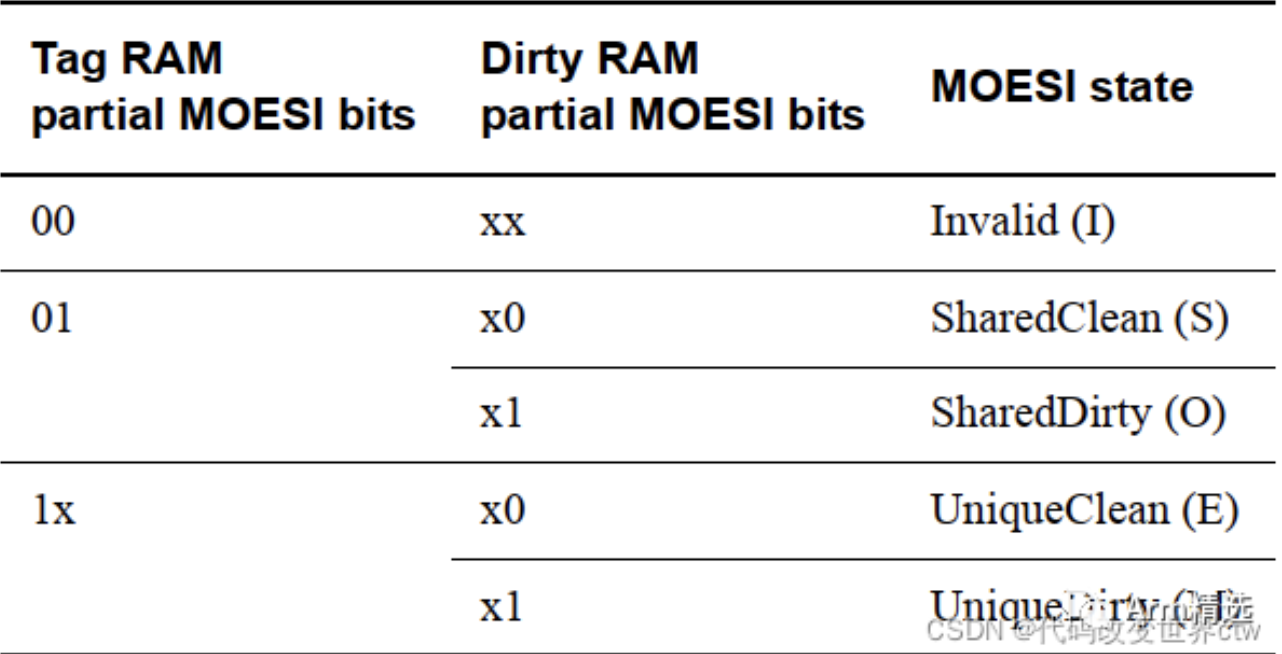

L1 data cache TAG

A53的L1 Data cache遵從的是MOESI協議,如下所示在L1 data cache的tag中存有MOESI的標記位。

圖3

MOESI state

圖4

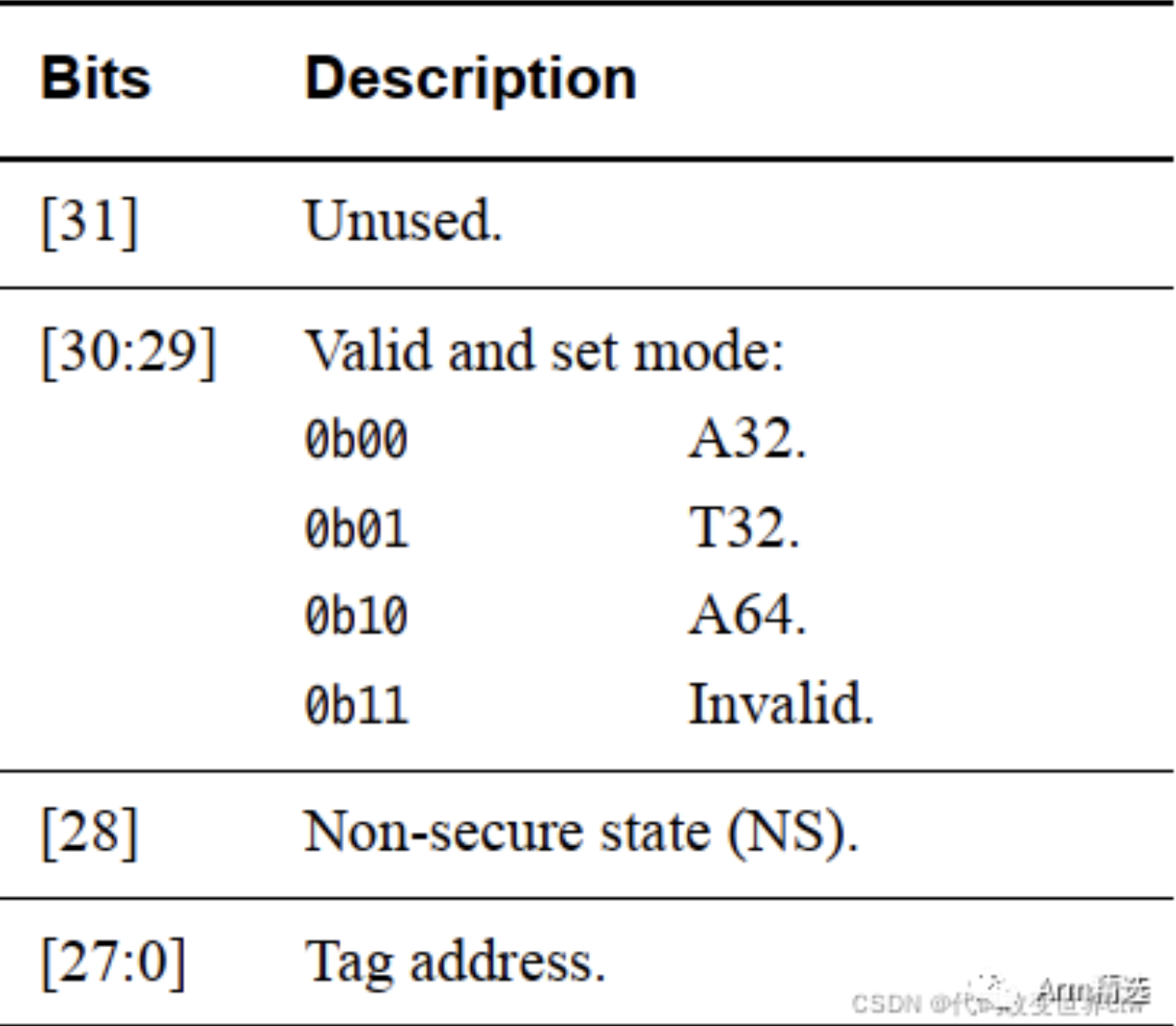

L1 Instruction cache TAG

L1 instruction cache是只讀的,所以也就無需硬件維護的多core之間instruction cache的一致性,所以也就無需組從MOESI協議,以下展示了 * L1 Instruction cache的TAG,其中標記為很少,無MESI標記位。

圖5

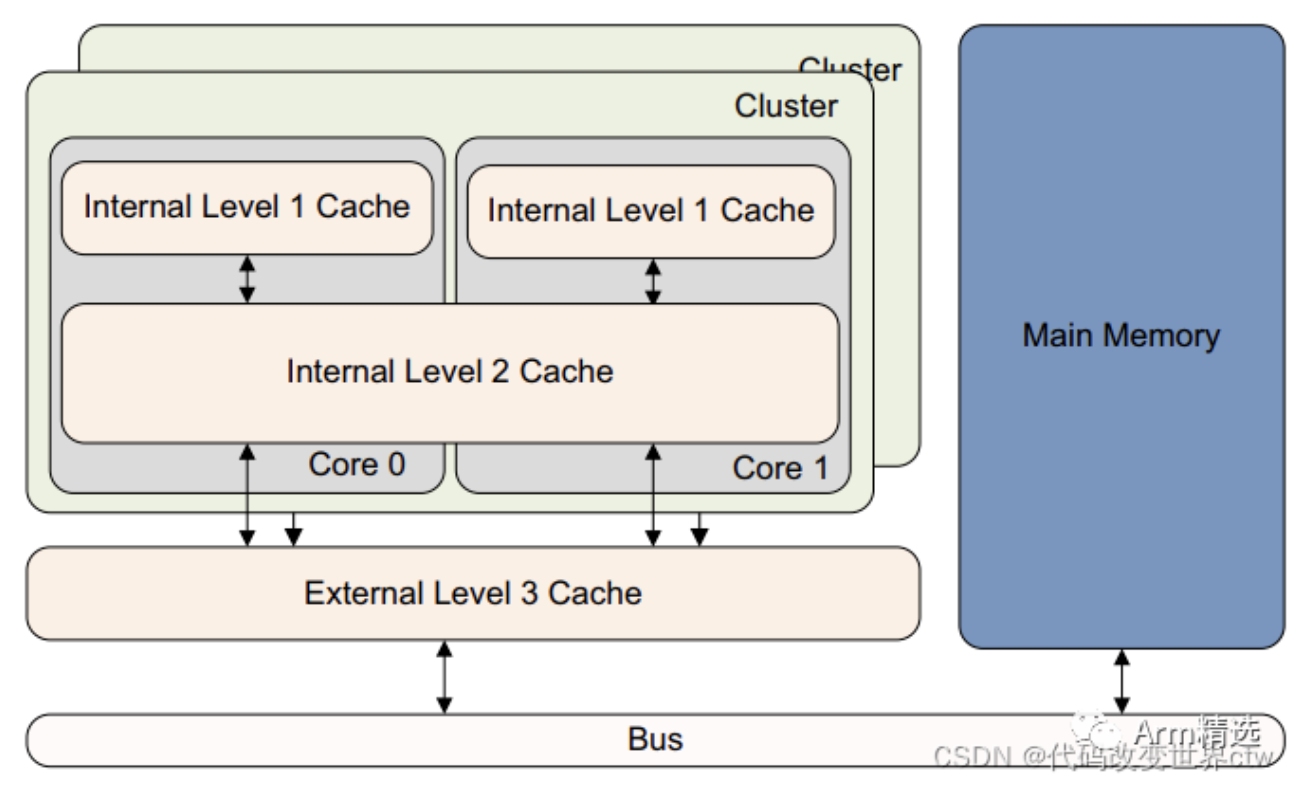

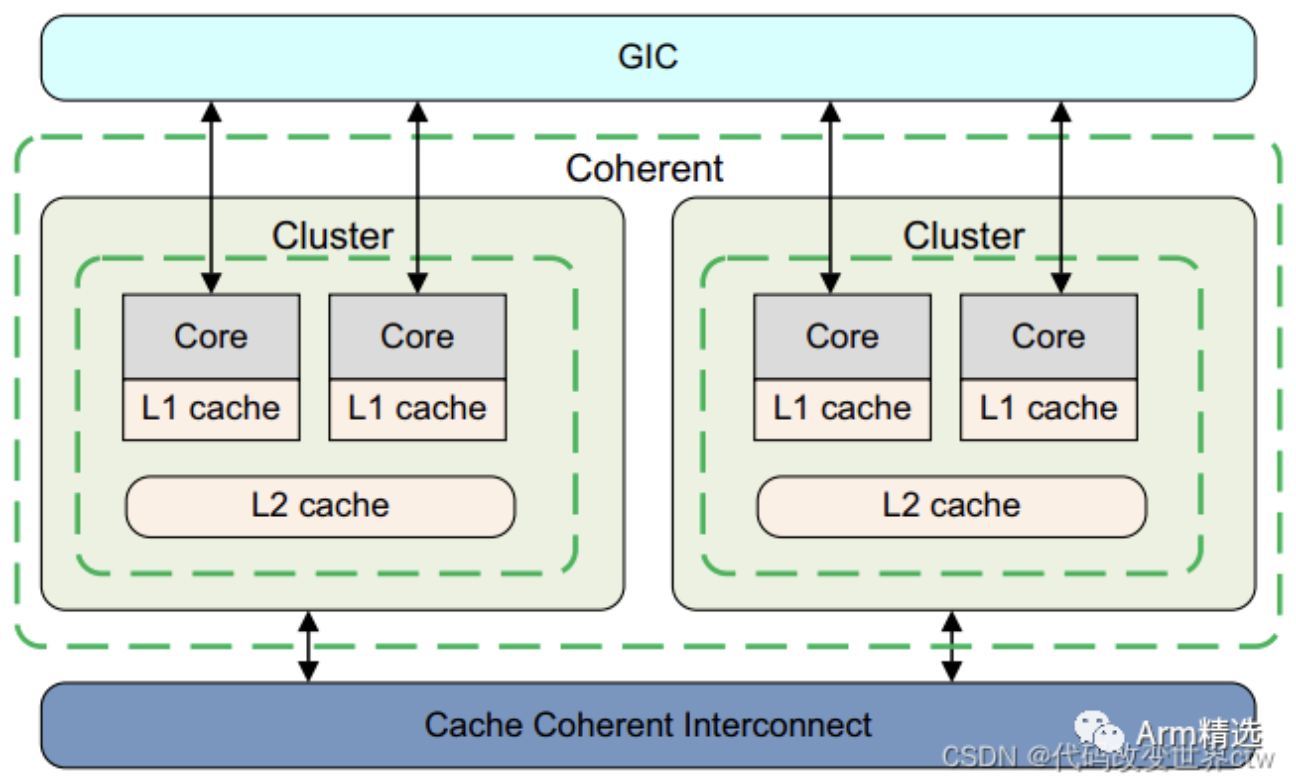

三 cache的層級結構:

- L1 cache是private的在core中。

- L2 cache是share的在cluster中。

圖6

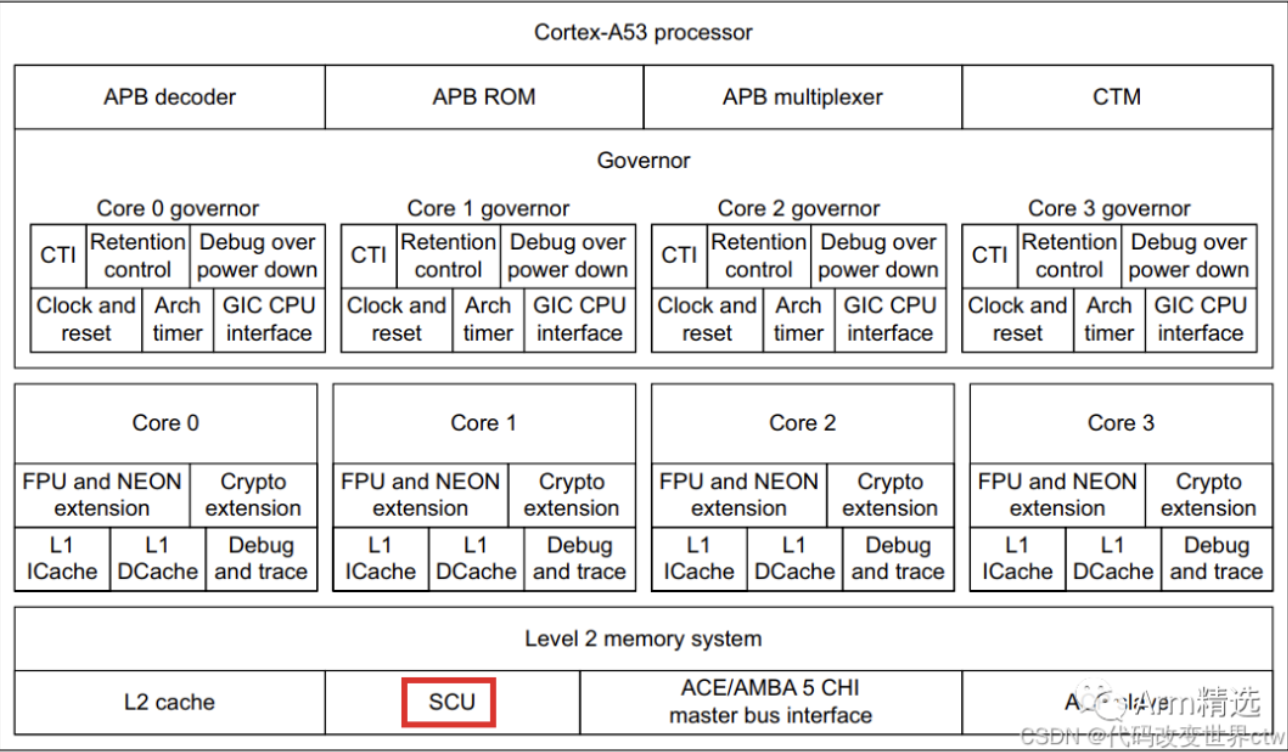

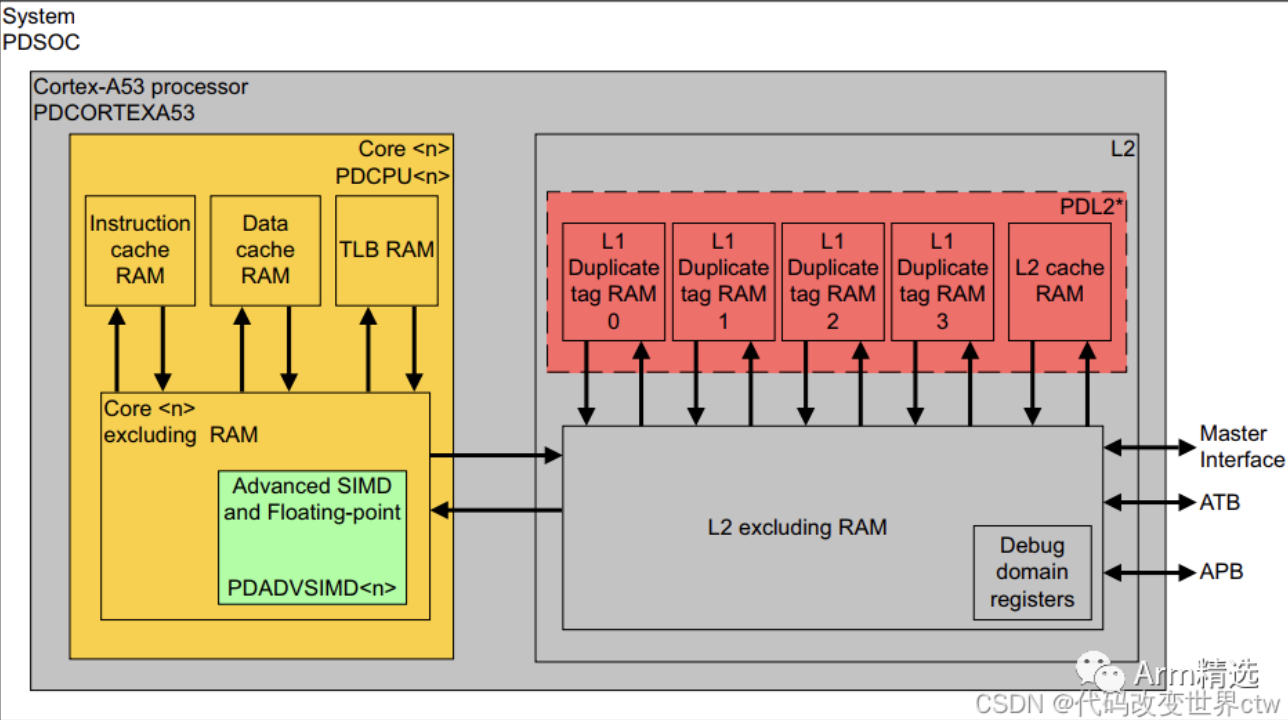

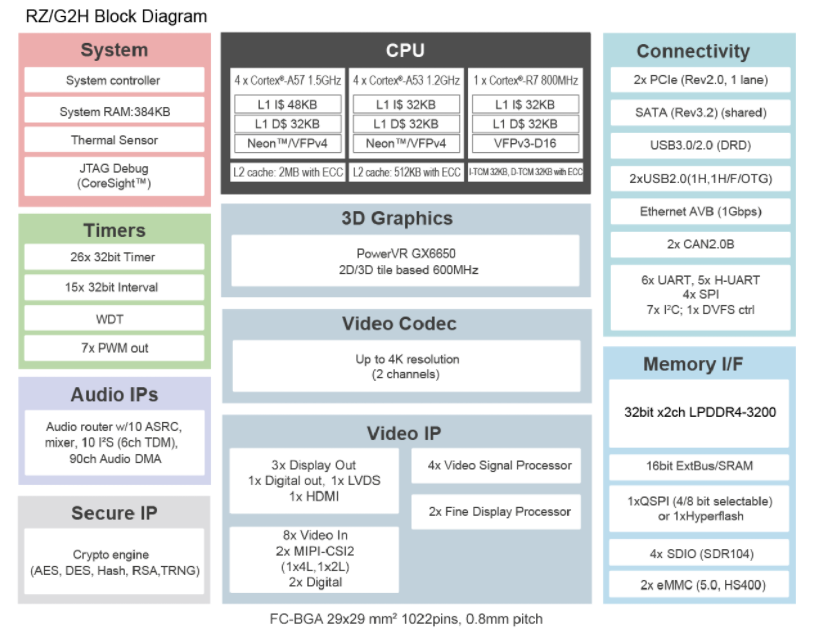

四 L2 memory System系統介紹

在bit.LITTLE架構中,在Cluster中,有一個SCU單元,SCU單元主要是執行和維護L1 cache的一致性(MESI協議或其變體如MOESI協議)。

圖7

在L2 Memory System的中,除了包含L2 cache,也會包含L1 Duplicate tag RAM(這里指的其實是L1 Data Cache Tags)。

圖8

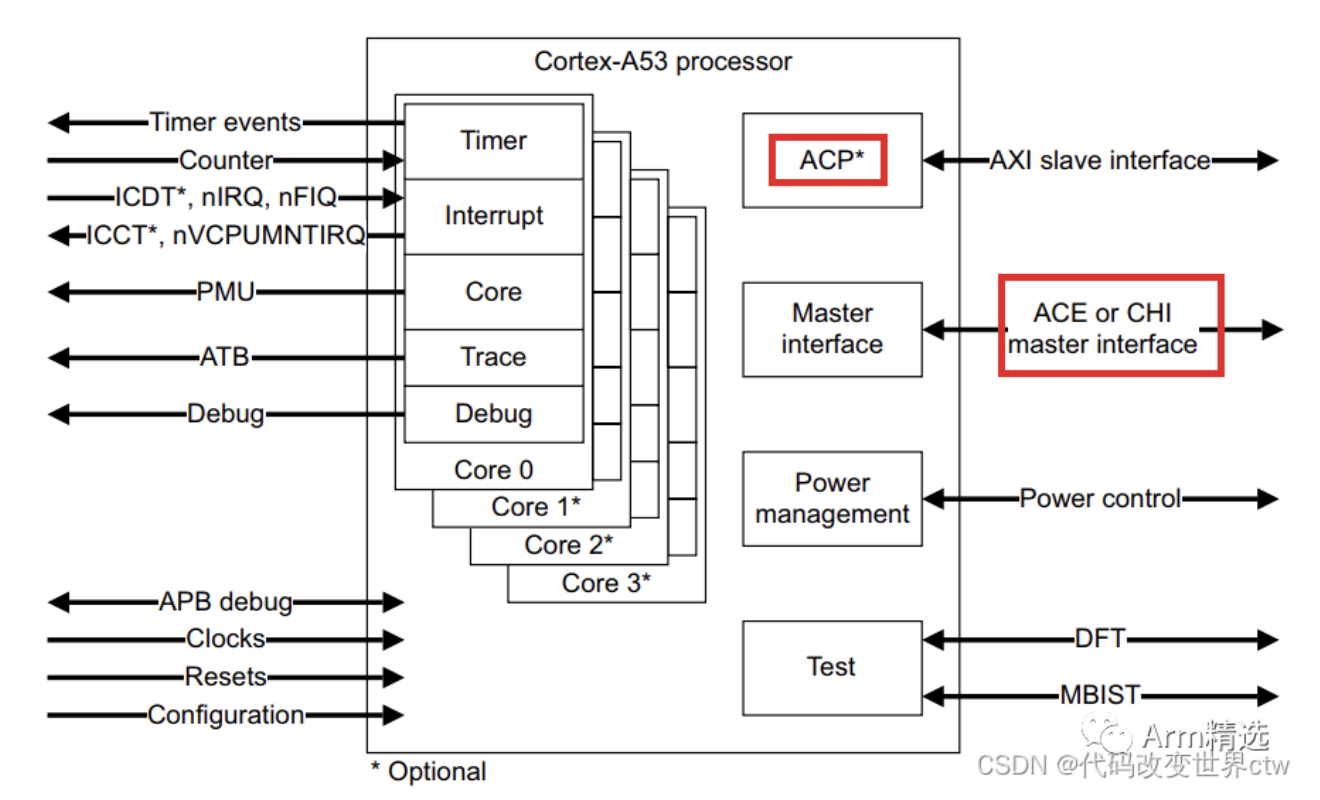

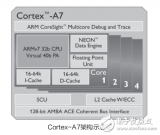

五 多cluster之間的緩存一致性

cluster和外界的接口,可以是ACE或CHI(目前常用的是ACE,后面的趨勢可能是CHI)。

圖9

- 如果使用的是ACE,那么多cluster之間的一致性,依靠CCI+ACE來維護。

- 如果使用的是CHI,那么多cluster之間的一致性,依靠CMN+CHI來維護。

圖10

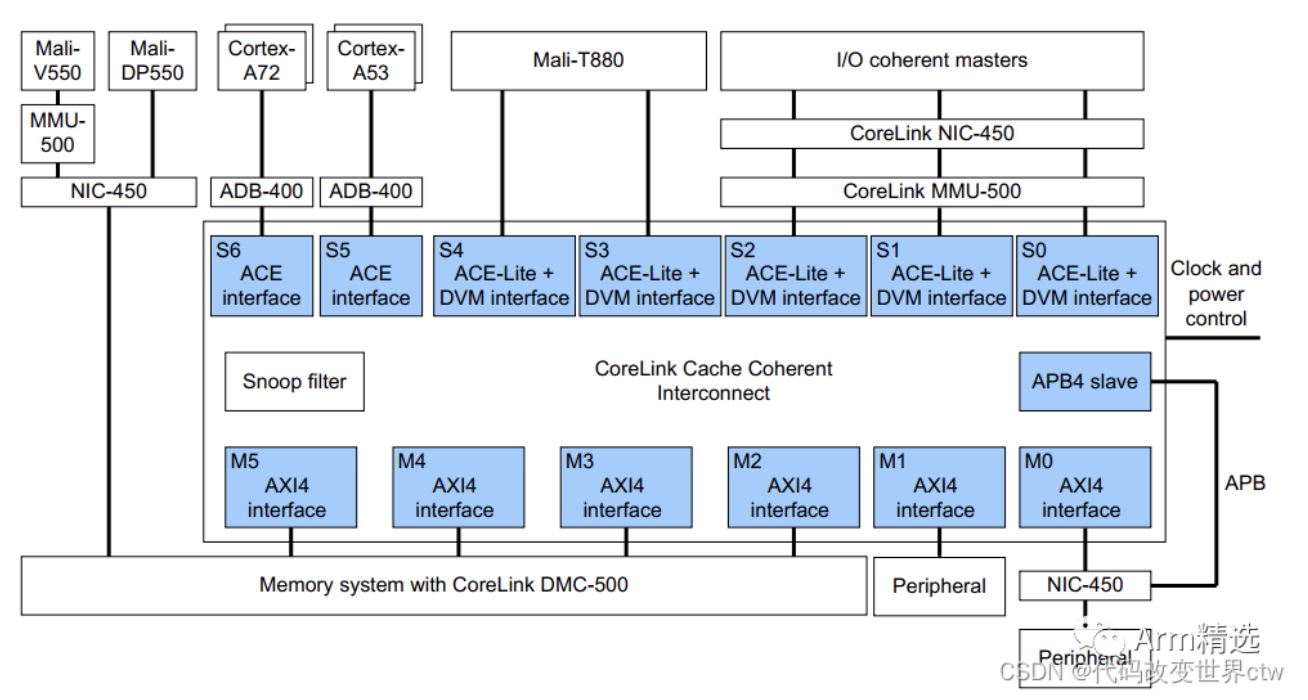

六 CCI的介紹(以CCI-550為例)

CCI-550包含一個包容性監聽過濾器(snoop filter),用于記錄存儲在ACE主緩存。

偵聽過濾器可以在未命中的情況下響應偵聽事務,并偵聽適當的主控只有在命中的情況下。Snoop過濾器條目通過觀察來自ACE主節點的事務來維護以確定何時必須分配和取消分配條目。

偵聽過濾器可以響應多個一致性請求,而無需向所有人廣播ACE接口。例如,如果地址不在任何緩存中,則監聽過濾器會以未命中和將請求定向到內存。如果地址在處理器緩存中,則請求被視為命中,并且指向在其緩存中包含該地址的ACE端口。

圖11

圖12

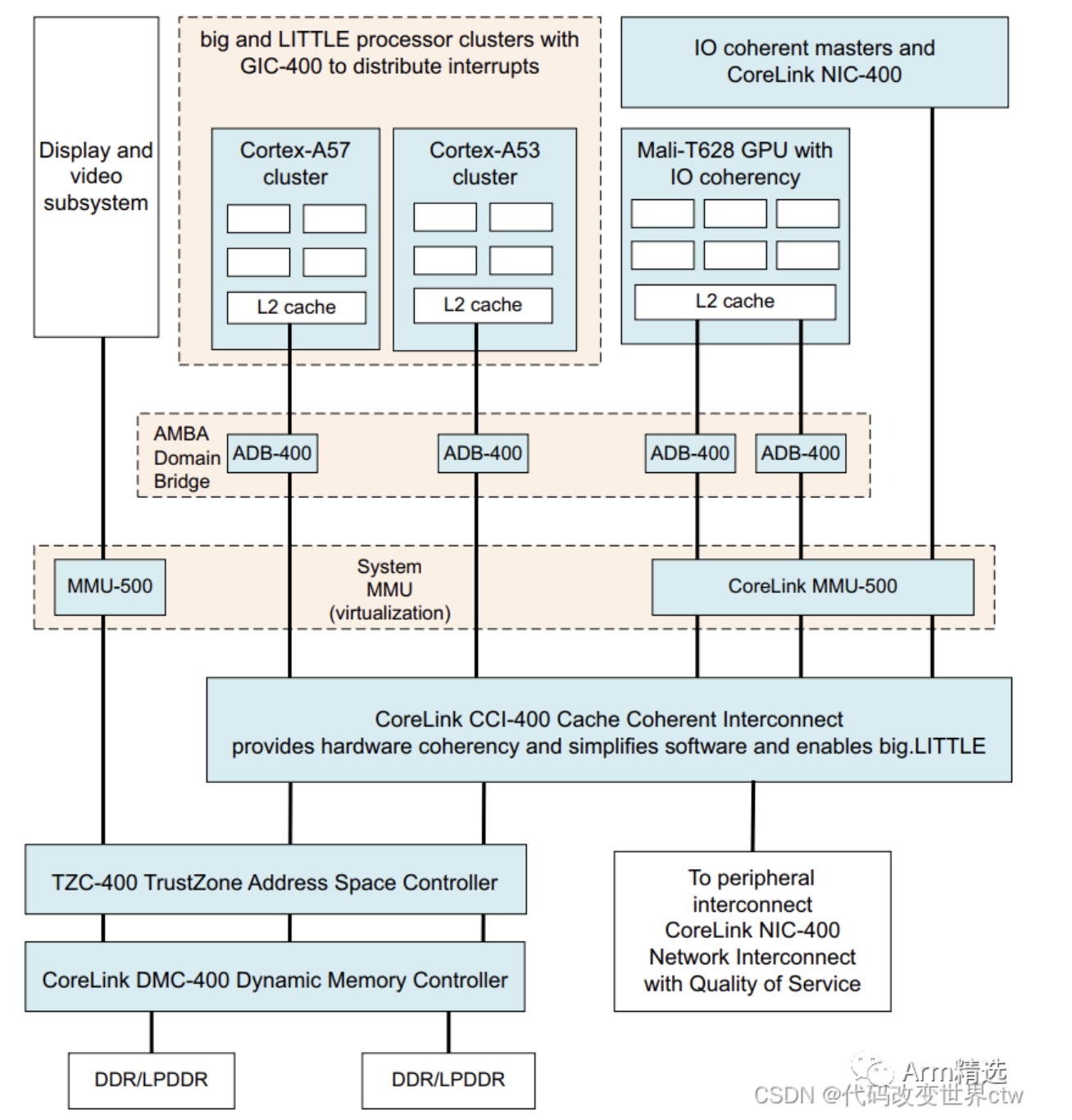

七 經典示例框圖

圖13

-

處理器

+關注

關注

68文章

19804瀏覽量

233529 -

ARM

+關注

關注

134文章

9306瀏覽量

375003 -

RAM

+關注

關注

8文章

1391瀏覽量

116782 -

ARM架構

+關注

關注

15文章

181瀏覽量

36983 -

Cortex-A53

+關注

關注

0文章

33瀏覽量

21540 -

cache技術

+關注

關注

0文章

41瀏覽量

1194

發布評論請先 登錄

ARM cortex-A53是否支持硬件預取、整型流水線的個數等相關參數

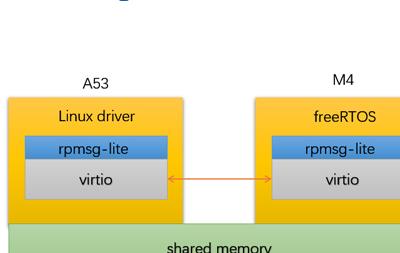

案例分享!IMX8 Cortex-A53與Cortex-M4多核通信開發詳解【含源碼】

請問可不可以在使用qemu模擬出Cortex-A53的架構來運行rt-thread?

請教大神qemu模擬cortex-A53運行rt-thread出錯怎么解決呢?

Cortex-A53循環模型9.6.0版用戶指南

ARM Cortex-A53 MPCore技術參考手冊

Cortex-M4F + Cortex-A53異構多核給工業控制帶來何種意義?

Imagination新推APXM-6200 CPU,性能超越Cortex-A53

ARM Cortex-A53嵌入式開發平臺Android手冊

ARM Cortex-A53嵌入式開發平臺FETT507-C OKT507-C用戶編譯手冊

帶四核Arm Cortex-A57和四核Arm Cortex-A53 CPU的RZ/G2H超高性能微處理器數據手冊

Arm Cortex-A53 cache的架構解析

Arm Cortex-A53 cache的架構解析

評論