當ADC迅猛發(fā)展的時候,我們射頻工程師的份額,又被吃掉了一塊。

大家都慌慌的,心里想,如果ADC一直進步,一直進步,然后直接懟到靠近天線的那邊,那射頻工程師還能干些啥。

確實,如果把ADC放到靠近天線,采樣后就變成數(shù)字信號,而數(shù)字信號的處理,比模擬信號要靈活的多。

在有的接收機設計中,ADC已經(jīng)開始對RF直接采樣了,也就是開始使用直采架構。

不過,要使用直采架構,也需要滿足一定的條件,比如說,ADC在相應的采樣率工作時,功耗是滿足系統(tǒng)指標的。

采樣定理

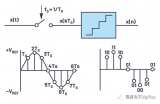

在使用ADC進行采樣時,有兩種采樣方法,一種稱為低通采樣,也叫過采樣(oversampling);另一種稱為帶通采樣,也叫欠采樣(undersampling)。

低通采樣

低通采樣的時候,要求采樣率fs>=2*fH,信號才不會發(fā)生混疊,在這種情況下,是假定信號的有用信息,頻率是DC~fH。但是,在大多數(shù)通信系統(tǒng)中,信號通常是窄帶信號。在這種情況下,就可以使用帶通采樣。

帶通采樣

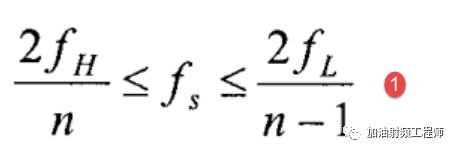

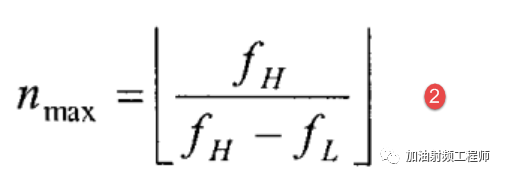

帶通采樣的時候,避免混疊的最小采樣率,取決于信號帶寬,而不是有用信號的最高頻率fH,即fs>=2*BW,其中BW是信道帶寬。不過,需要注意的是,這只是最低要求,除此之外,帶通采樣時的采樣率還需要滿足下面的等式,才能實現(xiàn)無混疊采樣,即:

其中,fL和fH分別是指帶通信號的最低和最高頻率。允許的最大的n值為:

如何理解上面的采樣速率的要求?

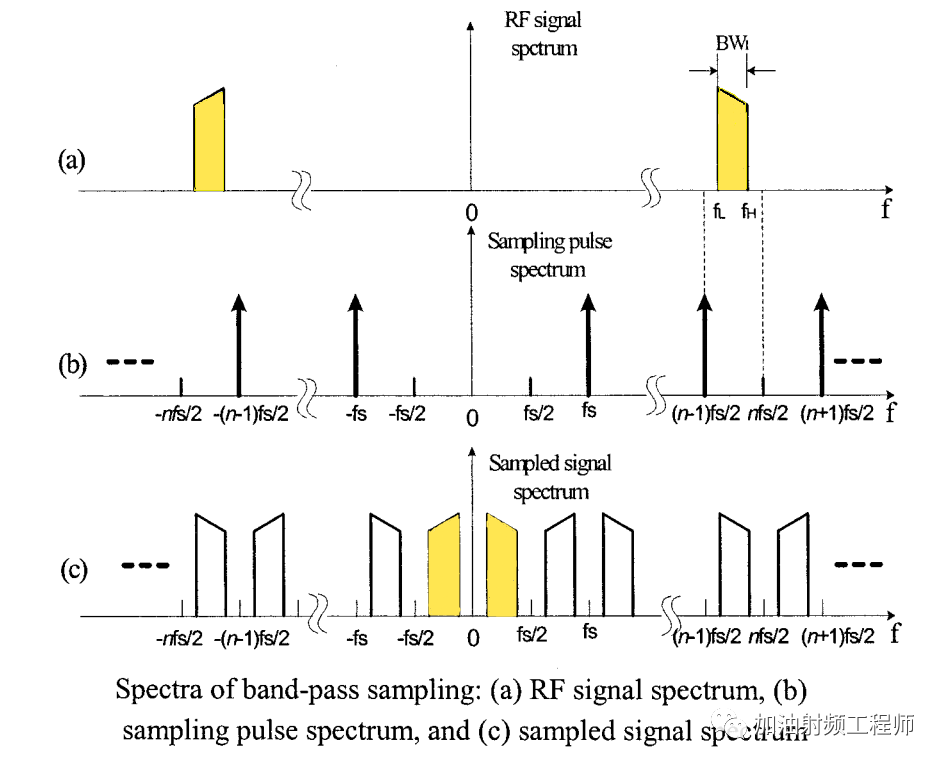

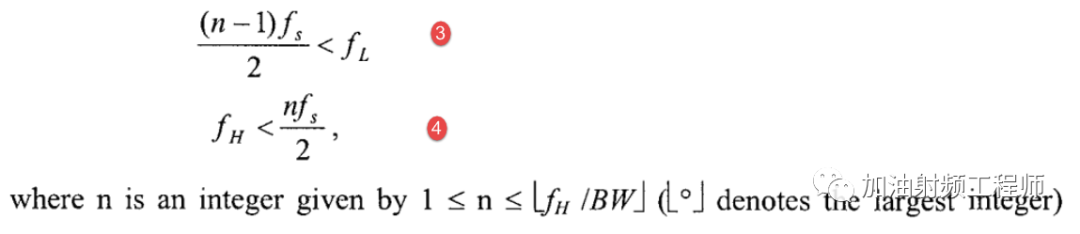

需要采樣不混疊,則要求有用信號位于一個奈奎斯特域以內(nèi),即(n-1)fs/2~nfs/2以內(nèi),如下圖所示。

這樣的話,很容易就列出下面的兩個不等式,如下圖所示。

對式子3和4稍微做一下整合,就可以得到式1。

也許會說,低通采樣要記一個公式,帶通采樣又要記一個公式,好麻煩啊!

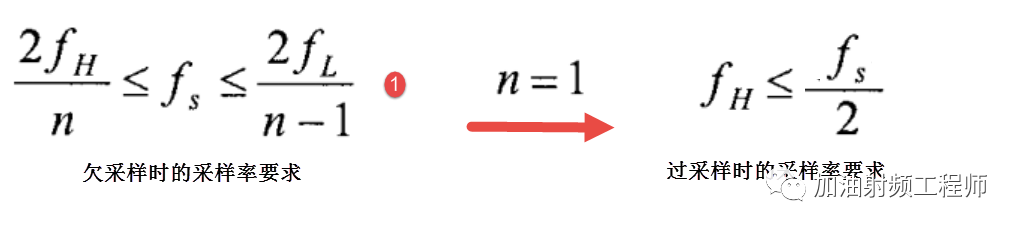

其實,仔細看看,這兩個公式是統(tǒng)一的,當n=1的時候,欠采樣時的采樣率要求,即等于過采樣時的采樣率的要求。

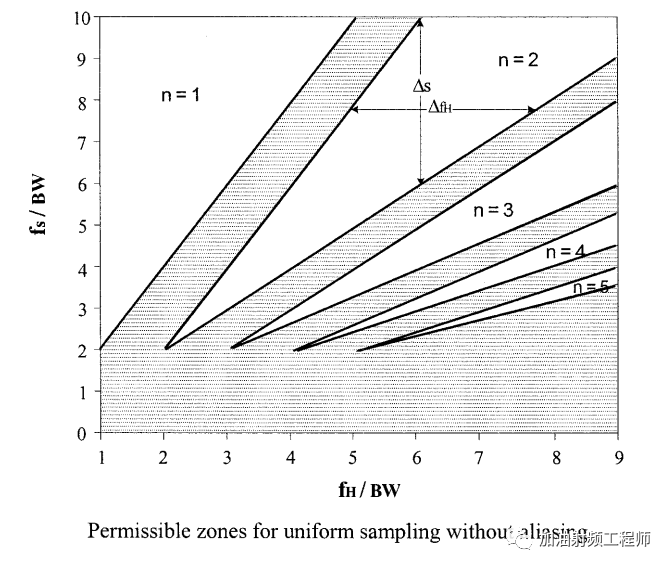

欠采樣時的采樣率的要求,可以用下圖進行圖形化表示,橫坐標是fH/BW,縱坐標是fs/BW。白色部分,為能夠?qū)崿F(xiàn)無混疊采樣的區(qū)域,陰影部分,則代表會產(chǎn)生混疊。從圖中可以看出,無混疊的區(qū)域,隨著fs/BW和fH/BW的增加而增加。

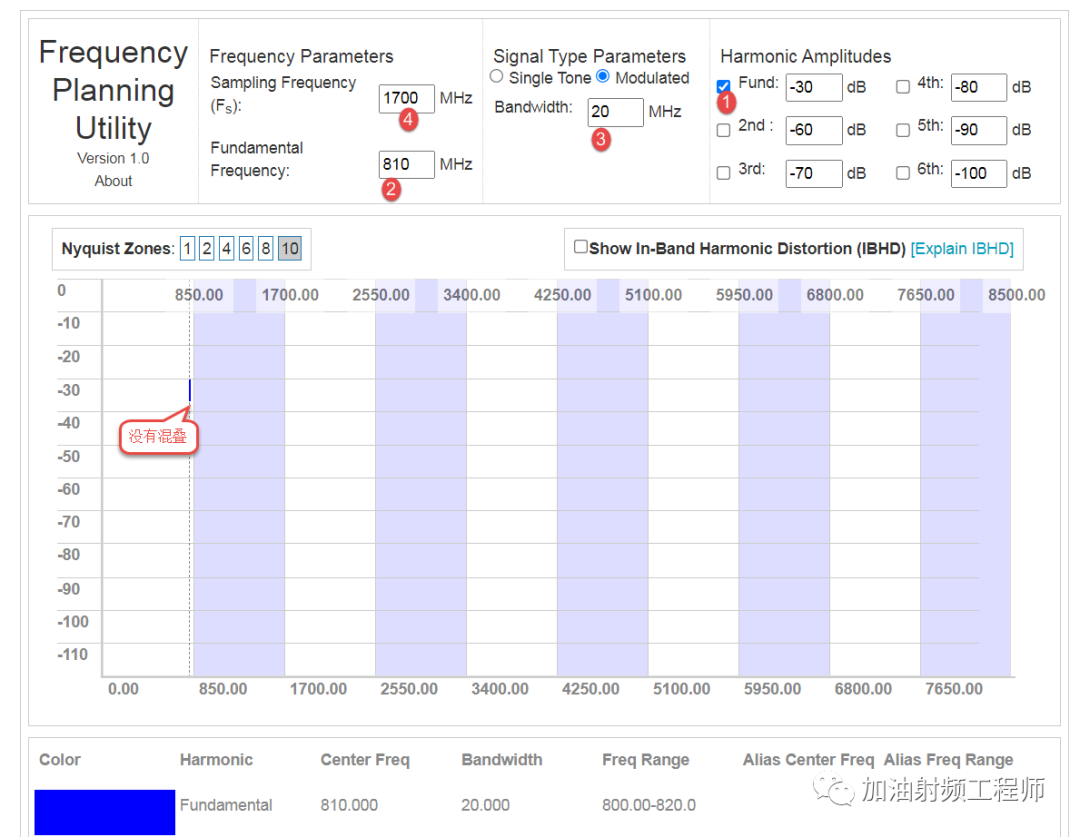

把Harmonic Amplitudes的選項中,只保留Fund選項,然后Nyquist Zones選擇10。假設信號的最低頻率fL=800MHz,fH=820MHz,那么BW=fH-fL=20MHz。

對于上式1,取n=1,即過采樣時,使得fs>2*fH=1640MHz,則顯示結(jié)果如下圖所示。

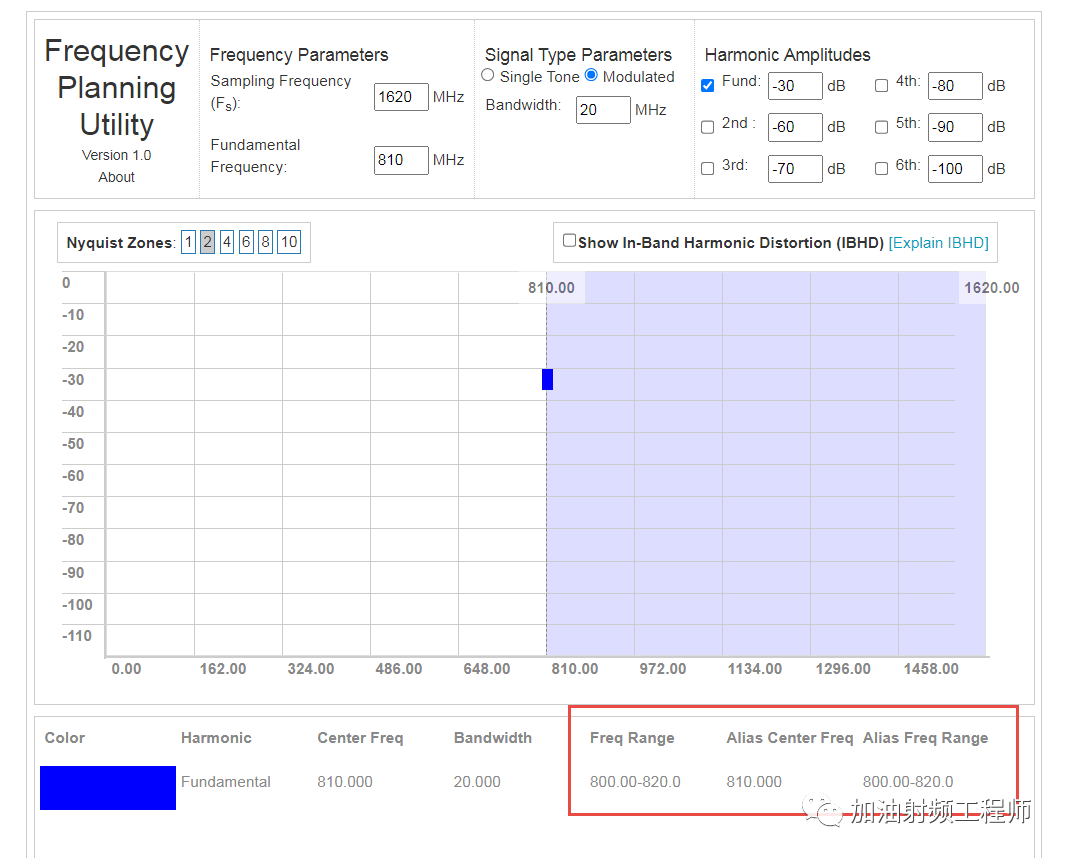

如果把采樣率選成1620MHz,則結(jié)果如下圖所示,

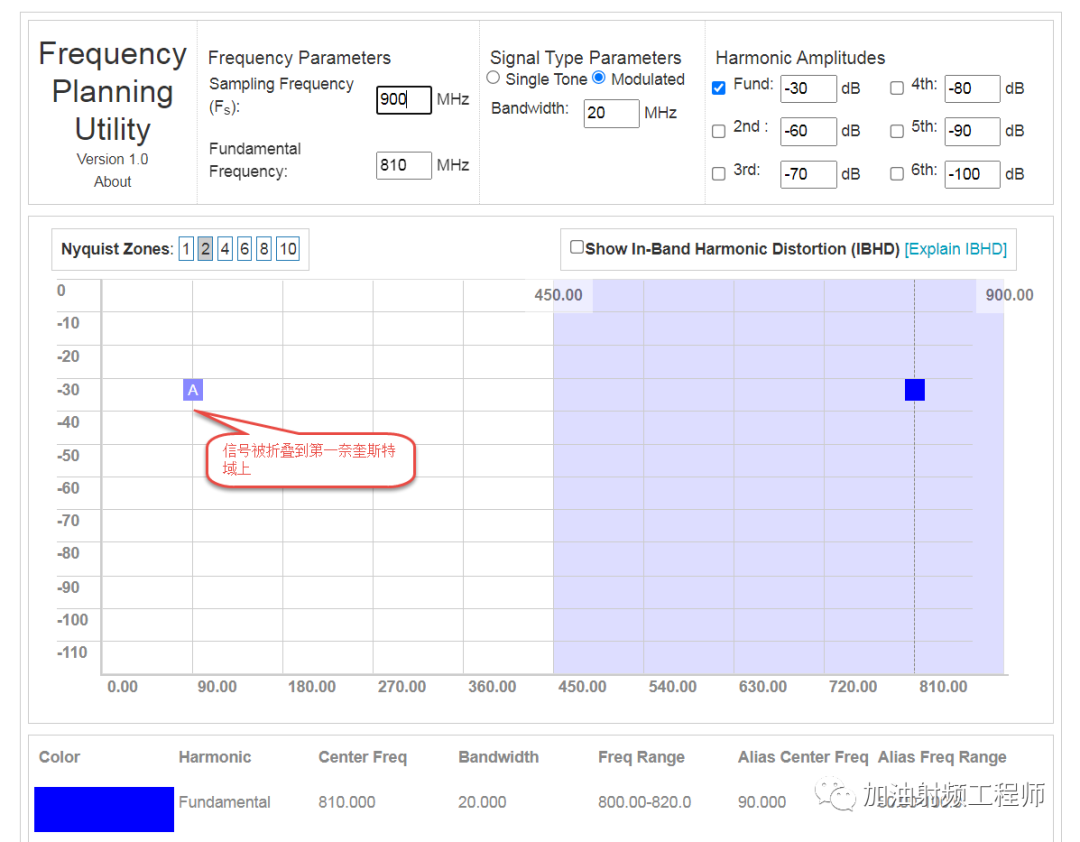

選擇n=2,則式1變?yōu)閒H<=fs<=2*fL,那么假設選擇fs=900MHz,滿足式1.

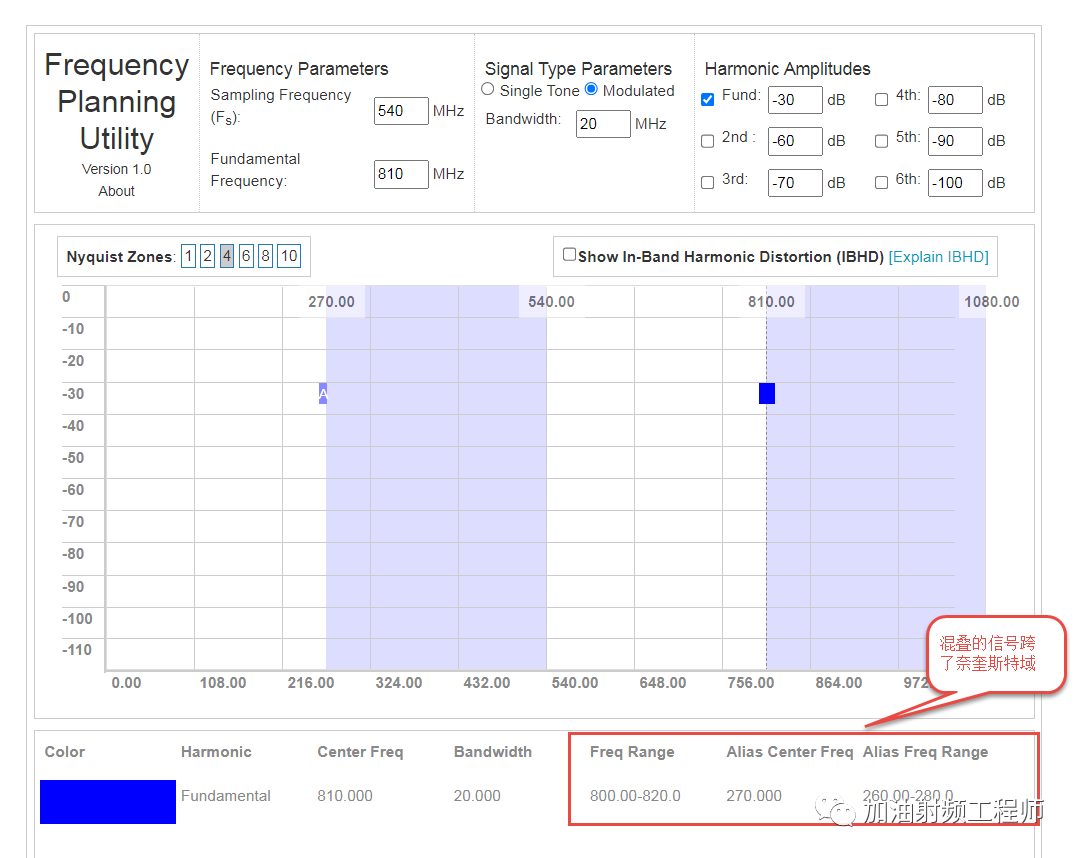

那如果選擇一個不符合式1的采樣率呢,發(fā)現(xiàn)采樣出來的信號,處于第一奈奎斯特域和第二奈奎斯特域中間,不滿足要求。

審核編輯:劉清

-

接收機

+關注

關注

8文章

1218瀏覽量

54214 -

通信系統(tǒng)

+關注

關注

6文章

1223瀏覽量

53943 -

數(shù)字信號處理器

+關注

關注

5文章

478瀏覽量

27731 -

混疊濾波

+關注

關注

0文章

2瀏覽量

5471 -

ADC采樣

+關注

關注

0文章

134瀏覽量

13122

原文標題:直采架構中的帶通采樣

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

TC334 ADC采樣25us采不到的問題怎么解決?

如何理解ADS5263的fin和采樣率呢?

TIVA在ADC數(shù)字比較器中斷中能否直接讀取采樣值?

常見ADC架構設計要求與應用

低速帶通采樣定理與高速AD/DA之間的矛盾分析

關于單片機ADC的詳細參數(shù)描述,助你更深層次的理解ADC采樣

求助,關于ADC采樣的相關參數(shù)問題

ADC中的吞吐速率如何理解,它與采樣速率是否等同呢?

LTC1402:串行12位2.2Msps采樣ADC,帶關閉數(shù)據(jù)表

ADC中采樣技術的信號鏈設計挑戰(zhàn)

如何理解ADC直采架構中的帶通采樣要求呢?

如何理解ADC直采架構中的帶通采樣要求呢?

評論