本節介紹后端處理的剩余部分,上節我們講到floorplan和placement。后面就到了CTS階段。

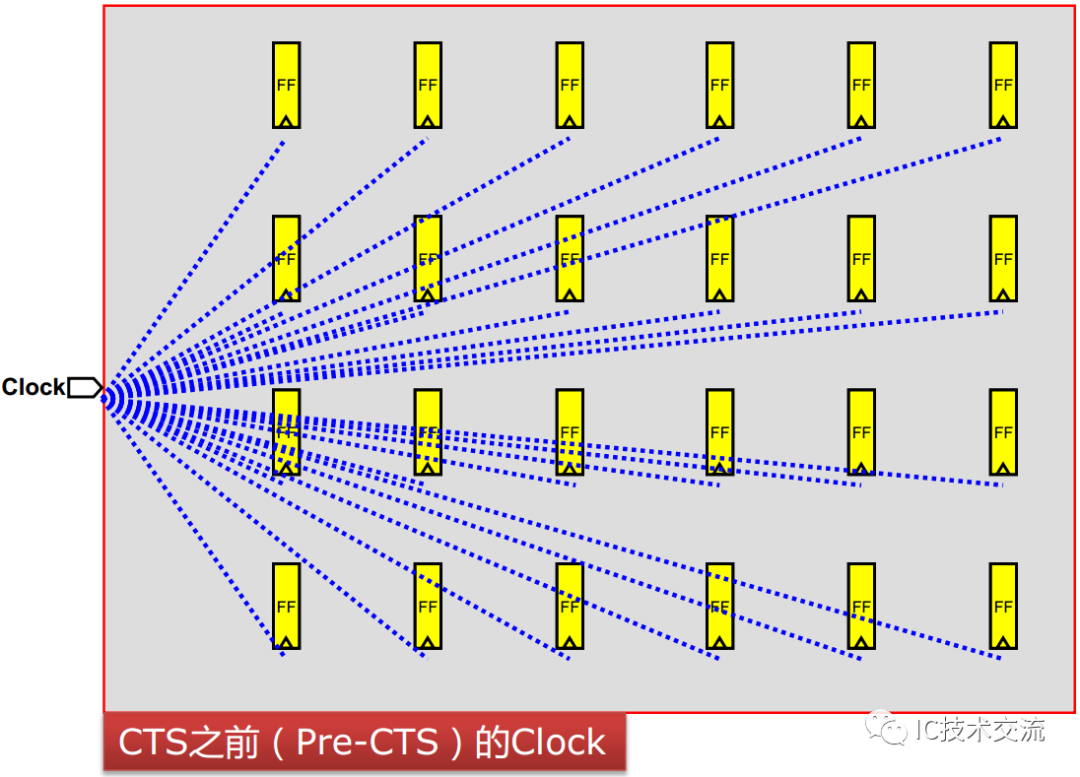

1、在此之前,從synthesis開始到placement,Clock都被假設為理想的,從clock port到reg/CK的延時都為0;需要構建一棵Clock Tree,把Clock信號從port送到reg/CK;

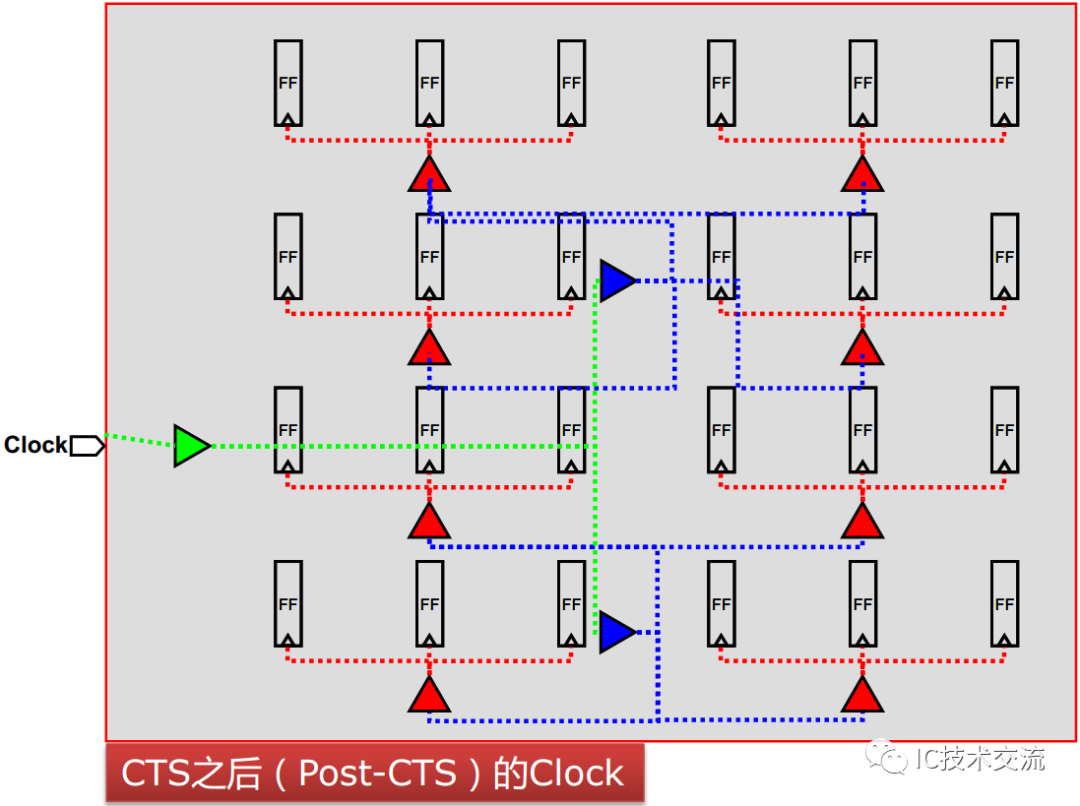

2、Clock Tree長好之后還需要對timing進行優化(這個階段的優化叫做PostCTS Opt),包括setup和hold;

第一:place_opt是基于理想時鐘而對設計進行,長完Clock Tree之后的時刻和理想時鐘存在區別;

第二:CTS的過程中工具會挪動原來的單元,導致delay有變化;

第三:需要修Hold timing,因為在這之前一直沒理會Hold;

3、要完成對Clock Net的繞線(route),這是因為Clock Net比普通的信號Net更重要,所以要先route;

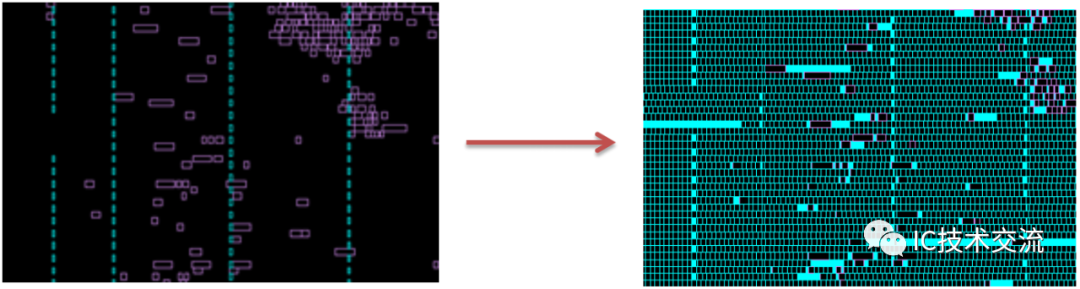

Pre-CTS之前的Clock如上圖所示,Post-CTS之后的Clock如下圖所示:

Post-CTS Opt之后需要進行timing分析。此步驟通過后進行Initial Route:對所有未繞線的net進行繞線。

繞線之后(PostRoute)進行Timing優化:包括setup和hold,及power和Area優化:

1、此時所有net都已經完成route,這時叫detailed route(之前的階段是Virtual Route),所以此時的RC信息和之前估算的會有些區別,delay會有變化;

2、PostRoute優化之后也需要分析是否滿足。

在以上步驟滿足時序要求之后,就要為提高良率(yield)和解決物理規則違規做的工作:

WireSpreading

Redundant ViaInsertion

FillerCellInsertion

Metal Fill Insertion

Metal Slotting

1、這一步也通常被稱為DFM(Design For Manufacturing);

2、良率(Yield):因為有些芯片在wafer上制造出來有缺陷,有的芯片能正常工作,有些芯片工作不正常,那么正常的芯片占總芯片的比例就是良率;

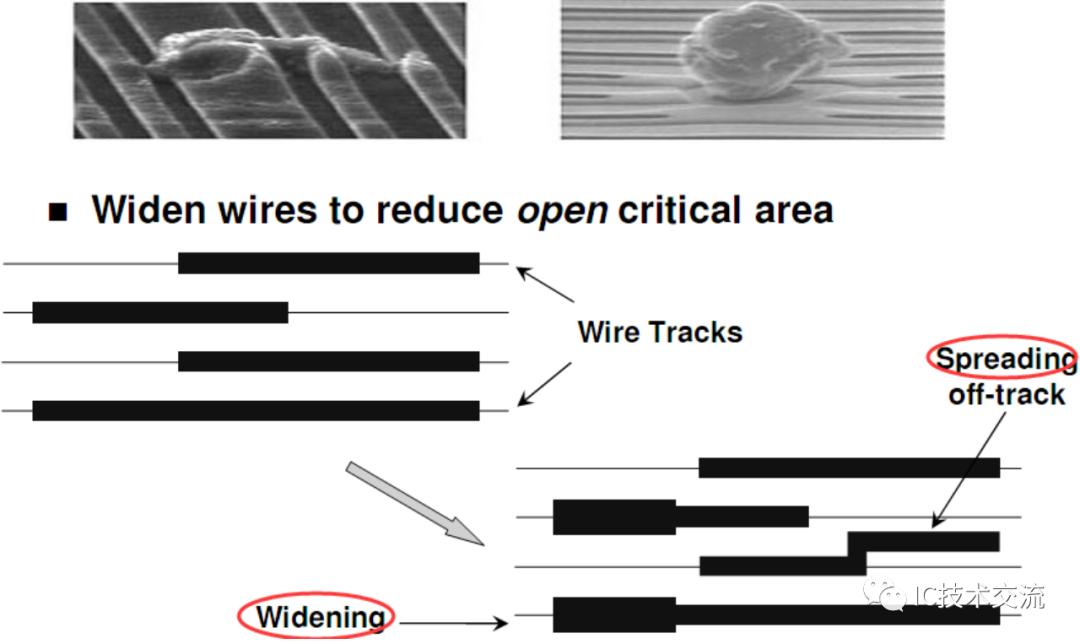

Wire Spreading

顧名思義,就是把線拓寬。如果一粒灰塵落在線上面會影響導通性能甚至短路,在沒有很多線時可把線拓寬,線間距拉大。

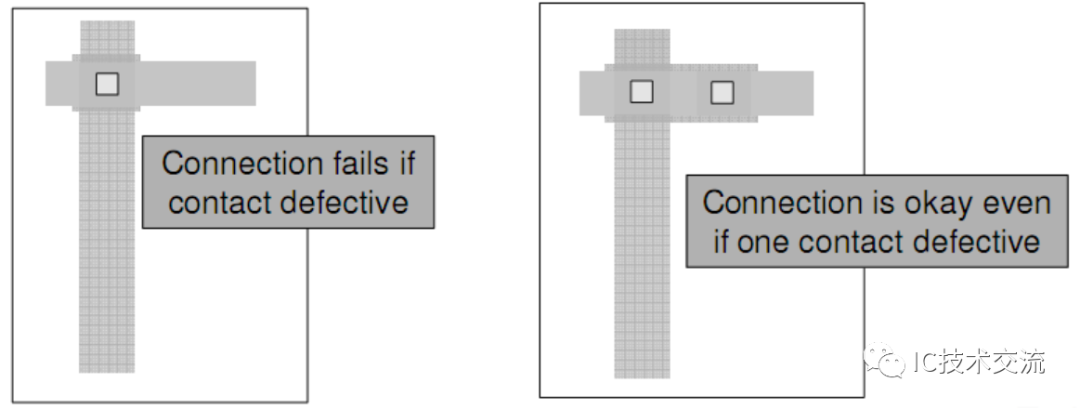

Redundant ViaInsertion

在不同層的連接點Via處,添加冗余Via,這樣即使一個連接點壞掉了,還有其它連接點。

Filler Cell

填充沒有實際功能的cell。在未擺放cell的row/site中填充標準單元,構建連續完整的NWell/PWell。

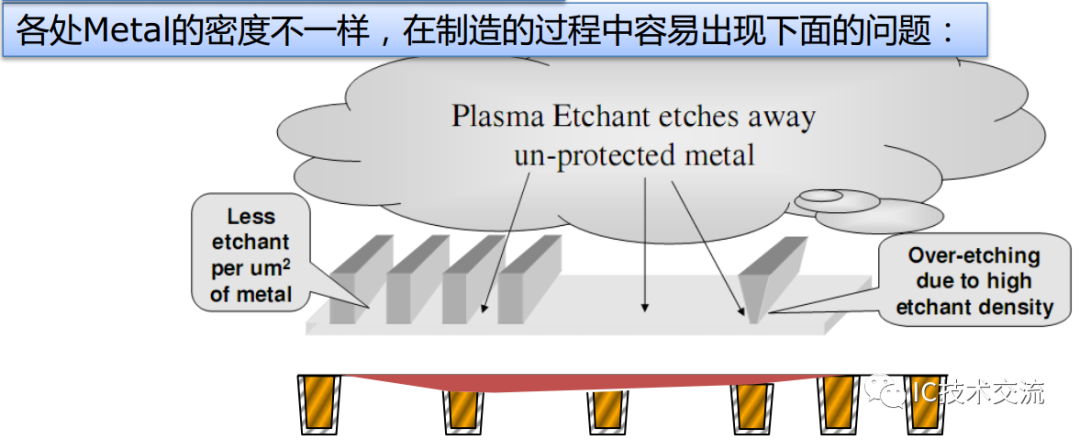

Metal Fil

一般Fab會給出每平方um中最低/最高metal密度,對于metal密度太低的地方,電路蝕刻時會更嚴重,導致metal變形,導通性下降。一般解決辦法是填充Metal,雖然這些metal沒有實際用途。

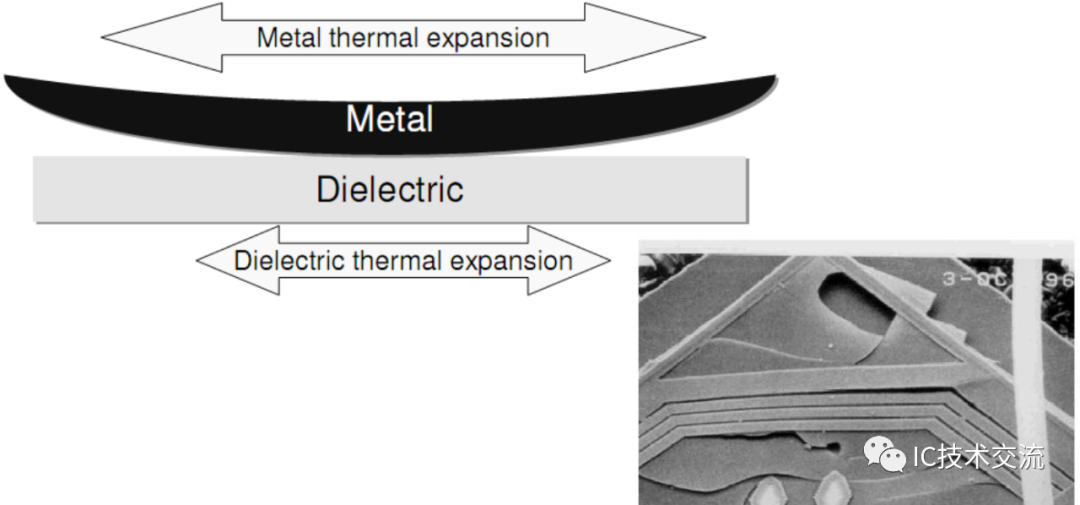

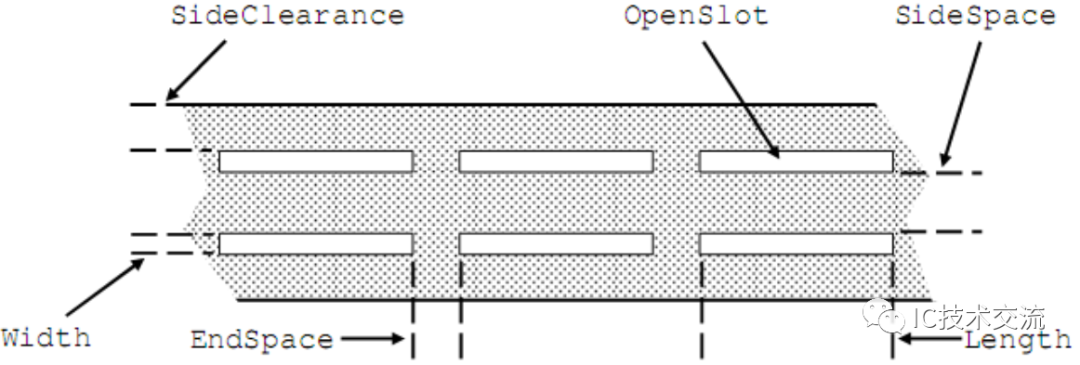

MetalSlot

對于二氧化硅上面覆蓋的Metal,時間長了熱脹冷縮可能兩端會翹起來,對于這種情況可在metal上挖洞。

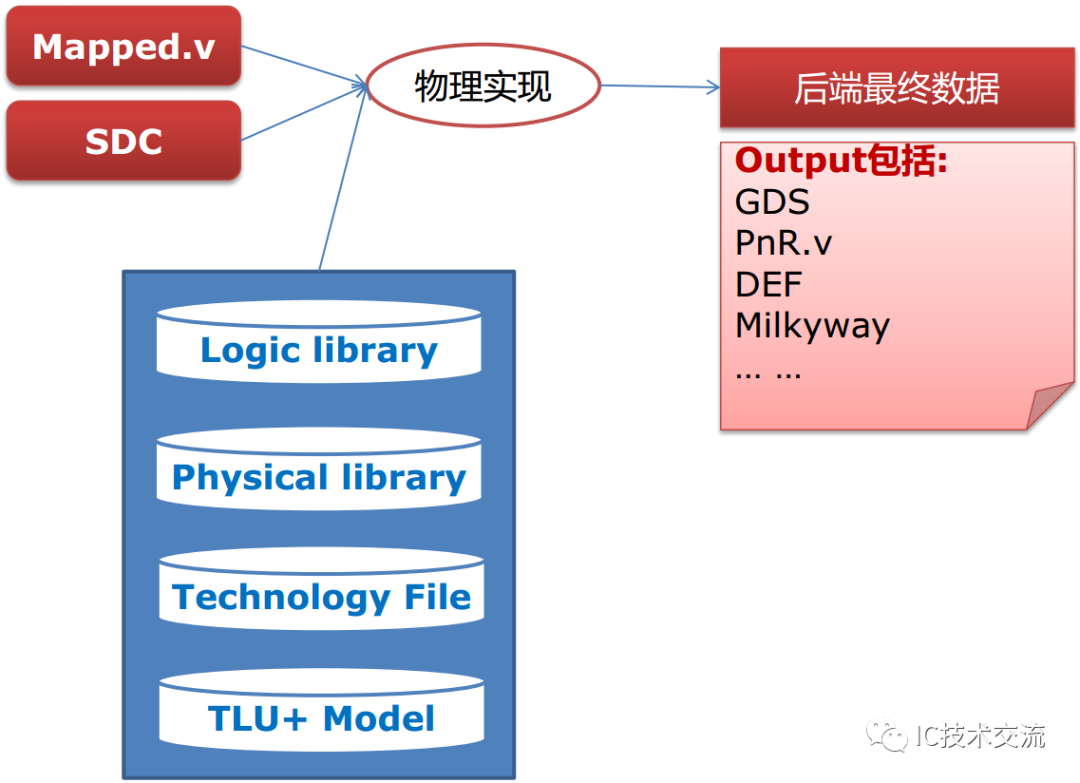

DFM做完后,下面是寫出數據,包括top.gds,top.sdc和top.dc.v,top.pg.lvs.filler.v等,用于形式驗證和sign off等。

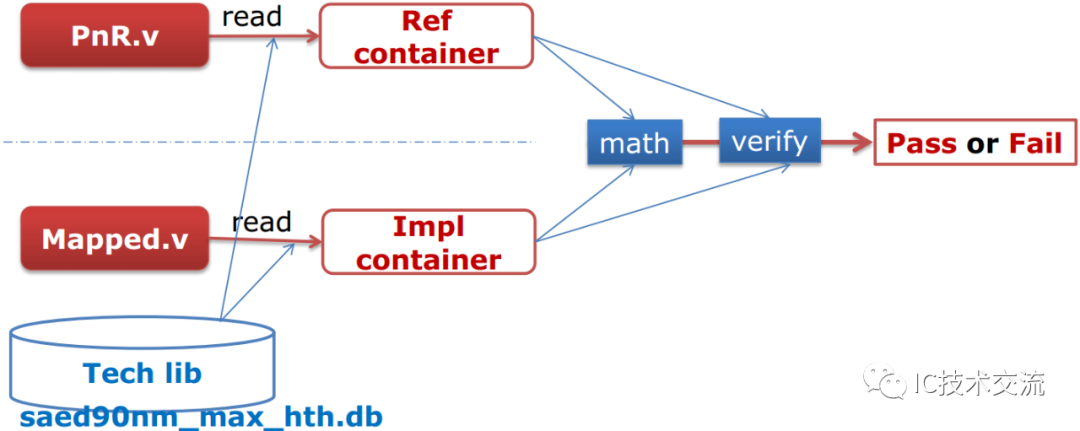

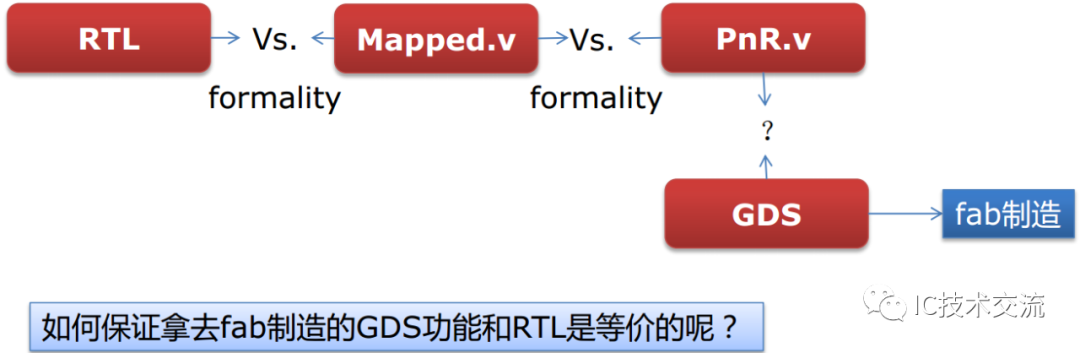

之前的形式驗證是比較rtl和DC綜合后的網表,這次的形式驗證是比對DC綜合后的網表和布局布線之后的網表,兩者不同。

時序最終步驟:Signoff STA:StartRC+PT

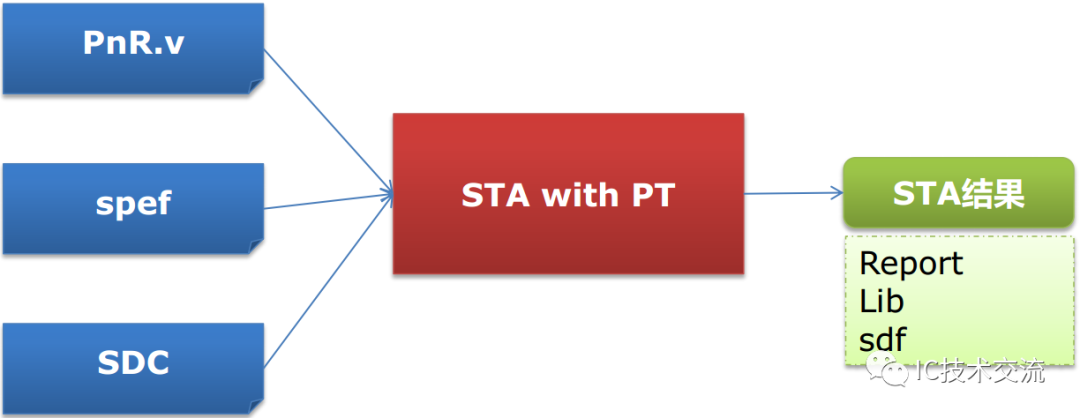

1、STA:Static Timing Analysis,是相對于使用激勵動態仿真而言的,STA通過靜態分析delay并檢查時序是否滿足;

2、Sigoff STA:可以理解為最終的、權威的STA,此處timing要是過了就人為性能滿足要求了;

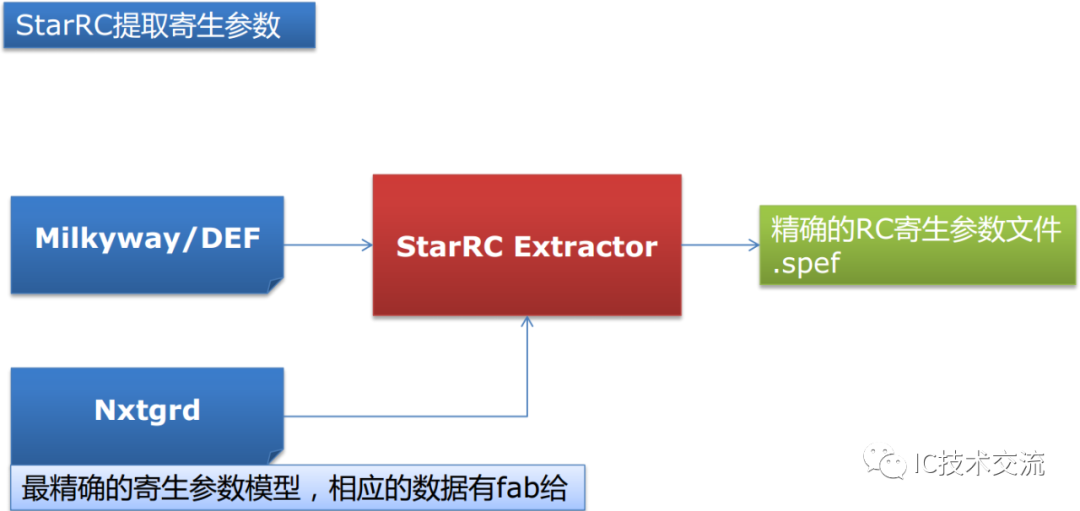

3、Signoff STA要求使用最精確的RC寄生參數和STA算法;

4、高精度的RC參數要synpsys的StarRC工具提取,Cadence相應的工具叫QRC;

5、STA工具用synopsys的PrimeTime(PT),Cadence相應的工具叫ETS;

首先用StarRC提取寄生參數,輸出精確延時的.spef文件

然后使用PT工具做signoff,signoff通過時序分析就完全結束了。

物理驗證是必不可少的,Physical Verfication:DRC,LVS和Antenna

DRC:物理規則檢查(Design Rule Check)

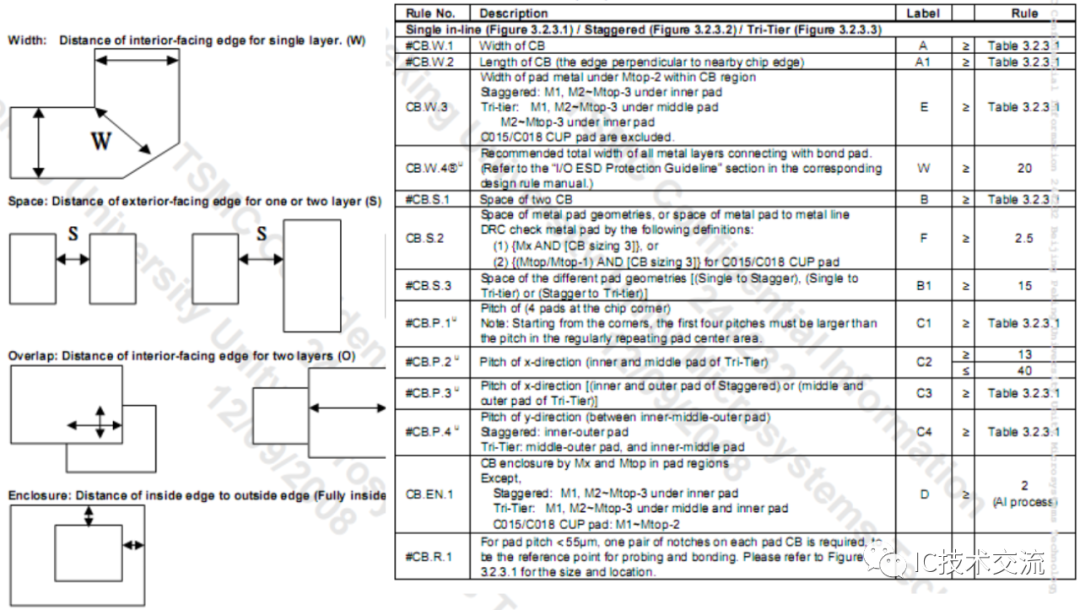

Fab的要求,會給IC后端一個drc的rule文件,包含所有物理要求,例如線寬度,線間距,相鄰層的正交距離等。

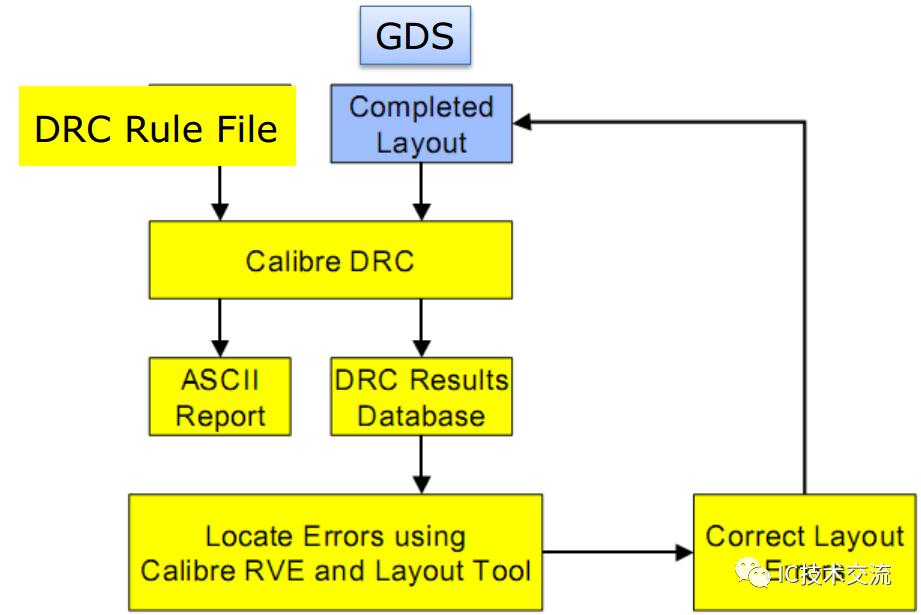

DRC檢查工具使用Calibre DRC,檢查迭代過程如下如所示。

Antenna天線規則檢查

放置在電磁場中的金屬線(天線)產生電壓,電壓大到一定程度會損壞MOSFET柵極處的薄氧化物,將管子擊穿。在加工過程中,隨著金屬絲長度的增加,施加在柵氧化層上的電壓增加,天線規則定義了可接受的天線比率

天線比率:

與閘門連接的金屬面積閘門組合面積或者與閘門連接的金屬面積組合周長

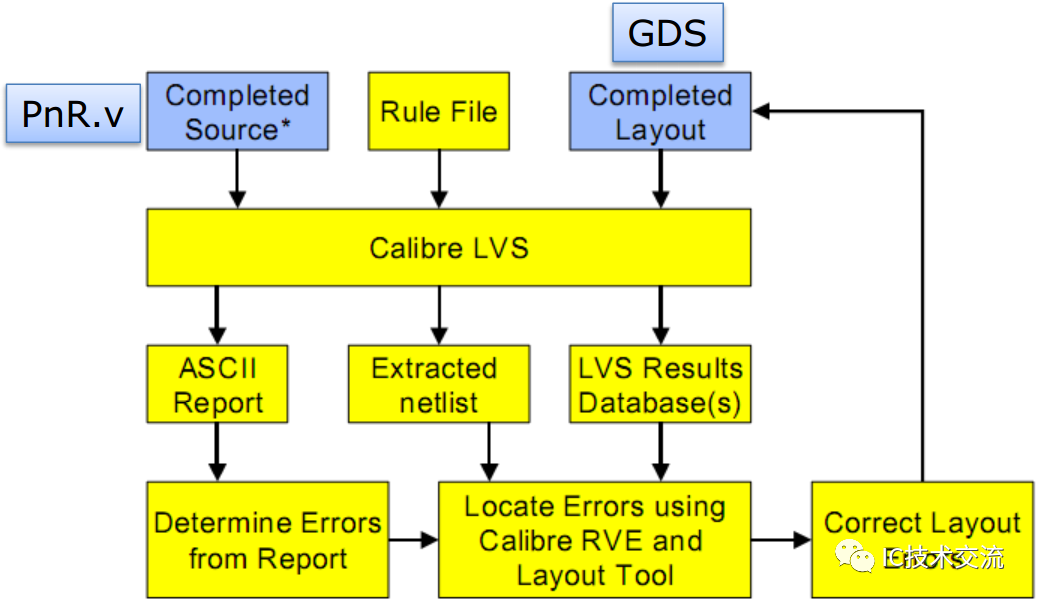

LVS:Layout vs. Schematic

前兩步形式驗證無法保證GDS和布局布線后的網表等價,所以需要LVS。

后面三步物理驗證統一使用Calibre工具。

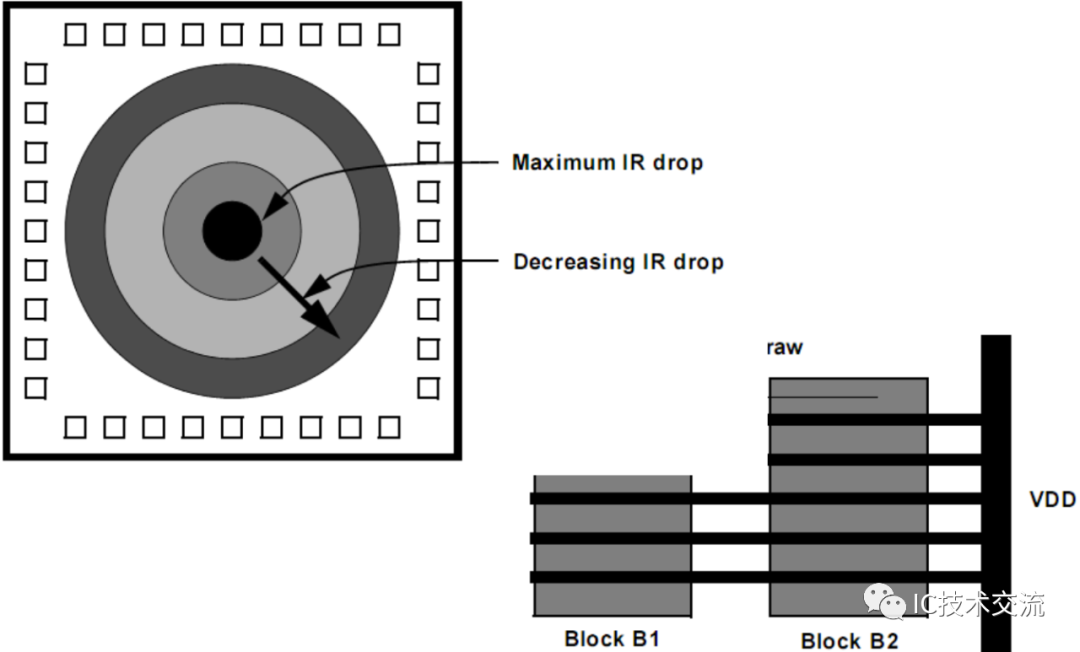

Power Signoff:IR Drop

對于整個芯片后端電壓而言,電壓由外部PAD供電,越往芯片內部走,電壓降越大。

Static IR drop

—VDD+VSS不能超過3%(寄存器)

—VDD+VSS不能超過5%(線wire bond)

Dynamic IR drop

—signoff要求的3-5倍

—掃描模式IR drop

漏電功耗通常在時鐘邊沿附近

當很多寄存器同時翻轉時,在一個小的時間窗口內分析IR drop

Power分析常用工具有Cadence的EPS和Synopsys的PrimeRail(該工具后續版本可能是PTPX)。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5421瀏覽量

123300 -

DFM

+關注

關注

8文章

476瀏覽量

29268 -

STA

+關注

關注

0文章

52瀏覽量

19223 -

電磁場

+關注

關注

0文章

797瀏覽量

47864 -

CTS

+關注

關注

0文章

35瀏覽量

14375

原文標題:IC后端概述(下)

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IC前端和后端設計的區別

數字IC后端(CAD)

數字IC后端設計介紹,寫給哪些想轉IC后端的人!

后端集成電路SAA7158電子資料

后端系統,后端系統是什么意思

IC前端設計(邏輯設計)和后端設計(物理設計)的詳細解析

IC設計前后端流程與EDA工具介紹

單片機上電復位后端口的狀態詳細概述

ic設計前端到后端的流程 ic設計的前端和后端的區別

IC后端概述(上)

IC后端概述(下)

IC后端概述(下)

評論