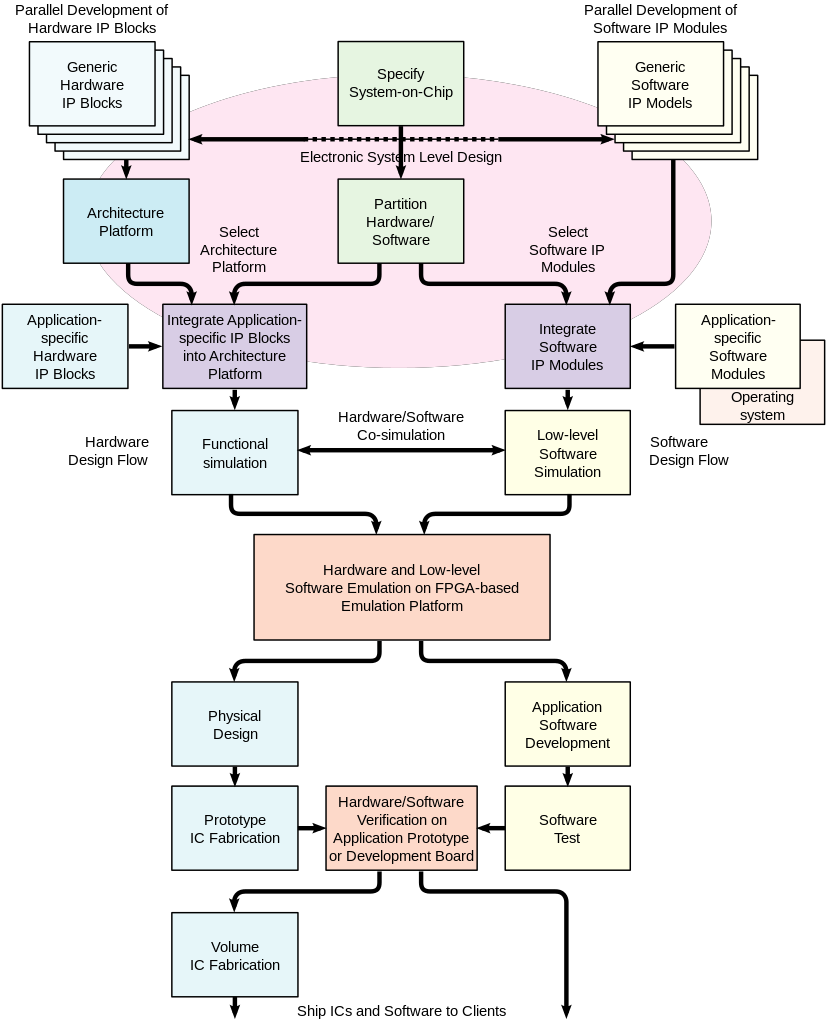

IC前端設(shè)計(jì)(邏輯設(shè)計(jì))和后端設(shè)計(jì)(物理設(shè)計(jì))的區(qū)分:

以設(shè)計(jì)是否與工藝有關(guān)來(lái)區(qū)分二者;從設(shè)計(jì)程度上來(lái)講,前端設(shè)計(jì)的結(jié)果就是得到了芯片的門級(jí)網(wǎng)表電路。

前端設(shè)計(jì)的流程及使用的EDA工具

1、架構(gòu)的設(shè)計(jì)與驗(yàn)證

按照要求,對(duì)整體的設(shè)計(jì)劃分模塊。架構(gòu)模型的仿真可以使用Synopsys公司的CoCentric軟件,它是基于System C的仿真工具。2、HDL設(shè)計(jì)輸入

設(shè)計(jì)輸入方法有:HDL語(yǔ)言(Verilog或VHDL)輸入、電路圖輸入、狀態(tài)轉(zhuǎn)移圖輸入。

使用的工具有:Active-HDL,而RTL分析檢查工具有Synopsys的LEDA。3、前仿真工具(功能仿真)

初步驗(yàn)證設(shè)計(jì)是否滿足規(guī)格要求。

使用的工具有:Synopsys的VCS,Mentor的ModelSim,Cadence的Verilog-XL,Cadence的NC-Verilog。4、邏輯綜合

將HDL語(yǔ)言轉(zhuǎn)換成門級(jí)網(wǎng)表Netlist。綜合需要設(shè)定約束條件,就是你希望綜合出來(lái)的電路在面積,時(shí)序等目標(biāo)參數(shù)上達(dá)到的標(biāo)準(zhǔn);邏輯綜合需要指定基于的庫(kù),使用不同的綜合庫(kù),在時(shí)序和面積上會(huì)有差異。邏輯綜合之前的仿真為前仿真,之后的仿真為后仿真。

使用的工具有:Synopsys的Design Compiler,Cadence的 PKS,Synplicity的Synplify等。5、靜態(tài)時(shí)序分析工具(STA)

在時(shí)序上,檢查電路的建立時(shí)間(Setuptime)和保持時(shí)間(Hold time)是否有違例(Violation)。

使用的工具有:Synopsys的Prime Time。6、形式驗(yàn)證工具

在功能上,對(duì)綜合后的網(wǎng)表進(jìn)行驗(yàn)證。常用的就是等價(jià)性檢查(Equivalence Check)方法,以功能驗(yàn)證后的HDL設(shè)計(jì)為參考,對(duì)比綜合后的網(wǎng)表功能,他們是否在功能上存在等價(jià)性。這樣做是為了保證在邏輯綜合過(guò)程中沒(méi)有改變?cè)菻DL描述的電路功能。

使用的工具有:Synopsys的Formality

后端設(shè)計(jì)的流程及使用的EDA工具

1. 數(shù)據(jù)準(zhǔn)備

對(duì)于 CDN 的 Silicon Ensemble而言后端設(shè)計(jì)所需的數(shù)據(jù)主要有是Foundry廠提供的標(biāo)準(zhǔn)單元、宏單元和I/O Pad的庫(kù)文件,它包括物理庫(kù)、時(shí)序庫(kù)及網(wǎng)表庫(kù),分別以.lef、.tlf和.v的形式給出。前端的芯片設(shè)計(jì)經(jīng)過(guò)綜合后生成的門級(jí)網(wǎng)表,具有時(shí)序約束和時(shí)鐘定義的腳本文件和由此產(chǎn)生的.gcf約束文件以及定義電源Pad的DEF(Design Exchange Format)文件。(對(duì)synopsys 的Astro 而言, 經(jīng)過(guò)綜合后生成的門級(jí)網(wǎng)表,時(shí)序約束文件 SDC 是一樣的,Pad的定義文件--tdf, .tf 文件 --technology file,Foundry廠提供的標(biāo)準(zhǔn)單元、宏單元和I/O Pad的庫(kù)文件 就與FRAM, CELL view, LM view形式給出(Milkway 參考庫(kù) and DB, LIB file)2. 布局規(guī)劃

主要是標(biāo)準(zhǔn)單元、I/O Pad和宏單元的布局。I/OPad預(yù)先給出了位置,而宏單元?jiǎng)t根據(jù)時(shí)序要求進(jìn)行擺放,標(biāo)準(zhǔn)單元?jiǎng)t是給出了一定的區(qū)域由工具自動(dòng)擺放。布局規(guī)劃后,芯片的大小,Core的面積,Row的形式、電源及地線的Ring和Strip都確定下來(lái)了。如果必要 在自動(dòng)放置標(biāo)準(zhǔn)單元和宏單元之后, 你可以先做一次PNA(power network analysis)--IR drop and EM .3.Placement -自動(dòng)放置標(biāo)準(zhǔn)單元

布局規(guī)劃后,宏單元、I/O Pad的位置和放置標(biāo)準(zhǔn)單元的區(qū)域都已確定,這些信息SE(Silicon Ensemble)會(huì)通過(guò)DEF文件傳遞給PC(Physical Compiler),PC根據(jù)由綜合給出的.DB文件獲得網(wǎng)表和時(shí)序約束信息進(jìn)行自動(dòng)放置標(biāo)準(zhǔn)單元,同時(shí)進(jìn)行時(shí)序檢查和單元放置優(yōu)化。如果你用的是PC +Astro那你可用write_milkway, read_milkway傳遞數(shù)據(jù)。4.時(shí)鐘樹生成(CTS Clock tree synthesis)

芯片中的時(shí)鐘網(wǎng)絡(luò)要驅(qū)動(dòng)電路中所有的時(shí)序單元,所以時(shí)鐘源端門單元帶載很多,其負(fù)載延時(shí)很大并且不平衡,需要插入緩沖器減小負(fù)載和平衡延時(shí)。時(shí)鐘網(wǎng)絡(luò)及其上的緩沖器構(gòu)成了時(shí)鐘樹。一般要反復(fù)幾次才可以做出一個(gè)比較理想的時(shí)鐘樹。---Clock skew.5.STA 靜態(tài)時(shí)序分析和后仿真

時(shí)鐘樹插入后,每個(gè)單元的位置都確定下來(lái)了,工具可以提出Global Route形式的連線寄生參數(shù),此時(shí)對(duì)延時(shí)參數(shù)的提取就比較準(zhǔn)確了。SE把.V和.SDF文件傳遞給PrimeTime做靜態(tài)時(shí)序分析。確認(rèn)沒(méi)有時(shí)序違規(guī)后,將這來(lái)兩個(gè)文件傳遞給前端人員做后仿真。對(duì)Astro 而言,在detail routing 之后,用starRC XT 參數(shù)提取,生成的E.V和.SDF文件傳遞給PrimeTime做靜態(tài)時(shí)序分析,那將會(huì)更準(zhǔn)確。6.ECO(Engineering Change Order)

針對(duì)靜態(tài)時(shí)序分析和后仿真中出現(xiàn)的問(wèn)題,對(duì)電路和單元布局進(jìn)行小范圍的改動(dòng).7. Filler的插入(padfliier, cell filler)

Filler指的是標(biāo)準(zhǔn)單元庫(kù)和I/O Pad庫(kù)中定義的與邏輯無(wú)關(guān)的填充物,用來(lái)填充標(biāo)準(zhǔn)單元和標(biāo)準(zhǔn)單元之間,I/O Pad和I/O Pad之間的間隙,它主要是把擴(kuò)散層連接起來(lái),滿足DRC規(guī)則和設(shè)計(jì)需要。8. 布線(Routing)

Global route-- Trackassign --Detail routing--Routingoptimization 布線是指在滿足工藝規(guī)則和布線層數(shù)限制、線寬、線間距限制和各線網(wǎng)可靠絕緣的電性能約束的條件下,根據(jù)電路的連接關(guān)系將各單元和I/O Pad用互連線連接起來(lái),這些是在時(shí)序驅(qū)動(dòng)(Timing driven ) 的條件下進(jìn)行的,保證關(guān)鍵時(shí)序路徑上的連線長(zhǎng)度能夠最小。--Timing report clear9. Dummy Metal的增加

Foundry廠都有對(duì)金屬密度的規(guī)定,使其金屬密度不要低于一定的值,以防在芯片制造過(guò)程中的刻蝕階段對(duì)連線的金屬層過(guò)度刻蝕從而降低電路的性能。加入Dummy Metal是為了增加金屬的密度。10. DRC和LVS

DRC是對(duì)芯片版圖中的各層物理圖形進(jìn)行設(shè)計(jì)規(guī)則檢查(spacing ,width),它也包括天線效應(yīng)的檢查,以確保芯片正常流片。LVS主要是將版圖和電路網(wǎng)表進(jìn)行比較,來(lái)保證流片出來(lái)的版圖電路和實(shí)際需要的電路一致。DRC和LVS的檢查--EDA工具Synopsy hercules/ mentor calibre/ CDN Dracula進(jìn)行的.Astro also include LVS/DRCcheck commands.11.Tape out

在所有檢查和驗(yàn)證都正確無(wú)誤的情況下把最后的版圖GDSⅡ文件傳遞給Foundry廠進(jìn)行掩膜制造。

-

IC

+關(guān)注

關(guān)注

36文章

6093瀏覽量

178322 -

eda

+關(guān)注

關(guān)注

71文章

2881瀏覽量

176406 -

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129551

原文標(biāo)題:IC設(shè)計(jì)前后端流程與EDA工具

文章出處:【微信號(hào):eetop-1,微信公眾號(hào):EETOP】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

IC前端和后端設(shè)計(jì)的區(qū)別

數(shù)字IC后端設(shè)計(jì)介紹,寫給哪些想轉(zhuǎn)IC后端的人!

數(shù)字IC前端和后端有何區(qū)別

IC設(shè)計(jì)完整流程分哪幾個(gè)部分

IC設(shè)計(jì)可以分為哪幾個(gè)部分?有哪些流程

IC前端設(shè)計(jì)是指什么

ASIC與大型邏輯設(shè)計(jì)實(shí)習(xí)教程

IC設(shè)計(jì)流程及各階段工具使用

解析邏輯設(shè)計(jì)和物理設(shè)計(jì)流程

IC設(shè)計(jì)完整流程及工具

IC前端設(shè)計(jì)工程師

IC設(shè)計(jì)完整流程

芯片設(shè)計(jì)包含哪些內(nèi)容 芯片設(shè)計(jì)流程詳解

IC前端設(shè)計(jì)(邏輯設(shè)計(jì))和后端設(shè)計(jì)(物理設(shè)計(jì))的詳細(xì)解析

IC前端設(shè)計(jì)(邏輯設(shè)計(jì))和后端設(shè)計(jì)(物理設(shè)計(jì))的詳細(xì)解析

評(píng)論