近日,為填補(bǔ)國(guó)內(nèi)集成電路市場(chǎng)上產(chǎn)業(yè)化CMP建模工具的空白,滿(mǎn)足芯片設(shè)計(jì)公司和晶圓制造廠的需求,廣立微正式推出CMP EXPLORER(簡(jiǎn)稱(chēng)“CMPEXP”)工具,保障芯片的可制造性和成品率,解決行業(yè)的痛點(diǎn)。

化學(xué)機(jī)械拋光(即Chemical Mechanical Planarization CMP)是集成電路制造工藝中的關(guān)鍵環(huán)節(jié),結(jié)合了化學(xué)反應(yīng)和機(jī)械研磨來(lái)實(shí)現(xiàn)硅片表面的高度平坦化。

隨著集成電路制造工藝的演進(jìn)迭代,納米器件尺寸不斷縮小,再加上集成程度提高及工藝層級(jí)越來(lái)越多,芯片在制造各階段的表面平坦度嚴(yán)重影響產(chǎn)品成品率及性能,其影響通過(guò)多層疊加和版圖特征效應(yīng)更加突出,可謂“差之毫厘,謬以千里”。如何實(shí)現(xiàn)CMP步驟的仿真、建模和優(yōu)化,一直是保障芯片成品率的重要挑戰(zhàn)。

即便在芯片設(shè)計(jì)時(shí)嚴(yán)格遵守了設(shè)計(jì)規(guī)則,對(duì)于一些工藝較敏感的設(shè)計(jì)Pattern,仍有可能在CMP階段形成碟型凹陷(Dishing)、介質(zhì)腐蝕(Erosion)和金屬厚度波動(dòng)等缺陷,從而造成互連線電阻、電容波動(dòng),甚至金屬互連短路和開(kāi)路。這樣一來(lái),后續(xù)制造步驟中的工藝窗口變窄,任何工藝上的小波動(dòng)能造成成品率問(wèn)題,因此,可制造性設(shè)計(jì)(Design for Manufacturing DFM)的角色更為重要,通過(guò)針對(duì)CMP步驟精準(zhǔn)仿真和建模,可以提前找出和預(yù)防CMP相關(guān)的芯片設(shè)計(jì)問(wèn)題。

進(jìn)軍DFM

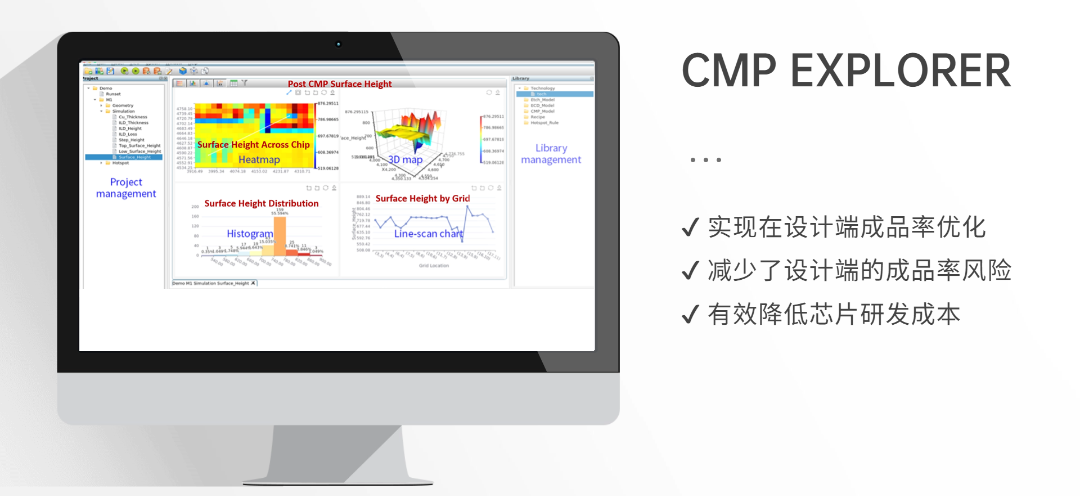

作為廣立微進(jìn)軍DFM領(lǐng)域的首款EDA工具,其可依據(jù)CMP工藝后的各測(cè)試結(jié)構(gòu)膜厚和表面形貌數(shù)據(jù)以及CMP工藝參數(shù),建立CMP模型。

設(shè)計(jì)人員可在芯片流片前,使用軟件內(nèi)的CMP模型對(duì)版圖進(jìn)行CMP仿真并進(jìn)行可制造性分析,對(duì)識(shí)別出的CMP工藝熱點(diǎn)提前進(jìn)行修復(fù),從而實(shí)現(xiàn)在設(shè)計(jì)端成品率優(yōu)化,減少了設(shè)計(jì)端的成品率風(fēng)險(xiǎn),有效降低芯片研發(fā)成本。

CMPEXP主要功能

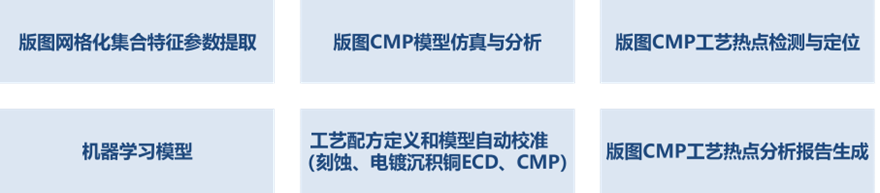

目前,廣立微的CMPEXP工具已完成了第二階段的開(kāi)發(fā),實(shí)現(xiàn)了業(yè)界廣泛使用的Cu CMP仿真與熱點(diǎn)檢查流程的所有功能,軟件的成熟度也已達(dá)到商用水平,其中工具特點(diǎn)包括:

考慮了接觸力學(xué)等物理和相關(guān)化學(xué)原理,同時(shí)結(jié)合快速傅里葉變換等數(shù)學(xué)手段,提供了高準(zhǔn)確性,魯棒性和泛化性的CMP模型。

采用了高效的分布式并行計(jì)算架構(gòu),有效地提升了模型校準(zhǔn)和仿真效率。

集成了先進(jìn)的模型校準(zhǔn)算法,大大地縮短了模型校準(zhǔn)時(shí)間周期并有效提升了校準(zhǔn)成功率。

采用數(shù)據(jù)表,散點(diǎn)圖,折線圖,柱狀圖,熱力圖,3D圖多種手段準(zhǔn)確直觀地展示模型校準(zhǔn),仿真與熱點(diǎn)檢測(cè)結(jié)果。

完善產(chǎn)品矩陣

這次CMPEXP EDA工具的推出,進(jìn)一步完善了廣立微的制造類(lèi)EDA的產(chǎn)品矩陣,同時(shí)與廣立微現(xiàn)有的成品率提升方案相互協(xié)同和補(bǔ)充,為集成電路企業(yè)提供更完備的解決方案,助力行業(yè)發(fā)展。

審核編輯:劉清

-

EDA工具

+關(guān)注

關(guān)注

4文章

271瀏覽量

32578 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1062瀏覽量

55455 -

CMP

+關(guān)注

關(guān)注

6文章

152瀏覽量

26494 -

DFM

+關(guān)注

關(guān)注

8文章

476瀏覽量

29256

原文標(biāo)題:廣立微重磅發(fā)布CMPEXP建模工具,豐富制造類(lèi)EDA產(chǎn)品矩陣

文章出處:【微信號(hào):gh_7b79775d4829,微信公眾號(hào):廣立微Semitronix】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

廣立微亮相2025中國(guó)浙江半導(dǎo)體裝備與材料博覽會(huì)

廣立微校準(zhǔn)實(shí)驗(yàn)室通過(guò)CNAS認(rèn)可

廣立微DFTEXP榮獲ISO 26262認(rèn)證

廣立微SEMICON China 2025圓滿(mǎn)落幕

EDA廠商廣立微獲評(píng)卓勝微2024年度優(yōu)秀供應(yīng)商

HFSS 自動(dòng)化建模工具

廣立微SemiMind平臺(tái)接入DeepSeek-R1大模型

SOLIDWORKS 2025集成式建模和仿真

cmp項(xiàng)目管理工具的優(yōu)缺點(diǎn)

CMP的平坦化機(jī)理、市場(chǎng)現(xiàn)狀與未來(lái)展望

廣立微正式發(fā)布DE-YMS 2.0版本

如何通過(guò)建模與仿真提升電力電子組件的設(shè)計(jì)與性能?

廣立微輕量級(jí)DE-YMS Lite方案多維度提升良率管理

如何實(shí)現(xiàn)CMP步驟的仿真?廣立微重磅發(fā)布CMPEXP建模工具

如何實(shí)現(xiàn)CMP步驟的仿真?廣立微重磅發(fā)布CMPEXP建模工具

評(píng)論