1

Kevin一直認(rèn)為學(xué)習(xí)FPGA的朋友的邏輯思維能力應(yīng)該是比其他人要強(qiáng)很多的。在很多求職網(wǎng)站上都可以看到FPGA相關(guān)行業(yè)的招聘信息可能會(huì)有這樣的一條工作職責(zé):負(fù)責(zé)項(xiàng)目的邏輯設(shè)計(jì)。

在業(yè)內(nèi),F(xiàn)PGA工程師也被稱(chēng)為邏輯工程師,而FPGA工程師寫(xiě)的Verilog代碼也被稱(chēng)為邏輯代碼。

上述信息均表明,F(xiàn)PGA工程師的邏輯思維能力應(yīng)該是極強(qiáng)的。

2

FPGA工程師遇到問(wèn)題一般都是會(huì)非常淡定的去分析問(wèn)題的原因,而不是看到項(xiàng)目出現(xiàn)了某個(gè)問(wèn)題就像個(gè)無(wú)頭蒼蠅到處亂改代碼,改完之后再試,試了不行再改,在“改了又試,試了又改”這條路上糾纏不清。如果進(jìn)入到這種模式,那只能說(shuō)明這完全不是一個(gè)稱(chēng)職的FPGA工程師。

不過(guò)很不幸,在很多初學(xué)者學(xué)習(xí)FPGA的時(shí)候,往往會(huì)進(jìn)入到“改了又試,試了又改”這種死循環(huán)的狀態(tài)中。出現(xiàn)這種情形的原因,就是缺乏深度思考。

深度思考,往往比努力修改代碼重要,修改代碼是要在經(jīng)過(guò)深度思考的前提下進(jìn)行的。

那如何進(jìn)行深度思考呢?

第一點(diǎn),需要仔細(xì)觀(guān)察問(wèn)題的現(xiàn)象。每一個(gè)錯(cuò)誤的現(xiàn)象都不是憑空出現(xiàn)的,而出現(xiàn)了問(wèn)題之后,就必須要對(duì)錯(cuò)誤的現(xiàn)象進(jìn)行觀(guān)察。

第二點(diǎn),仔細(xì)觀(guān)察現(xiàn)象之后,接著就需要進(jìn)行深度分析了。在分析的過(guò)程中,一定要對(duì)涉及到此問(wèn)題的所有因素進(jìn)行排查。要做到這一點(diǎn),就必須要懷疑一切與此相關(guān)、可能造成該錯(cuò)誤現(xiàn)象的條件。

第三點(diǎn),雖然是懷疑一切可能會(huì)觸發(fā)此錯(cuò)誤現(xiàn)象的因素,但也需要進(jìn)行一個(gè)預(yù)排查的過(guò)程。就是說(shuō),需要先排除一些經(jīng)過(guò)邏輯推理后能確定不會(huì)造成出現(xiàn)問(wèn)題的因素。

第四點(diǎn),排查了部分因素之后,那就需要多剩下的不能確定的因素進(jìn)行試驗(yàn),在有試驗(yàn)結(jié)果或現(xiàn)象的基礎(chǔ)上再進(jìn)行分析,分析什么呢?分析實(shí)驗(yàn)結(jié)果,如果改了代碼的某個(gè)地方,問(wèn)題一下子解決了,那肯定就說(shuō)明這一因素一定是會(huì)造成問(wèn)題的。如果不是這個(gè)因素,那就再繼續(xù)做實(shí)驗(yàn),做完試驗(yàn)后在繼續(xù)分析,直到找到真正能產(chǎn)生問(wèn)題的那個(gè)錯(cuò)誤為止。

3

Kevin這段時(shí)間做的一個(gè)項(xiàng)目,在常溫下產(chǎn)品能穩(wěn)定工作,在低溫(-40℃)下偏偏不能正常工作。

對(duì)于這一點(diǎn),整個(gè)項(xiàng)目組的人員認(rèn)為的問(wèn)題的因素很多:

第一,懷疑邏輯代碼有問(wèn)題;

第二,低溫下FPGA的參考時(shí)鐘失鎖,不夠穩(wěn)定;

第三,所選FPGA的型號(hào)的工作溫度達(dá)不到-40攝氏度,也就是在低溫下FPGA掛掉了;

。。。。。。。

當(dāng)然,項(xiàng)目組認(rèn)為會(huì)引起該問(wèn)題的因素還有很多,Kevin就不一一列舉了。

Kevin舉這個(gè)例子的目的,就是告訴大家,遇到問(wèn)題,一定要深度分析會(huì)引發(fā)該問(wèn)題的所有因素。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1645文章

22049瀏覽量

618379 -

Verilog語(yǔ)言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8555

原文標(biāo)題:FPGA工程師的項(xiàng)目邏輯思維

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

RISC-V 的平臺(tái)思維和生態(tài)思維

FPGA在機(jī)器學(xué)習(xí)中的具體應(yīng)用

FPGA從0到1學(xué)習(xí)資料集錦

FPGA+AI王炸組合如何重塑未來(lái)世界:看看DeepSeek東方神秘力量如何預(yù)測(cè)......

解密邏輯單元與CoreScore得分的關(guān)系

FPGA 實(shí)時(shí)信號(hào)處理應(yīng)用 FPGA在圖像處理中的優(yōu)勢(shì)

華為亮相自然資源數(shù)字化技術(shù)骨干培訓(xùn)班

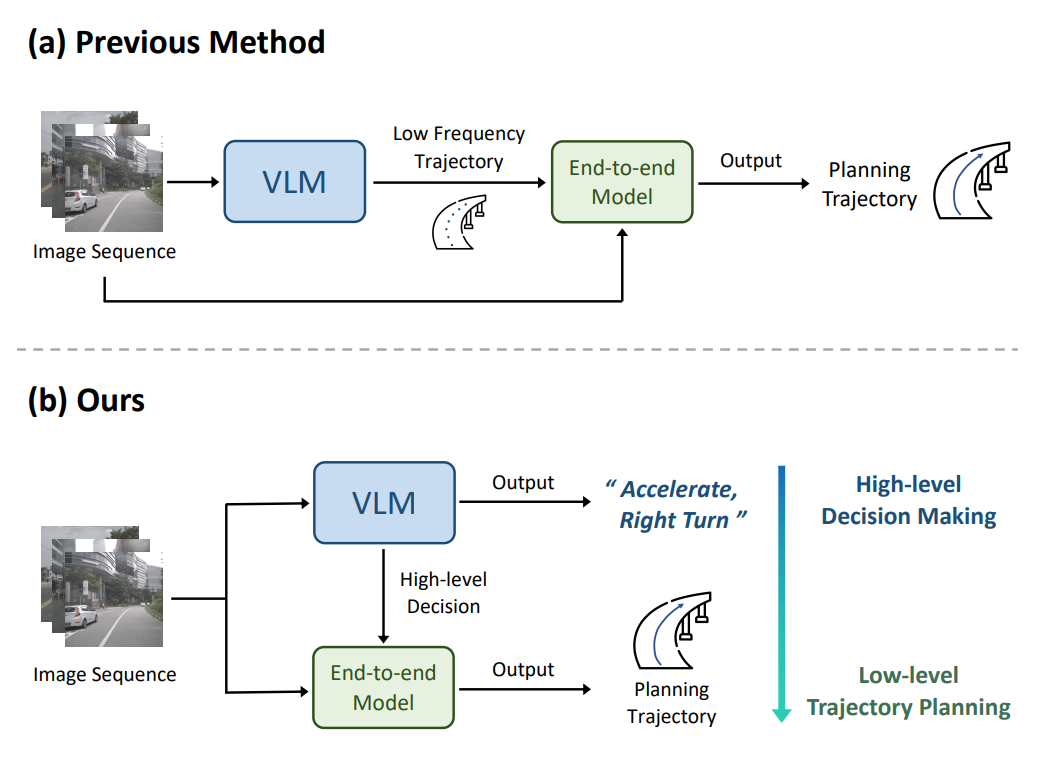

連接視覺(jué)語(yǔ)言大模型與端到端自動(dòng)駕駛

FPGA朋友邏輯思維能力的學(xué)習(xí)

FPGA朋友邏輯思維能力的學(xué)習(xí)

評(píng)論