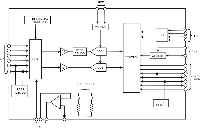

近年來,數字射頻接收器技術取得了巨大進步,這主要得益于高速ADC的性能發展。直接轉換、中頻采樣以及軟件定義的無線電架構開始在現代射頻接收器設計中普及。現在ADC中也包含許多以前在獨立器件中使用或者通過軟件實現的數字信號處理 (DSP) 功能;選擇適合某個系統的正確ADC并不僅僅是選擇分辨率(位數)和采樣速率。

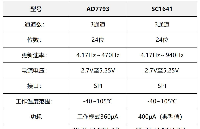

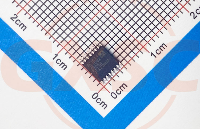

如今的高速/高分辨率ADC是具有眾多規格和性能特征的復雜系統。國產芯熾的雙通道12位20/40/65/80MSps ADC SC1232非常適合高靈敏度的接收機應用,并且改善了那些在接收機設計中最為重要的參數:數字化帶寬采樣、保持帶寬采樣、信噪比等。

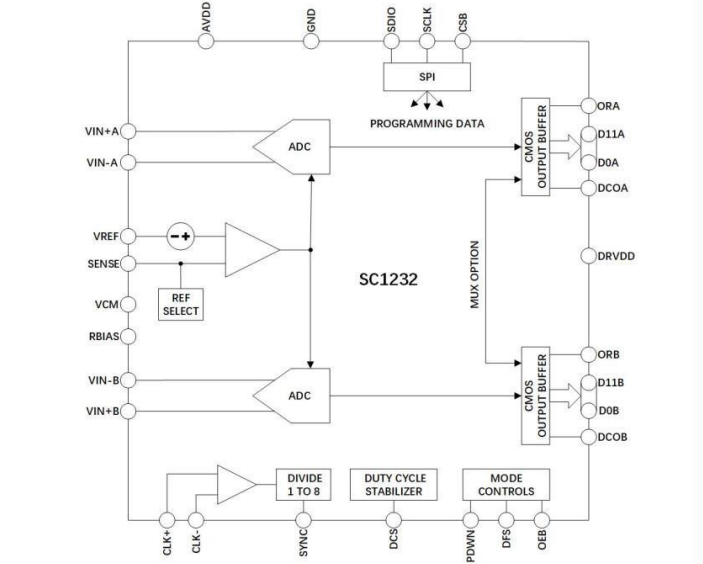

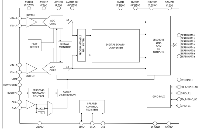

SC1232 ADC內部采用的是多級差分流水線架構,內置輸出糾錯邏輯,在 80MSPS數據速率時可提供14位精度,并保證在整個工作溫度范圍內無失碼。該ADC內置多種功能特性,可使器件的靈活性達到最佳、系統成本最低,例如可編程時鐘與數據對準、生成可編程數字測試碼等。可獲得的數字測試碼包括內置固定碼和偽隨機碼,以及通過串行端口接口(SPI)輸入的用戶自定義測試碼。

SC1232主要性能:

?1.8V 電源供電

?1.8V至3.3V輸出電源

?低功耗:每個通道31mW(20MSPS)

每個通道66mW(80MSPS)

?信噪比(SNR):72.5dBFS(30.5MHz輸入)

69dBFS(200MHz輸入)

?無雜散動態范圍(SFDR):82dBc(30.5MHz輸入)

74dBc(200MHz輸入)

?微分非線性(DNL):±0.2LSB(典型值)

?片內基準電壓源和采樣保持電路

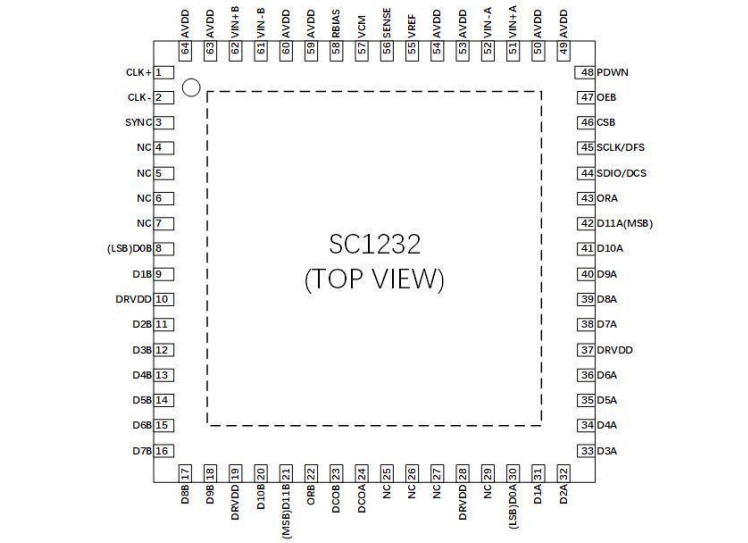

?QFN-64封裝9mm×9mm

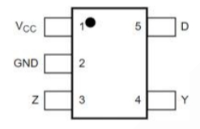

SC1232采用一個差分時鐘輸入來控制所有內部轉換周期。數字輸出數據格式為偏移二進制、格雷碼或二進制補碼。每個ADC通道均有一個數據輸出時鐘(DCO),用來確保接收邏輯具有正確的鎖存時序。該器件支持1.8V和 3.3V兩種CMOS電平,輸出數據可以在單條輸出總線上多路復用。

注:如涉及作品版權問題,請聯系刪除。

-

接收器

+關注

關注

15文章

2562瀏覽量

73389 -

國芯思辰

+關注

關注

0文章

1184瀏覽量

1698

發布評論請先 登錄

國芯思辰|替代AD9231BCPZ,國產12位SC1232用于數字射頻接收器

國芯思辰|替代AD9231BCPZ,國產12位SC1232用于數字射頻接收器

評論