摘要:

為了滿足某大型旋轉(zhuǎn)機(jī)械設(shè)備在監(jiān)測過程中實時性高精度多通道的采集需求,提出了一種基于FPGA的多通道振動信號采集檢測系統(tǒng)的設(shè)計方案。系統(tǒng)采用主/從式FPGA架構(gòu),在強(qiáng)噪聲環(huán)境下實現(xiàn)了采樣頻率為100 kHz的128通道并行實時數(shù)據(jù)采集功能。然后通過設(shè)計一種參數(shù)可調(diào)的隨機(jī)共振信號檢測系統(tǒng),提高了信號信噪比,增強(qiáng)了系統(tǒng)在旋轉(zhuǎn)環(huán)境下檢測的準(zhǔn)確性。經(jīng)測試驗證,該系統(tǒng)具有良好的實時性、穩(wěn)定性和有效性。

0 引言

隨著現(xiàn)代工業(yè)的飛速發(fā)展,人們對旋轉(zhuǎn)設(shè)備的需求愈加迫切,如風(fēng)力發(fā)電、大型煉鋼設(shè)備等旋轉(zhuǎn)設(shè)備的應(yīng)用。大型旋轉(zhuǎn)機(jī)械設(shè)備雖然極大地提高了生產(chǎn)率,但其突發(fā)性的故障率偏高,一旦停機(jī)就會造成較大的損失[1]。加強(qiáng)對旋轉(zhuǎn)機(jī)械的狀態(tài)檢測和診斷工作,有助于減少旋轉(zhuǎn)機(jī)械故障率,大幅度降低機(jī)械的維修費用和縮短維修時間,提高設(shè)備運行的經(jīng)濟(jì)效益。傳統(tǒng)的多通道振動信號采集系統(tǒng)多以DSP和ARM作為控制核心,存在功能簡單、通道數(shù)少、時鐘頻率低和實時性差等缺點[2-3]。 與DSP和ARM相比,F(xiàn)PGA在數(shù)據(jù)采集領(lǐng)域發(fā)揮著重要的作用。FPGA具有時鐘頻率高、內(nèi)部延時小、運算速度快、開發(fā)周期短、抗干擾能力強(qiáng)、編程配置靈活、內(nèi)部資源豐富等優(yōu)點,非常適用于數(shù)據(jù)高數(shù)采集和處理[4-6]。本文提出了一種基于主/從式FPGA架構(gòu)的128通道振動信號檢測方案,系統(tǒng)采用了高精度A/D芯片AD7606,同時結(jié)合了FPGA的并行數(shù)據(jù)處理能力實現(xiàn)了采集信號的隨機(jī)共振檢測,保證了采集系統(tǒng)的準(zhǔn)確性和穩(wěn)定性。

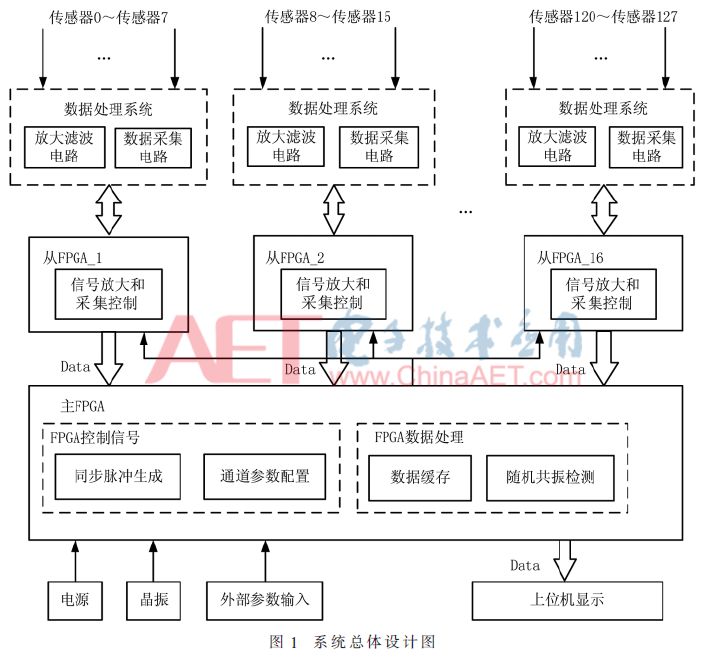

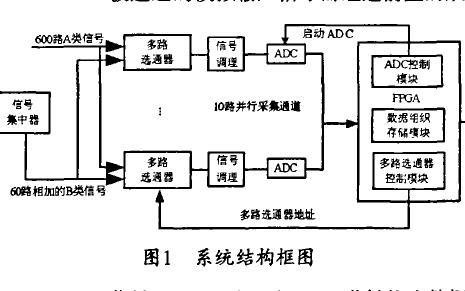

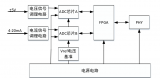

1 系統(tǒng)總體設(shè)計

本系統(tǒng)總體設(shè)計如圖1所示,系統(tǒng)由信號調(diào)理系統(tǒng)、FPGA控制系統(tǒng)和FPGA數(shù)據(jù)處理系統(tǒng)三部分構(gòu)成。其中信號調(diào)理系統(tǒng)由放大濾波電路和AD7606采集電路構(gòu)成,主要實現(xiàn)將傳感器發(fā)出的微弱信號進(jìn)行放大和濾波后發(fā)送到AD7606芯片中,將采集到的模擬信號轉(zhuǎn)化為數(shù)字信號。FPGA控制系統(tǒng)由主FPGA控制系統(tǒng)和從FPGA控制系統(tǒng)兩部分組成。從FPGA控制系統(tǒng)由16片Xilinx公司生產(chǎn)的Spartan3系列的FPGA構(gòu)成,主要實現(xiàn)程控放大器AD8250和AD8253的信號放大控制和AD7606同步數(shù)據(jù)采集控制。主FPGA控制系統(tǒng)由Xilinx公司生產(chǎn)的Spartan6系列的FPGA構(gòu)成,主要實現(xiàn)參數(shù)配置、同步時鐘生產(chǎn)、數(shù)據(jù)緩存等。FPGA數(shù)據(jù)處理系統(tǒng)由主FPGA實現(xiàn)數(shù)據(jù)的時序約束和隨機(jī)共振檢測處理功能,通過采用主從式FPGA架構(gòu),合理分配FPGA資源,完成整個系統(tǒng)的任務(wù)調(diào)度,克服FPGA輸出時的亞穩(wěn)態(tài)現(xiàn)象,使得系統(tǒng)具有性能穩(wěn)定、數(shù)據(jù)處理能力強(qiáng)、抗干擾性好等特點。

2 部分硬件電路設(shè)計

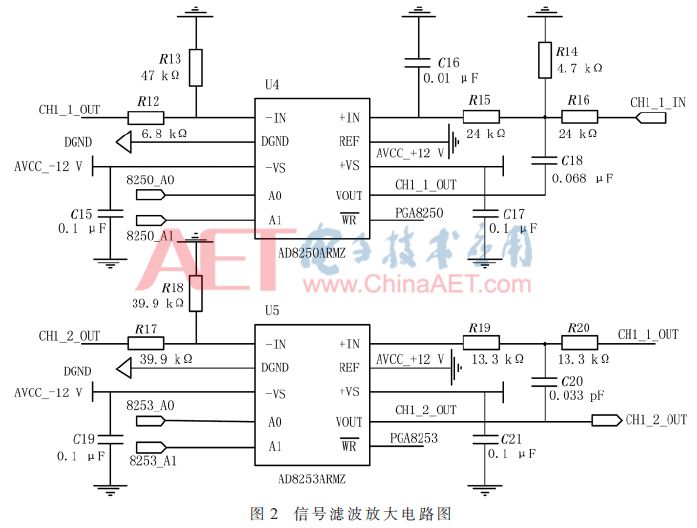

2.1 信號調(diào)理電路設(shè)計

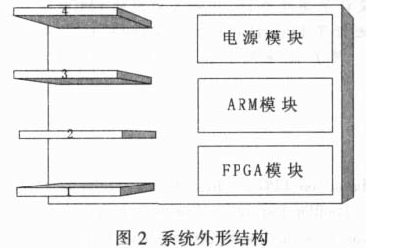

由于傳感器輸出信號范圍包含±0.025 V、±0.05 V、±0.1 V、±0.5 V 4個擋位,為保證采集精度,不能同時對整個量程進(jìn)行放大,需要采取分級放大的方式,且增益可調(diào)。本系統(tǒng)采用圖2所示的兩級放大電路結(jié)構(gòu),由于系統(tǒng)通過滑環(huán)進(jìn)行供電,在強(qiáng)噪聲環(huán)境下傳感器輸出信號首先利用AD8253和AD8250實現(xiàn)四階的巴特沃斯低通濾波器提高信噪比。

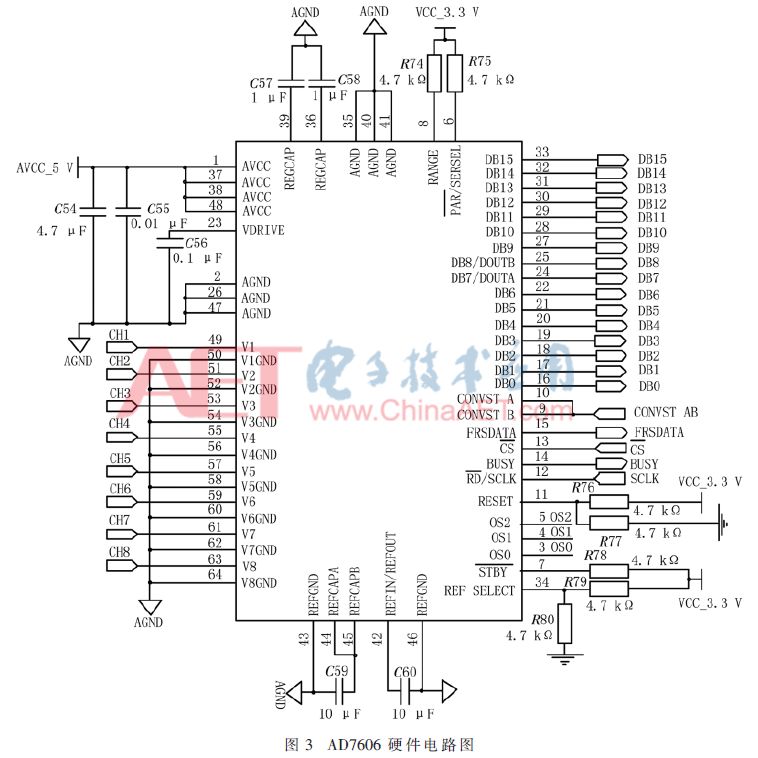

2.2 AD7606采集電路設(shè)計

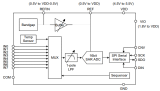

A/D數(shù)模轉(zhuǎn)換器是整個采集系統(tǒng)的核心,影響著系統(tǒng)的采集精度、采集速率和數(shù)據(jù)吞吐量,所以A/D芯片選型是采集系統(tǒng)中最關(guān)鍵的一步。系統(tǒng)采用ADI公司的高精度、低功耗、電荷再次分配逐次逼近型模數(shù)轉(zhuǎn)換芯片AD7606。該產(chǎn)品是一款8通道16位真差分具有二階抗混疊模擬濾波電路的同步采樣模數(shù)轉(zhuǎn)換芯片。本系統(tǒng)采用16片AD7606芯片構(gòu)成128通道的數(shù)據(jù)采集電路。AD7606硬件電路設(shè)計如圖3所示,將轉(zhuǎn)換芯片CONVST A與CONVST B短接在一起并施加同一個轉(zhuǎn)換信號能夠?qū)崿F(xiàn)8通道的數(shù)據(jù)同步轉(zhuǎn)換。

3 軟件設(shè)計

FPGA軟件設(shè)計主要劃分為主FPGA控制系統(tǒng)和從FPGA控制系統(tǒng)兩部分。其中,主FPGA控制系統(tǒng)主要完成同步時鐘生成、參數(shù)配置、數(shù)據(jù)緩存、隨機(jī)共振檢測等功能。而從FPGA主要完成數(shù)據(jù)組幀、程控放大控制和AD7606數(shù)據(jù)采集控制等。下面對部分核心模塊的設(shè)計進(jìn)行介紹。

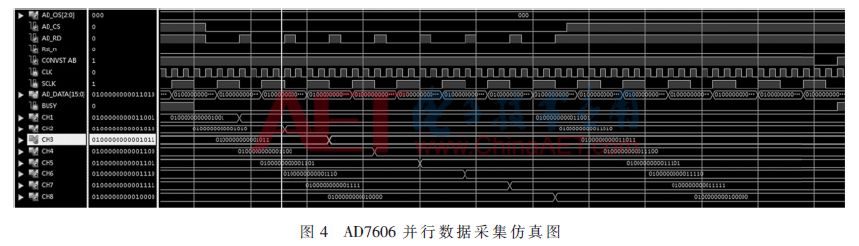

3.1 數(shù)據(jù)采集模塊

傳感器產(chǎn)生的微弱信號經(jīng)過濾波放大電路后,將其輸送入AD7606芯片實現(xiàn)數(shù)據(jù)采集功能。FPGA主要控制AD7606的轉(zhuǎn)換信號CONVST AB、片選信號CS和時鐘信號SCLK,實現(xiàn)芯片的采樣率調(diào)整和采樣啟停功能。如圖4所示,本模塊通過控制AD7606工作在并行數(shù)據(jù)輸出模式下,實現(xiàn)了系統(tǒng)在旋轉(zhuǎn)環(huán)境下采樣率為100 kHz的高速采集功能。從仿真圖中可以看出,采用并行輸出的方式能夠穩(wěn)定有效地將模擬信號轉(zhuǎn)換為數(shù)字信號進(jìn)行處理,經(jīng)過多次測試表明,通過采用并行數(shù)據(jù)輸出的方式,該芯片的采樣誤差小于0.1%。

3.2 數(shù)據(jù)緩存模塊

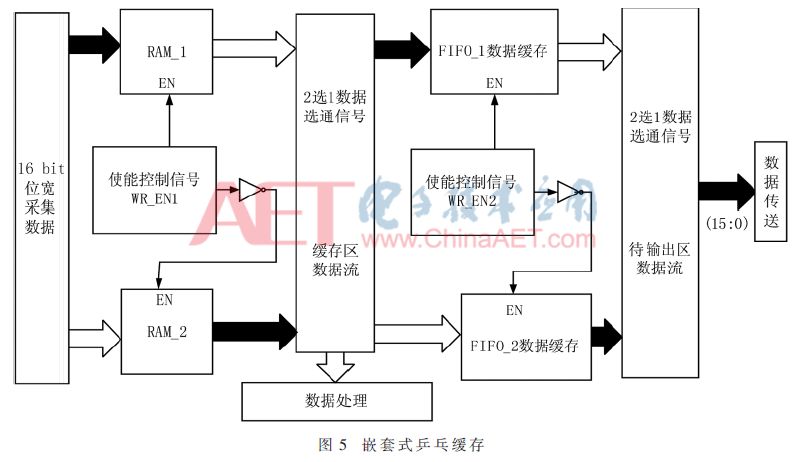

由于本系統(tǒng)為128路振動信號采集系統(tǒng),每完成一次采集會產(chǎn)生大量的待處理數(shù)據(jù),因此,設(shè)計了一種嵌套式的乒乓傳輸緩存方式,實現(xiàn)系統(tǒng)所需實時性數(shù)據(jù)采集功能。相比于傳統(tǒng)的乒乓式緩存[7],其效率更高,實用性更強(qiáng)。如圖5所示,本模塊有效地利用FPGA內(nèi)部IP核資源產(chǎn)生兩個不同的塊隨機(jī)存取存儲器(Random Access Memory,RAM)和先入先出隊列(First Input First Output,F(xiàn)IFO)進(jìn)行嵌套式的乒乓緩存。通過設(shè)置兩個不同的使能信號WR_EN1和WR_EN2,實現(xiàn)了塊RAM_1、塊RAM_2之間的乒乓緩存和FIFO_1、FIFO_2之間的乒乓緩存。如此周而復(fù)始,構(gòu)成了嵌套式乒乓緩存。通過數(shù)據(jù)緩存模塊可以很好地協(xié)調(diào)數(shù)據(jù)流在各模塊之間穩(wěn)定、實時有效地傳輸和處理。

3.3 隨機(jī)共振檢測模塊

由于系統(tǒng)處于強(qiáng)噪聲干擾的環(huán)境下,雖然添加了四階的巴特沃斯低通濾波電路,但在實際工程中旋轉(zhuǎn)環(huán)境下還是會產(chǎn)生大量的無法濾除的噪聲信號使有效的振動信號淹沒在噪聲中,無法正常檢測。所以采用隨機(jī)共振的檢測方法,在參數(shù)匹配的情況下將能量從噪聲轉(zhuǎn)移到有用信號中,使得輸出信噪比提高。下面依次從隨機(jī)共振的MATLAB仿真和FPGA實現(xiàn)兩個方面進(jìn)行介紹。

3.3.1 隨機(jī)共振的MATALB仿真

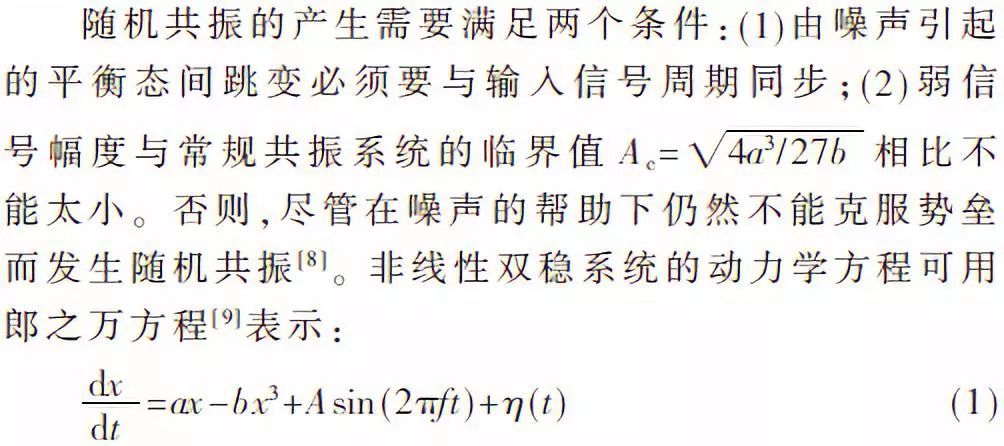

式中,a、b為非線性的雙穩(wěn)態(tài)系統(tǒng)參數(shù),通常取a=1,b=1。

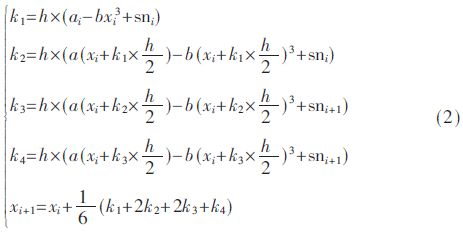

為了得到隨機(jī)共振的輸出,系統(tǒng)采用4階龍格-庫塔數(shù)值方法對式(1)進(jìn)行求解[10],其算法如式(2)所示:

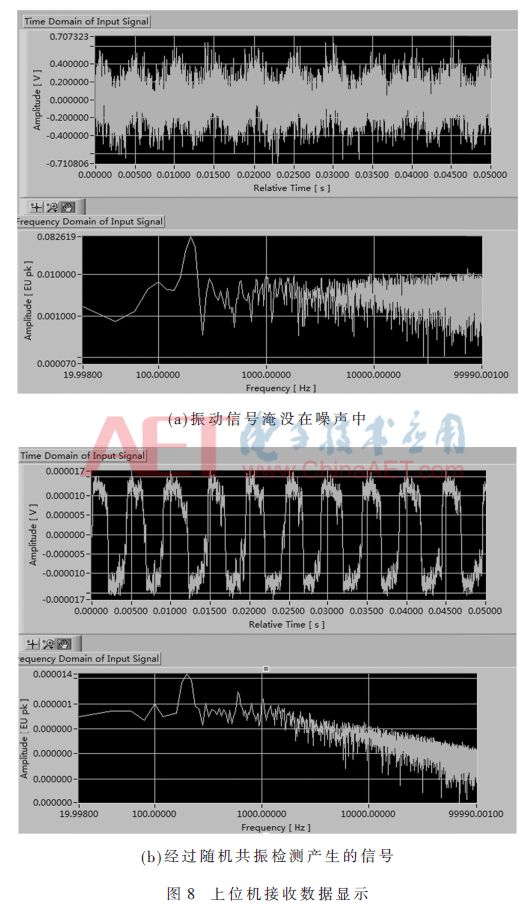

其中,xi表示x(t)的第i個采樣點,sni表示對輸入信號的第i個采樣點,計算步長h=1/f,f是對信號s(t)=Asin(2πft)+η(t)的采樣頻率,k為調(diào)整系數(shù)。隨機(jī)共振的MATLAB仿真圖如圖6所示,從上到下分別為原始有效信號、有效信號淹沒在噪聲中和隨機(jī)共振檢測輸出。由仿真圖可知,通過采用隨機(jī)共振檢測可以提高輸出信號的信噪比。

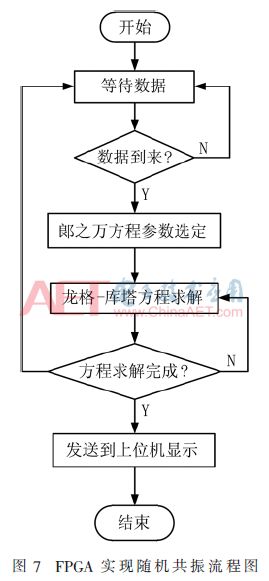

3.3.2 FPGA實現(xiàn)隨機(jī)共振檢測

隨機(jī)共振檢測算法由主FPGA通過采用補(bǔ)碼形式的定點數(shù)來實現(xiàn)郎之萬方程的求解,系統(tǒng)采用4階龍格庫塔的迭代方式,利用FPGA的并行數(shù)據(jù)處理能力實現(xiàn)了淹沒在噪聲中的振動信號的隨機(jī)共振檢測,本模塊的流程圖如圖7所示。將求解出的數(shù)據(jù)發(fā)送到上位機(jī)進(jìn)行實時顯示,圖8(a)是未使用FPGA實現(xiàn)的隨機(jī)共振檢測算法,由圖可知有效信號完全淹沒到噪聲中,無法識別。圖8(b)反映淹沒在噪聲中的有效信號經(jīng)過隨機(jī)共振模塊后檢測出原有振動信號的頻率,增強(qiáng)了輸出信號的信噪比。

4 結(jié)論

針對旋轉(zhuǎn)機(jī)械設(shè)備在強(qiáng)噪聲環(huán)境下難以檢測的問題,本文設(shè)計了一種基于FPGA的128通道振動信號采集檢測系統(tǒng),通過采用主/從式FPGA架構(gòu),極大地發(fā)揮出了FPGA的并行數(shù)據(jù)處理能力。系統(tǒng)采用了嵌套式的乒乓緩存方式,實現(xiàn)了數(shù)據(jù)的實時緩存和傳輸功能;然后,采用了FPGA在定點數(shù)補(bǔ)碼形式下的隨機(jī)共振檢測,增強(qiáng)了傳感器有效信號的信噪比,對大型旋轉(zhuǎn)機(jī)械的機(jī)械損耗和斷軸預(yù)判有著極其重要的作用。本系統(tǒng)已成功應(yīng)用于某旋轉(zhuǎn)機(jī)械的監(jiān)測項目中,具有一定的實用價值。

作者信息:

易志強(qiáng),韓 賓,鮮 龍,李 維

(西南科技大學(xué) 信息工程學(xué)院,四川 綿陽621010)

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21957瀏覽量

614057 -

控制系統(tǒng)

+關(guān)注

關(guān)注

41文章

6753瀏覽量

111801 -

噪聲

+關(guān)注

關(guān)注

13文章

1137瀏覽量

47882 -

數(shù)據(jù)采集

+關(guān)注

關(guān)注

40文章

6944瀏覽量

115695

原文標(biāo)題:【學(xué)術(shù)論文】旋轉(zhuǎn)環(huán)境下基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于CVI的多通道數(shù)據(jù)采集系統(tǒng)

基于FPGA的多通道同步數(shù)據(jù)采集存儲系統(tǒng)

基于PCI總線多通道數(shù)據(jù)采集系統(tǒng)的設(shè)計

基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計

基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計

基于FPGA和USB接口的多通道數(shù)據(jù)采集系統(tǒng)

基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計

如何使用FPGA進(jìn)行超多通道高速數(shù)據(jù)采集系統(tǒng)的構(gòu)成和設(shè)計過程資料概述

如何使用FPGA進(jìn)行多通道同步數(shù)據(jù)采集系統(tǒng)的設(shè)計

SAR型ADC GAD7699可用于真空環(huán)境下多通道數(shù)據(jù)采集卡

多通道數(shù)據(jù)采集系統(tǒng)的優(yōu)缺點

多通道數(shù)據(jù)采集系統(tǒng)的轉(zhuǎn)換誤差怎么算

多通道數(shù)據(jù)采集串?dāng)_問題怎么解決

多通道數(shù)據(jù)采集系統(tǒng)的設(shè)計的意義

FPGA的多通道數(shù)據(jù)采集傳輸系統(tǒng)

旋轉(zhuǎn)環(huán)境下基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計

旋轉(zhuǎn)環(huán)境下基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計

評論