作為一名DV,開發(fā)驗證環(huán)境,編寫驗證環(huán)境也算是必備基礎(chǔ)技能了。雖然每天都會coding,但最終寫出來的代碼,是一次性代碼,還是方法?

何為一次性代碼?可以從復(fù)用性考慮。

代碼的復(fù)用可大可小。IP驗證內(nèi)部,寫出的代碼是否可以在不同case間復(fù)用,還是僅針對具體的需求,點對點地寫代碼。一個簡單的例子就是,不同case的實現(xiàn),是在不停地復(fù)制粘貼,還是精簡的實現(xiàn);不同case的仿真,是否需要重新編譯驗證環(huán)境。

system或者soc驗證時,寫出的case是否可以方便地移植或者為他人所使用。一個長達(dá)數(shù)百行,for/if/while/fork來回嵌套的函數(shù),大概率會直接打消大家review的念頭。其大概率也是一次性代碼,復(fù)用性不高。

一次性代碼和方法的區(qū)別,換個角度看,也是是驗證環(huán)境的靜態(tài)和動態(tài)性的一種體現(xiàn)。如果環(huán)境中的某些參數(shù)或者特性在編譯階段就已經(jīng)確定,可認(rèn)為是靜態(tài)性的。如果某些參數(shù)或者code執(zhí)行在運行時才會確定,則是動態(tài)性的,即runtime。

使用動態(tài)性的代碼,可以使得驗證環(huán)境具備較好的靈活性。盡可能少的重新編譯環(huán)境,盡可能高效的debug case,在芯片規(guī)模較大時顯得尤為重要。尤其在使用一些如增量編譯,MSIE(multi snapshot incremental elaboration),simulation based snapshot方法時,對環(huán)境結(jié)構(gòu)和靈活性的要求會更高。這里分享一些靜態(tài)式和動態(tài)式的例子和思路。

ifdef/ifndef雙刃劍

條件編譯宏在環(huán)境開發(fā)中經(jīng)常會使用到,作者此前也分享過相關(guān)的總結(jié),讀者可參閱:SystemVerilog Macro宏使用場景小結(jié)。

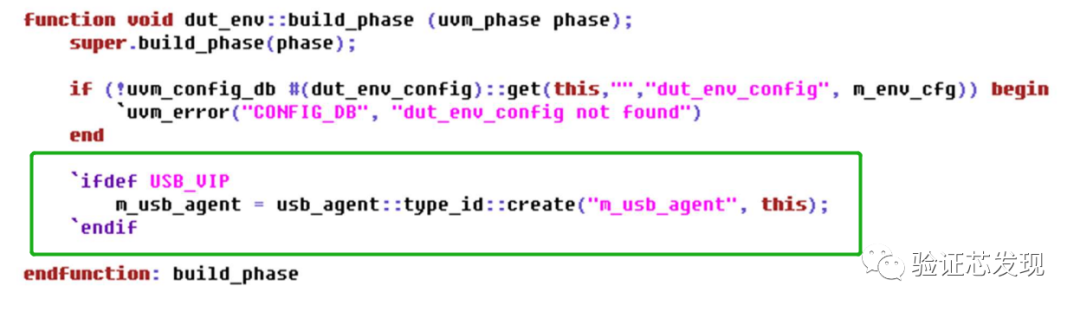

testbench中的env部分盡量減少使用條件編譯宏。比如下面的例子:

在環(huán)境部分使用ifdef/ifndef,就意味著在不同的場景下,需要重新編譯環(huán)境,是一種靜態(tài)式的思路。

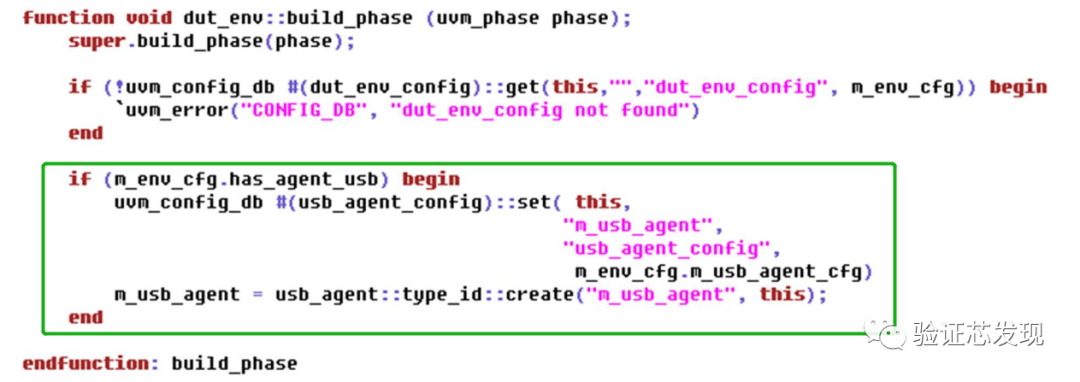

去除ifdef/ifndef,可以使用configuration來實現(xiàn),根據(jù)config的結(jié)果來決定要不要例化或者啟動某個組件。

用好plusargs

既然是runtime,動態(tài)式,那就從仿真命令中獲取數(shù)據(jù)好了。plusargs有兩個函數(shù),plusargs和plusargs。前者檢測是否有制定了某個參數(shù),后者用于獲取命令行輸入的參數(shù)值。

使用plusargs,可以在仿真前指定某個參數(shù)的取值,如時鐘頻率、module選擇、仿真超時域值等。甚至可以從plusargs中傳入對隨機參數(shù)的約束!而且UVM庫中也有uvm_cmdline_processor,用于處理命令行的輸入?yún)?shù)。同樣的,前面去除ifdef/ifndef的事情,也可以用plusargs來解決。

plusarg的使用可謂"五花八門"。如果后面有機會,作者也會做類似的分享,有興趣的讀者可私信交流和學(xué)習(xí)。總之,用好plusargs可以在case的調(diào)試時,帶來效率上的提升。

需求一直在變,做好數(shù)據(jù)驅(qū)動

不直接面向具體的數(shù)據(jù)編寫代碼,而是編寫對數(shù)據(jù)的處理和操作方法。比如環(huán)境中需要對A0~A9寄存器進(jìn)行配置,以完成DUT的初始化,或者需要對某些信號進(jìn)行force和check。需求變化和明天,不知道哪個會先來,雖然今天的需求是配置A0~A9, force a0~a9,明天可能就是變成B0~B9。

這里就可以做好通用的寄存器配置方法,需要配置的寄存器從plusargs或者配置文件中導(dǎo)入,而不是看到具體的A0或者B0寄存器。需要force和check的信號,可以從文件中導(dǎo)入,環(huán)境中編寫從force到check的邏輯方法。

數(shù)據(jù)驅(qū)動中,聯(lián)合數(shù)組是一個比較好的數(shù)據(jù)結(jié)構(gòu),在其他語言中也稱為哈希數(shù)組或者字典。這種數(shù)據(jù)結(jié)構(gòu)有key和value兩個屬性,你所需要的信息可以設(shè)置到key和value上,而不用關(guān)心key和value具體是什么,是數(shù)據(jù)驅(qū)動的天然好幫手。比如只使用一個int cfg[string]類型的聯(lián)合數(shù)組作為函數(shù)的入?yún)ⅲ涂梢詫崿F(xiàn)多個參數(shù)的配置傳遞,具體的配置參數(shù)名體現(xiàn)在cfg的string類型的key中,參數(shù)取值體現(xiàn)在cfg的int類型的value中。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19805瀏覽量

233543 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123333 -

SoC芯片

+關(guān)注

關(guān)注

1文章

636瀏覽量

35656 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19431 -

DUT

+關(guān)注

關(guān)注

0文章

190瀏覽量

12846

原文標(biāo)題:編寫動態(tài)的驗證環(huán)境

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于VMM驗證方法學(xué)的MCU驗證環(huán)境

基于VMM的驗證環(huán)境的驗證MCU指令實現(xiàn)設(shè)計

為什么要使用動態(tài)編寫安卓廣播的案例呢

SoC驗證環(huán)境搭建方法的研究

如何編寫dll文件

LINUX環(huán)境下CLIPS動態(tài)鏈接庫的實現(xiàn)方法

如何在代碼編寫器StudioIDE開發(fā)環(huán)境中使用腳本實用程序的詳細(xì)描寫

基于GameGAN的動態(tài)環(huán)境模擬

基于UVM驗證環(huán)境開發(fā)測試流程

C和C++編寫環(huán)境下LabVIEW如何調(diào)用動態(tài)庫?

一種半動態(tài)環(huán)境中的定位方法

編寫動態(tài)的驗證環(huán)境

編寫動態(tài)的驗證環(huán)境

評論