一、板卡概述

板卡為標準FMC接口子卡,ADC采用兩片TI的ADS54J60,4通道1Gsps,16bit,DAC采用2片TI的DAC39J84,4通道16bit1.25Gsps時鐘采用HMC7044,支持板上時鐘和外接時鐘;共10個SSMB接口,1個FMC/HPC接口。

二、性能指標

| 板卡功能 | 參數(shù) | 內(nèi)容 |

| ADC | 芯片型號 | ADS54J60 |

| 路數(shù) | 4路ADC, | |

| 采樣率 | 1Gsps | |

| 數(shù)據(jù)位 | 16bit | |

| 數(shù)字接口 | JESD204B | |

| 模擬接口 | 交流耦合 | |

| 模擬輸入 | ±1V | |

| 輸入阻抗 | 50Ω | |

| 模擬指標 | ||

| DAC | 芯片型號 | DAC39J84 |

| 路數(shù) | 4路DAC, | |

| 轉(zhuǎn)換率 | 1.25Gsps | |

| 數(shù)據(jù)位 | 16bit | |

| 數(shù)字接口 | JESD204B | |

| 模擬接口 | 交流耦合 | |

| 模擬輸出 | ±1V | |

| 輸出阻抗 | 50Ω | |

| 模擬指標 | 信噪比SNR:69.327dBFS | |

| 時鐘 | PLL芯片 | HMC7044 |

| 板載晶振 | 10MHz溫補晶振VCXO | |

| 外輸入時鐘 | 默認10MHz,3.3VLVTTL電平 | |

| 外觸發(fā) | 路數(shù) | 1路輸入 |

| 電平 | 3.3VLVTTL電平 | |

| 連接器類型 | FMC-LPC | ASP_134604_01 |

| 前面板 | 10路SSMB | |

| 板卡標準 | FMCANSI/VITA57.1-2008 | |

| 板卡尺寸 | 69X76.5mm | |

| 板卡重量 | (含散熱片) | |

| 板卡供電 | +12V@1A | |

| 板卡功耗 | 8W | |

| 工作溫度 | Industrial-20℃到+70℃ | |

| 支持母板 | Xilinxboard | V6、V7、KU、VU、ZYNQ、ZU開發(fā)板 |

| Orihardboard | 136、270、367、288、330、274、3、9 |

四、板卡應用

板卡配置FPGA母板用于模擬信號、無線電、光電、雷達的采集輸出場景。

三、軟件內(nèi)容

提供ISE或者Vivado版本的FMC接口AD輸入或者DA輸出,時鐘配置、外觸發(fā)接入的參考測試程序,支持的FPGA型號或者板卡見說明書表格。

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1643文章

21964瀏覽量

614110 -

adc

+關(guān)注

關(guān)注

99文章

6639瀏覽量

548264 -

FMC

+關(guān)注

關(guān)注

0文章

99瀏覽量

20002

發(fā)布評論請先 登錄

Why FPGA開發(fā)板喜歡FMC?

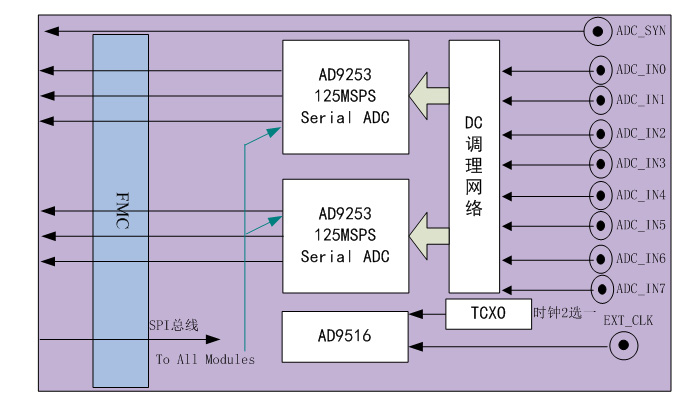

FMC子卡設計原理圖:FMC209-基于FMC的4路125MAD輸入、2路1GDA輸出子卡 中低頻信號采集

JESD204B使用說明

FMC子卡設計方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數(shù)據(jù)處理核心板

采用ADS54J20EVM同時對兩路模擬信號進行1GSPS采樣遇到的疑問求解

調(diào)試ADS52J90板卡JESD204B接口遇到的問題求解

DAC38J84EVM SYNC信號無法通過FMC-LHC接口輸入到FPGA,怎么解決?

FMC子卡原理圖設計:四通道1.25G/14bit數(shù)據(jù)采集

ADC16DX370 JESD204B串行鏈路的均衡優(yōu)化

FMC子卡原理圖設計: 4路 16bit 250M ADC+4路 16bit 2.8G DAC

從JESD204B升級到JESD204C時的系統(tǒng)設計注意事項

FMC子卡設計資料原理圖:FMC451-基于JESD204B的4路1GspsAD 4路1.25Gsps DA FMC子卡

FMC子卡設計資料原理圖:FMC451-基于JESD204B的4路1GspsAD 4路1.25Gsps DA FMC子卡

評論