一、測試的基本概念

IC驗(yàn)證,一般也稱“功能驗(yàn)證”,我們今天要講的,不是這個(gè),是它的簡化版:模塊測試,是設(shè)計(jì)工程師完成代碼設(shè)計(jì)后,需要自己做的這部分驗(yàn)證工作。IC驗(yàn)證,我們將會(huì)在后續(xù)文章中,專門講解。

為什么說設(shè)計(jì)工程師做的模塊測試是IC驗(yàn)證的簡化版?

在回答這個(gè)問題之前,我們先了解幾個(gè)概念:

這個(gè)幾個(gè)概念在軟件工程中都有介紹,IC設(shè)計(jì)驗(yàn)證中一樣存在這幾個(gè)概念涉及的工作,所以直接借用。

白盒測試,一般是針對代碼結(jié)構(gòu)進(jìn)行的測試,所以也有稱白盒測試為“結(jié)構(gòu)測試”。

黑盒測試,一般是行為測試,把設(shè)計(jì)當(dāng)黑盒子,不用看代碼不用針對代碼結(jié)構(gòu)進(jìn)行測試。我們前面提到的IC驗(yàn)證,通常指的“功能驗(yàn)證”,就屬于“黑盒測試”。

灰盒測試,介于白盒測試和黑盒測試之間,兼顧兩者優(yōu)點(diǎn)。

在實(shí)際工作中,設(shè)計(jì)工程師完成代碼設(shè)計(jì)之后,交給驗(yàn)證工程師之前,除了檢查語法、可綜合性之外(當(dāng)然還有其他檢查,設(shè)計(jì)剛?cè)腴T,不用關(guān)心這么多),還需要進(jìn)行基本的測試,這個(gè)基本的測試,原則上應(yīng)該是白盒測試。

實(shí)際上,因?yàn)槿吭O(shè)計(jì)工程師構(gòu)造測試?yán)齺碜龈采w完成白盒測試的工作量太大,一般都用更實(shí)際的做法:簡單的功能測試。

做法:確認(rèn)設(shè)計(jì)的代碼基本可以工作,基本的讀寫沒有問題后,就交給驗(yàn)證工程師來做“IC驗(yàn)證”,也就是功能驗(yàn)證。當(dāng)然,不同的團(tuán)隊(duì)對設(shè)計(jì)交付代碼質(zhì)量的要求不一樣,那么測試的內(nèi)容和工作量也有差異。

二、Timer測試方案

Timer的測試方案涵蓋的內(nèi)容包括:測試內(nèi)容、測試?yán)y試平臺結(jié)構(gòu),在實(shí)際操作中,有些團(tuán)隊(duì)略去了測試內(nèi)容的梳理和測試平臺結(jié)構(gòu)的設(shè)計(jì),僅僅構(gòu)造了一些這對基本功能的測試?yán)覀冞@部分保留這些內(nèi)容,但是做了精簡。

1.測試內(nèi)容

Timer模塊的白盒測試,簡化為基本的功能測試,如:

- 對總線接口的讀寫檢查

- 對模塊寄存器的復(fù)位值的檢查;

- 對寄存器讀寫的檢查;

- 對計(jì)數(shù)基本功能的檢查;

- 對代碼行、if語句各分支的執(zhí)行檢查等;

針對這些功能,構(gòu)造相應(yīng)的測試?yán)M(jìn)行測試。

2.測試?yán)?/strong>

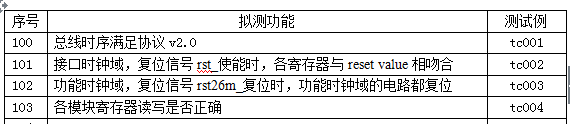

根據(jù)規(guī)格書上梳理待測試的功能。實(shí)際操作時(shí)有的工程師會(huì)簡化,經(jīng)測試基本功能,確認(rèn)設(shè)計(jì)可以動(dòng)起來。如下表格是測試?yán)钠巍?/p>

3.測試平臺結(jié)構(gòu)

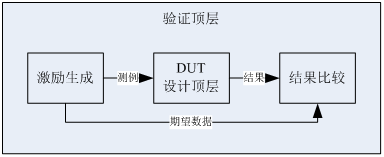

完成待測試功能的梳理和測試?yán)臉?gòu)造,我們接著要做是,設(shè)計(jì)構(gòu)造測試平臺(Testbench)。

DUT:待測試對象(Device Under Test),也就是我們前面用Verilog或VHDL寫的RTL設(shè)計(jì)代碼。

激勵(lì):DUT和testbench之間只能通過頂層接口連接,所以,所有的測試數(shù)據(jù)都必須按照頂層接口的時(shí)序要求,輸入進(jìn)DUT中。這里的測試數(shù)據(jù)也叫測試?yán)蛘邷y試向量。測試?yán)话闶遣捎弥苯訙y試?yán)M(jìn)行測試,這種測試方式針對性強(qiáng),能夠快速將模塊驅(qū)動(dòng)起來。

結(jié)果比較:等待DUT輸出結(jié)果(DUT會(huì)有標(biāo)識,或通過主機(jī)輪詢,或DUT自己有標(biāo)識接口),testbench必須按照頂層接口的時(shí)序要求,取出DUT的輸出結(jié)果,再與期望值比較,最后將比較結(jié)果打印出來,便于查看。

三、Timer測試平臺實(shí)現(xiàn)

實(shí)現(xiàn)語言: 可以用verilog語言,或者VHDL語言,或者SystemVerilog語言等。

仿真工具 :Modelsim、VCS、NC-Verilog/NC-VHDL

下面是平臺代碼實(shí)現(xiàn)的片段。

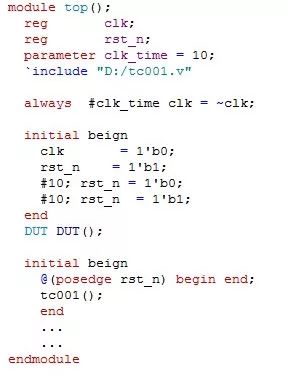

1. 頂層文件代碼

頂層包含:

- 時(shí)鐘和復(fù)位信號的定義;

- 時(shí)鐘周期的參數(shù)定義;

- 驗(yàn)證環(huán)境文件的導(dǎo)入;

- 時(shí)鐘的產(chǎn)生;

- 復(fù)位信號的產(chǎn)生;

- 模塊的例化;

- 在初始化中運(yùn)行測試?yán)蝿?wù);

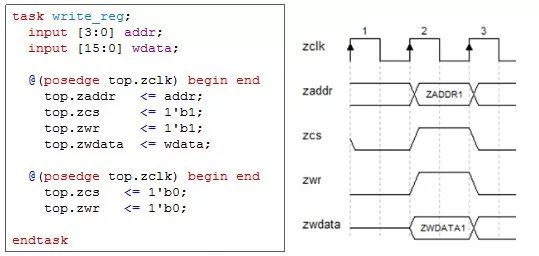

2 .總線激勵(lì)

假定Timer的總線接口是Z總線,下面的代碼就是實(shí)現(xiàn)一個(gè)Z總線的寫操作,將wdata寫入zaddr這個(gè)地址里面。

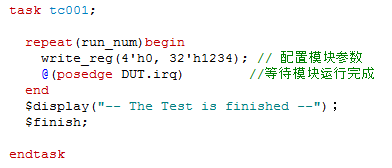

3.測試?yán)?/strong>

測試?yán)饕菍⑸厦娴目偩€驅(qū)動(dòng)task調(diào)用起來對模塊進(jìn)行驅(qū)動(dòng),讓模塊正常工作起來。同時(shí)設(shè)定一定的循環(huán)次數(shù),每一次新的運(yùn)行需要等待中斷到來之后進(jìn)行新的寄存器配置。

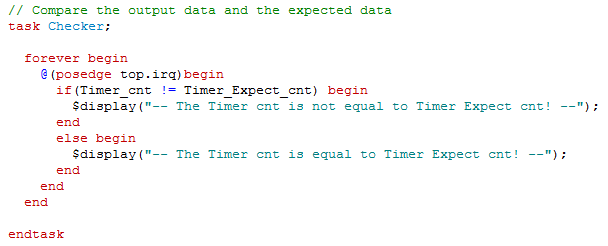

4.結(jié)果比較

為了提高debug效率,將從DUT出來的結(jié)果和理想結(jié)果進(jìn)行自動(dòng)對比,并將對比結(jié)果打印出來。

結(jié)果比較一般流程是等待DUT的中斷到來,然后讀取Timer的寄存器的值與期望值做比較。

四、測試平臺Debug注意事項(xiàng)

- 在對整個(gè)testbench進(jìn)行編譯時(shí)候,初期語法錯(cuò)誤較多,這時(shí)候需要多聯(lián)系上下文來check,很多時(shí)候工具報(bào)的問題不在出錯(cuò)誤的地方。

- Debug經(jīng)常遇到的問題是測試?yán)芩溃@種情況一般是等待的事件沒有等到,或者寄存器配置錯(cuò)誤。

-

寄存器

+關(guān)注

關(guān)注

31文章

5415瀏覽量

123214 -

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1345瀏覽量

105195 -

VHDL語言

+關(guān)注

關(guān)注

1文章

113瀏覽量

18494 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60621 -

DUT

+關(guān)注

關(guān)注

0文章

190瀏覽量

12818

發(fā)布評論請先 登錄

高壓絕緣電阻測試的使用注意事項(xiàng)

接地電阻測試儀使用與注意事項(xiàng)

Timer0和Timer1及Timer2定時(shí)器的C語言和匯編語言測試程序免費(fèi)下載

全自動(dòng)電容電感測試儀使用注意事項(xiàng)

防止Stress測試損壞注意事項(xiàng)

觸摸按鍵測試板PCB設(shè)計(jì)注意事項(xiàng)

扭力測試儀的操作安全有哪些注意事項(xiàng)?

Y電容的測試方法和注意事項(xiàng)

HK32MCU應(yīng)用筆記(十六)| HK32F103xC/D/E-Timer的應(yīng)用及注意事項(xiàng)

繼電保護(hù)測試儀測試時(shí)必須注意事項(xiàng)有哪些?

Timer測試方案 Timer測試平臺實(shí)現(xiàn) 測試平臺debug注意事項(xiàng)

Timer測試方案 Timer測試平臺實(shí)現(xiàn) 測試平臺debug注意事項(xiàng)

評論