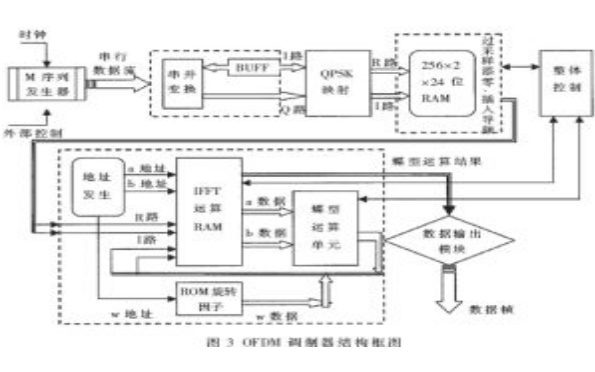

OFDM中調(diào)制使用IFFT,解調(diào)使用IFFT,在OFDM實現(xiàn)系統(tǒng)中,F(xiàn)FT和IFFT時必備的關(guān)鍵模塊。在使用Xilinx的7系列FPGA(KC705)實現(xiàn)OFDM系統(tǒng)時,有以下幾種選擇:

(1)在Vivado中調(diào)用官方的FFT的IP核(AXI-Stream總線);

(2)在Vivado HLS中調(diào)用官方的FFT的IP核(內(nèi)部FFT通信AXI-Stream總線),可以自己增加外部封裝接口類型;

(3)Verilog編寫FFT,很復(fù)雜,找到了一個1024點的并行流水線的,但是資源耗費太大,8192點時很難滿足,不采用;

(4)使用HLS用C語言自己編寫FFT,程序比較簡單,開發(fā)快,但是我需要100M時鐘下跑8192點FFT的時鐘時序約束不夠,跑不到100M;

最后還是選擇使用HLS里面調(diào)用FFT的庫,并且根據(jù)我們的項目需要,對其外部輸入輸出封裝成一個AXI-Master接口,并且在Devcpp里面使用C語言實現(xiàn)(不考慮延時和資源消耗等)對比結(jié)果,發(fā)現(xiàn)基本一致。

本節(jié)主要講Devcpp里的實現(xiàn)結(jié)果。

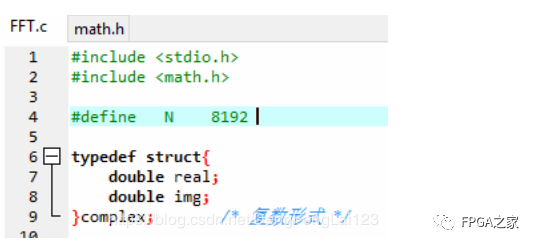

1.定義計算點數(shù)和復(fù)數(shù)類型

2.計算

(1)初始化蝶形因子;

(2)比特反轉(zhuǎn),變址運算;

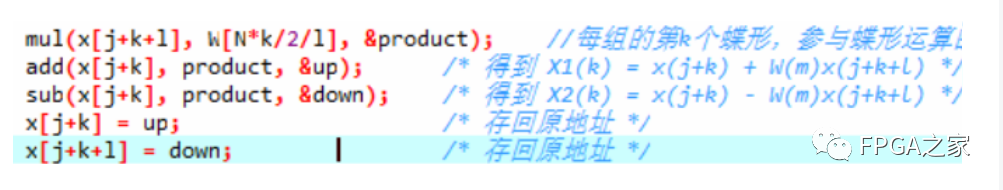

(3)FFT蝶形循環(huán)計算;

(4)計算功率,輸出結(jié)果;

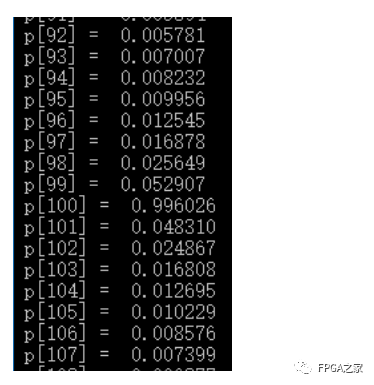

3.結(jié)果驗證

以100Hz的sin函數(shù)作為輸入信號,幅值-1~1,輸出功率最大值在p[100],趨近于1。

4.計算IFFT

(1)將輸入的復(fù)數(shù)取共軛;

(2)調(diào)用FFT;

(3)對輸出的數(shù)據(jù)取共軛;

完成。

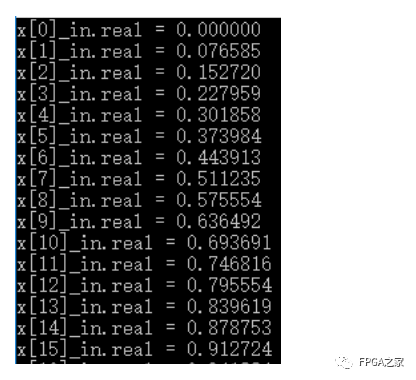

最初始的sin信號如下:

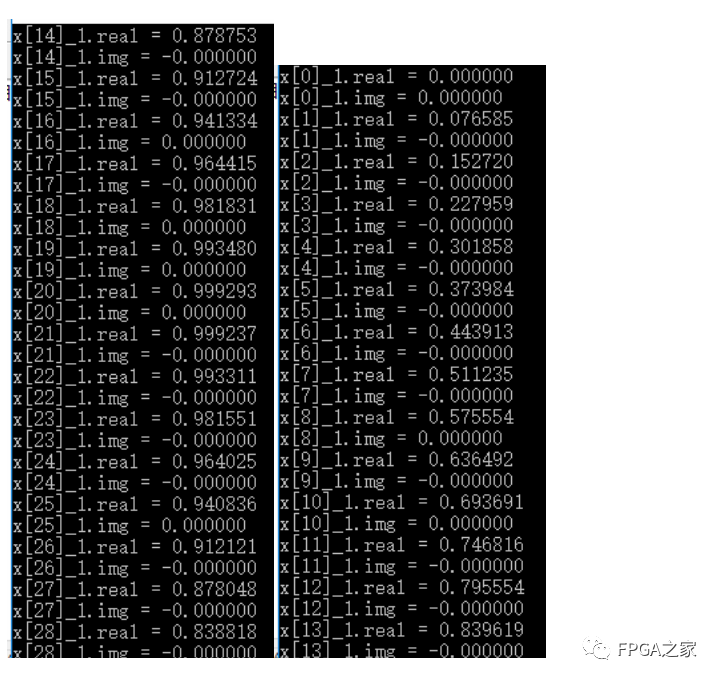

經(jīng)過FFT之后,對結(jié)果取共軛,并且縮小N點(8192)倍,再次調(diào)用FFT,對輸出取共軛,得到IFFT結(jié)果如下:

??審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21956瀏覽量

614004 -

Xilinx

+關(guān)注

關(guān)注

73文章

2182瀏覽量

124329 -

FFT

+關(guān)注

關(guān)注

15文章

443瀏覽量

60559 -

C語言

+關(guān)注

關(guān)注

180文章

7630瀏覽量

140244 -

HLS

+關(guān)注

關(guān)注

1文章

131瀏覽量

24637

原文標(biāo)題:FPGA實現(xiàn)OFDM通信——FFT與IFFT(1)——C語言實現(xiàn)N點FFT

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

應(yīng)用于LTE-OFDM系統(tǒng)的Viterbi譯碼在FPGA中的實現(xiàn)

【參考書籍】基于XILINX FPGA的OFDM通信系統(tǒng)基帶設(shè)計—史治國

【基于Xilinx FPGA的OFDM通信系統(tǒng)基帶設(shè)計】隨書光盤

adc采樣后數(shù)據(jù)無法實現(xiàn)ofdm(fft)解調(diào)

怎么使用xilinx系統(tǒng)生成器實現(xiàn)ofdm

怎么使用FPGA實現(xiàn)OFDM系統(tǒng)同步算法?

基于FPGA 的OFDM 寬帶數(shù)據(jù)通信同步系統(tǒng)設(shè)計與實現(xiàn)

OFDM系統(tǒng)中DAGC的應(yīng)用研究及FPGA實現(xiàn)

導(dǎo)頻疊加OFDM同步方法的FPGA實現(xiàn)

基于FPGA的OFDM系統(tǒng)設(shè)計與實現(xiàn)

應(yīng)用于LTE_OFDM系統(tǒng)的Viterbi譯碼在FPGA中的實現(xiàn)

如何使用FPGA設(shè)計和實現(xiàn)OFDM系統(tǒng)和OFDM中的FFT模塊設(shè)計及其FPGA實現(xiàn)

如何使用FPGA實現(xiàn)高速移動下的OFDM均衡器

從Xilinx FFT IP核到FPGA實現(xiàn)OFDM

基于FPGA的OFDM調(diào)制器設(shè)計與實現(xiàn)

使用Xilinx FPGA實現(xiàn)OFDM系統(tǒng)

使用Xilinx FPGA實現(xiàn)OFDM系統(tǒng)

評論