串行輸入 – 串行輸出 (SISO) 移位寄存器

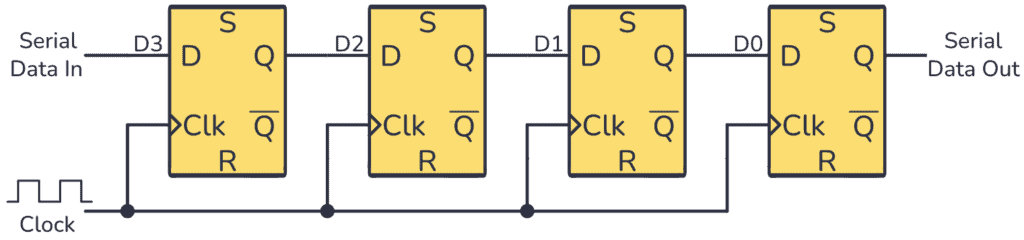

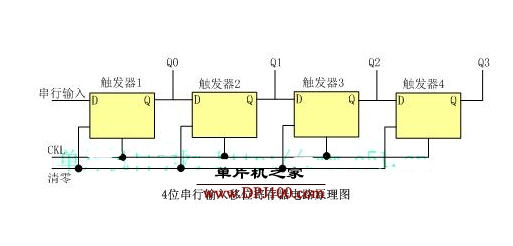

以下電路顯示了由D觸發器制成的串行輸入-串行輸出移位寄存器的結構:

該移位寄存器在串行數據輸入端僅接受一位數據。每次Clk輸入接收到有效的觸發信號時,它都會橫向移動到下一個D觸發器。觸發器中的有效觸發信號可以是上升沿(即從數字狀態0 到 1 ↑ 的變化)或下降沿(從 1 到 0 ↓ 的變化)。在本教程中,我們使用觸發器,通過上升沿信號觸發。

如您所見,上述電路有四個D觸發器。假設您將數字 1

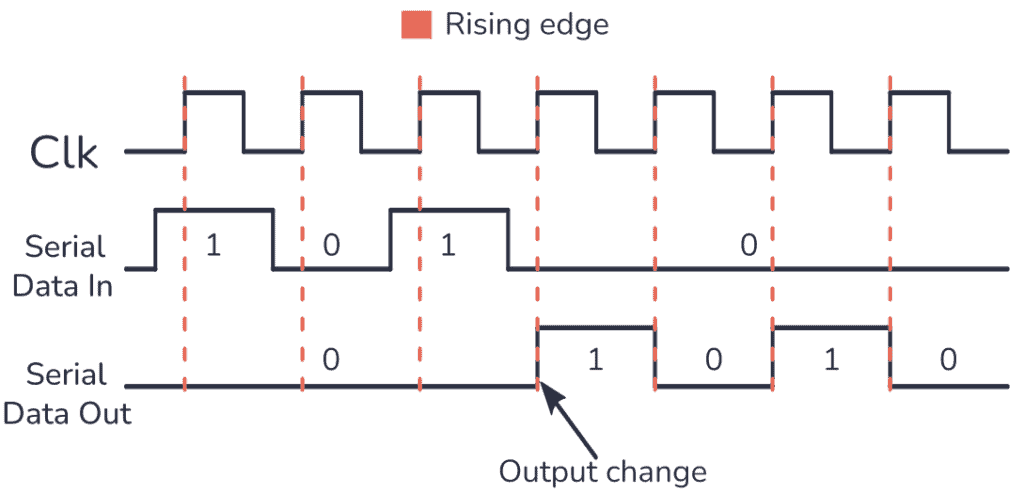

放入串行數據輸入中。輸入位需要四個上升沿信號才能到達串行數據輸出。您可以在下面的SISO移位寄存器時序圖中看到位的移動:

串行輸入 – 并行輸出 (SIPO) 移位寄存器

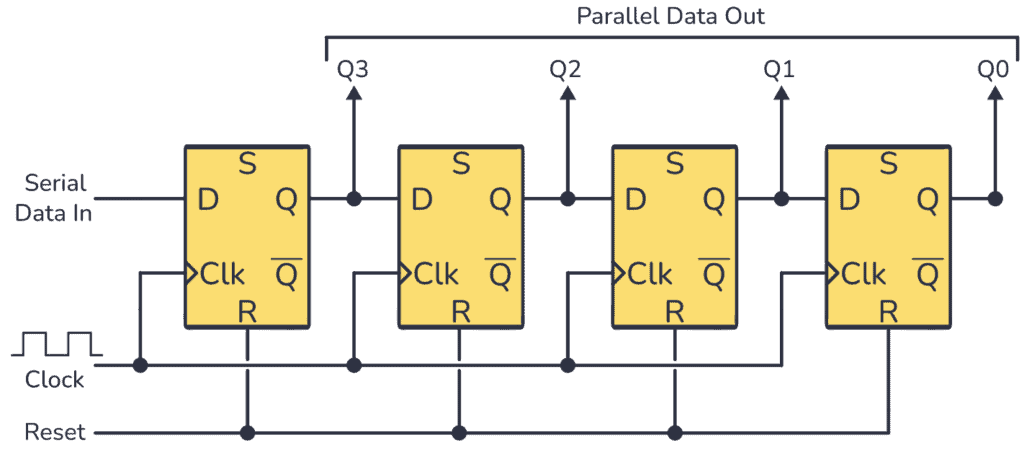

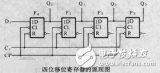

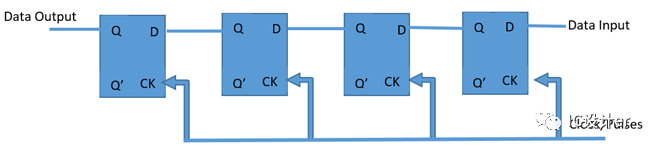

這種類型的移位寄存器與我們上面看到的SISO寄存器非常相似,但不同之處在于SIPO移位寄存器具有多個輸出。該移位寄存器具有來自每個觸發器的輸出引腳,以便您可以并行訪問這些位。讓我們看看它的電路:

該電路在串行數據輸入中一次接收一位。每當D觸發器中的Clk輸入收到上升沿信號時,該位都會從一個觸發器移動到另一個觸發器 - 從左到右。

由于 SIPO 版本具有并行輸出 Q0、Q1、Q2 和

Q3,因此您不必等待輸入位到達最后一個觸發器即可使用;它將在第一個觸發信號的Q3輸出端,在Q2中在第二個觸發信號中,第三個信號在Q1輸出端,最后在Q0中具有第四個上升沿。您有以下行為:

SIPO寄存器的一個常見實際示例是向Arduino或其他微控制器添加更多輸出引腳。例如,使用帶有Arduino的74HC595查看此示例。

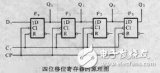

并行輸入 – 串行輸出 (PISO) 移位寄存器

該移位寄存器具有并行輸入,這意味著位同時分別加載到每個觸發器上。與輸入相反,輸出具有串行格式,這意味著每次觸發觸發器時僅輸出一位。

上述電路由四個D觸發器組成,其中時鐘信號在所有Clk輸入之間共享。每個D輸入都連接到多路復用器,多路復用器接收位輸入(IN0,IN1,IN2,IN3)和前一個觸發器的輸出(從左到右)。由于第一個觸發器缺少先前的觸發器,因此多路復用器的一個輸入放置在數字1中。

對于這種類型的寄存器,不需要上升沿信號來并行加載寄存器,因為輸入中已經存在位。但是,如果考慮上述具有四個觸發器的電路,則需要四個上升沿來卸載數據。這將從

IN0 中的位開始,然后是 IN1 中的位,然后是 IN2,最后是 IN3。這里有一個帶有時序圖的示例:

并行輸入 – 并行輸出 (PIPO) 移位寄存器

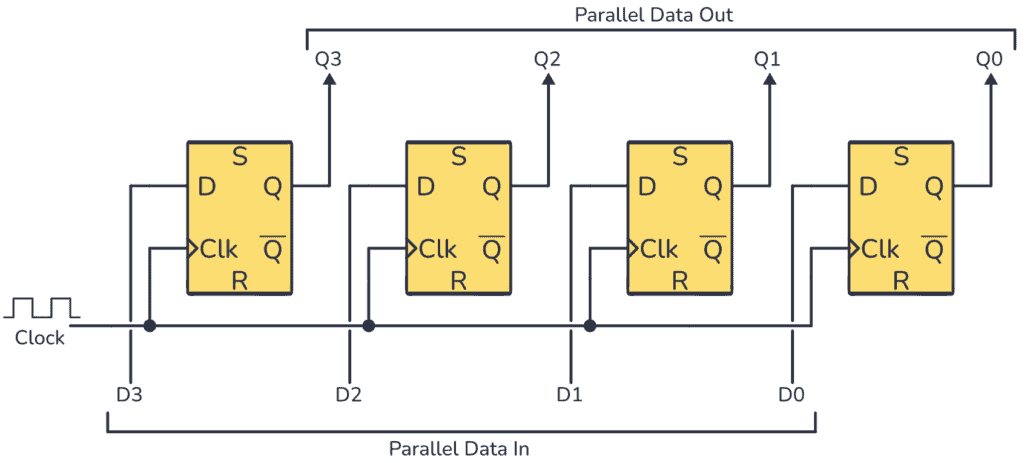

這種類型的移位寄存器充當多位臨時存儲設備。看看它的電路,試著猜測為什么。

您可能已經觀察到,在PIPO移位寄存器中,D觸發器沒有通過D輸入和Q輸出連接在一起。相反,它們只共享時鐘信號。

并行輸入對應于每個觸發器的每個D輸入(D0,D1,D2,D3)。由于每個觸發器在Clk輸入中具有相同的時鐘信號,因此每個觸發器將同時觸發。發生這種情況時,并行輸入中的所有位將同時移動到并行輸出(Q0、Q1、Q2、Q3)。換句話說,要傳輸整個數據集,您只需要一個觸發信號。

該電路不符合移位寄存器的條件,因為它實際上不會移位。但是,在一個輸出和下一個輸出之間有一些額外的邏輯門,您可以并行加載數據,移動數據,然后以并行格式獲取數據的移位版本。

-

寄存器

+關注

關注

31文章

5425瀏覽量

123617 -

移位寄存器

+關注

關注

3文章

287瀏覽量

22669

發布評論請先 登錄

集成移位寄存器

移位寄存器的工作原理是什么?

移位寄存器及其應用實驗

移位寄存器的特點_移位寄存器工作原理

移位寄存器有哪些不同類型?

移位寄存器有哪些不同類型?

評論