高速先生成員--姜杰

大家都在關(guān)注DDR5跑的有多快,高速先生卻在關(guān)心它為什么能夠跑的穩(wěn)……

內(nèi)存的穩(wěn)定性,離不開RAS功能。提起RAS,熟悉DDR的小伙伴們一定記得行地址選通信號(Row Address Strobe, RAS),不過這個信號跟本文沒啥關(guān)系,為了避免大家概念混淆,先說明一哈。

言歸正傳,今天要介紹的是另外一個RAS(Reliability,Availability and Serviceability),即可靠性、可用性和可維護性的簡稱。RAS功能一方面可以通過調(diào)整信號規(guī)避風(fēng)險,另一方面,在發(fā)生錯誤時及時發(fā)現(xiàn)并進行修正,以延長系統(tǒng)正常運行的時間,通俗點說,就是沒事不找事,有事不怕事,當(dāng)然了,這么通透的功能不是某一項技術(shù)就能搞掂的,RAS功能通常是一組技術(shù)的合稱,DDR5能穩(wěn)住,RAS功能功不可沒。閑言少敘,一起上車吧。

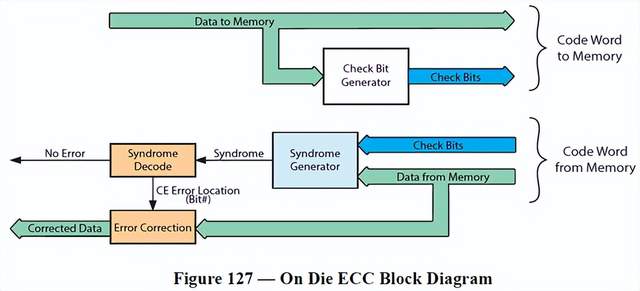

【提升1】片上ECC (On-Die Error Correction Code)

隨著DDR5信號速率的增加和芯片生產(chǎn)工藝難度的加大,DRAM內(nèi)存出現(xiàn)單位錯誤的風(fēng)險也隨之增加,為進一步改善內(nèi)存信道,糾正DRAM芯片中可能出現(xiàn)的位錯誤,DDR5引入了片上ECC技術(shù),將ECC集成到DDR5芯片內(nèi)部,提高可靠性并降低風(fēng)險,同時還能降低缺陷率。

看到這里,高速先生似乎已經(jīng)能猜到大家最關(guān)心的問題了:片上ECC的使用是否意味著可以不用單獨的ECC顆粒了?很遺憾,答案是否定的,因為On-Die ECC無法糾正芯片外或者模塊與內(nèi)存控制器之間的DDR通道中的錯誤,因此,之前常用的邊帶(Side-band)ECC顆粒在必要的情況下還是要保留的。

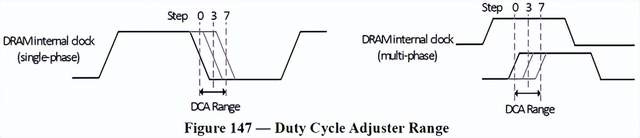

【提升2】占空比調(diào)節(jié)器 (DCA,Duty Cycle Adjuster)

占空比調(diào)節(jié)器(DCA)支持主控通過調(diào)節(jié)DDR5內(nèi)部占空比,在一定的范圍內(nèi)補償數(shù)據(jù)選通信號(DQS)和數(shù)據(jù)信號(DQ)的占空比失真,該功能通過調(diào)整DQ和DQS信號的占空比,鞏固了讀取數(shù)據(jù)的穩(wěn)定性。

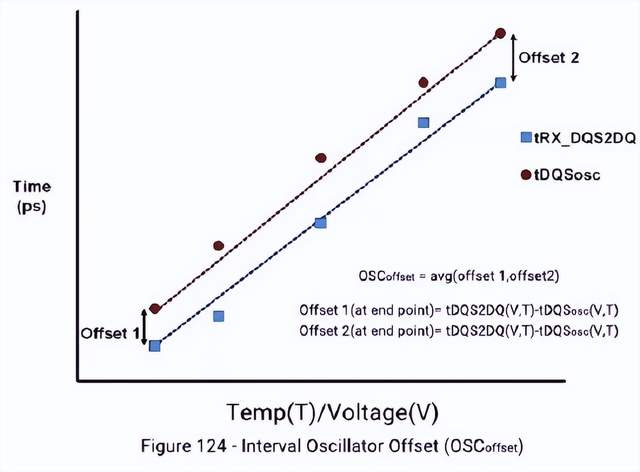

【提升3】DQS內(nèi)部延遲監(jiān)控(DQS Interval Oscillator)

隨著DDR DIE上的電壓和溫度變化,DQS時鐘樹延遲將發(fā)生偏移,可能需要重新訓(xùn)練(re-train)。DDR5包括一個內(nèi)部DQS時鐘樹振蕩器,用于測量由主控確定的給定時間間隔內(nèi)的延遲量。DQS振蕩器為主控提供是否需要重新訓(xùn)練,以及潛在誤差大小等重要信息。主控可以使用此功能定期重新訓(xùn)練通道,以補償DRAM中電壓和溫度變化引起的延遲。

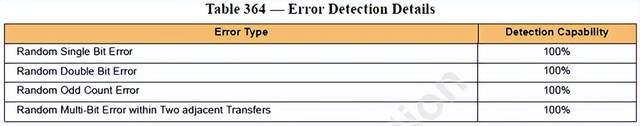

【提升4】數(shù)據(jù)讀寫的循環(huán)冗余校驗 (CRC, Cyclic Redundancy Check)

循環(huán)冗余校驗是數(shù)據(jù)通信領(lǐng)域中一種常見的查錯校驗技術(shù)。其基本原理是:將固定數(shù)量的校驗位附加在需要傳輸?shù)臄?shù)據(jù)后面,發(fā)送端對校驗位進行特定的運算并發(fā)送,接收端在接收數(shù)據(jù)后對校驗位進行運算以檢查是否出錯。CRC保證了數(shù)據(jù)傳輸?shù)恼_性。

DDR4僅支持數(shù)據(jù)寫操作的CRC,DDR5則將CRC功能擴展到數(shù)據(jù)的讀操作,進一步保證了數(shù)據(jù)傳輸?shù)目煽啃浴?/p>

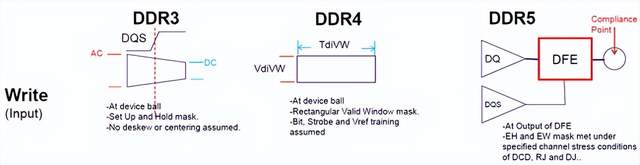

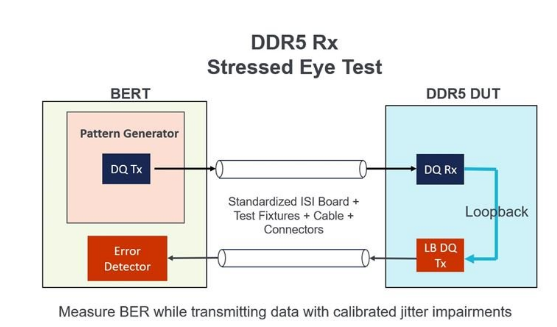

【提升5】數(shù)據(jù)的反饋判決均衡 (DFE)

對于數(shù)據(jù)信號,隨著速率的進一步提升,DDR5采用了之前在高速串行信號中才會使用的反饋判決均衡技術(shù)(DFE),以減少信號衰減和碼間干擾(ISI)的負面影響,增加了信號眼圖的優(yōu)化手段,為數(shù)據(jù)信號的高速傳輸提供了保障。

關(guān)于DDR5數(shù)據(jù)信號的DFE功能,高速先生之前有專門寫過一篇文章進行介紹,這里就不再贅述。

篇幅所限,本文對DDR5的RAS功能簡介就到這里,正是由于多種RAS新功能的加持,才一定程度上保證了DDR5提速后的穩(wěn)定性。

-

DDR

+關(guān)注

關(guān)注

11文章

732瀏覽量

66794 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3122瀏覽量

75243 -

DDR5

+關(guān)注

關(guān)注

1文章

446瀏覽量

24881

發(fā)布評論請先 登錄

DDR5內(nèi)存普及率不高,是PMIC的鍋?

DDR5內(nèi)存接口芯片組如何利用DDR5 for DIMM的優(yōu)勢?

新一代DDR5內(nèi)存模組密集發(fā)布,支持DDR5 CPU隨后就到!

Introspect DDR5/LPDDR5總線協(xié)議分析儀

DDR3/4都還沒玩夠,DDR5已經(jīng)來啦

DDR5這么快,為啥還能那么穩(wěn)?

DDR5內(nèi)存的價格為何那么貴

ddr5的主板可以用ddr4內(nèi)存嗎 幾代CPU才能上DDR5

ddr5為什么能跑得那么穩(wěn)呢

DDR5這么快,為啥還能那么穩(wěn)?

DDR5這么快,為啥還能那么穩(wěn)?

評論