高速數(shù)字電路模塊通常以 同步 (synchronous)電路的形式實現(xiàn),它們由一個或者多個時鐘驅(qū)動(觸發(fā))。對于 單一時鐘(域) 的同步電路而言,只要輸入和時鐘的關(guān)系滿足 建立(setup)時間 、保持(hold)時間的時序關(guān)系,電路的輸出(布爾值)就是可預(yù)測的,這是數(shù)字邏輯電路設(shè)計的基礎(chǔ)。如果 不能滿足建立保持時間 ,我們認為輸入是 異步 (asynchronous) 信號 。一個時鐘域的同步信號輸出到另一個時鐘域通常被認為是異步信號。

本文從同步電路的時序模型出發(fā),探討了兩種時鐘同步的總線電路方案:

- 共同時鐘 (common clock)總線

- 源同步 (source synchronous)總線

共同時鐘總線的收發(fā)端使用同一時鐘,結(jié)構(gòu)簡單,由于物理限制和PVT效應(yīng),局限于時鐘速率比較低的應(yīng)用;源同步總線增加 接口時鐘 ,并以 與數(shù)據(jù)相同的方式發(fā)送 ,大大提升了接口時鐘速率,由于引入了 不同的時鐘域 ,也增加了接口設(shè)計的復(fù)雜程度。

1. 時鐘同步電路的時序模型

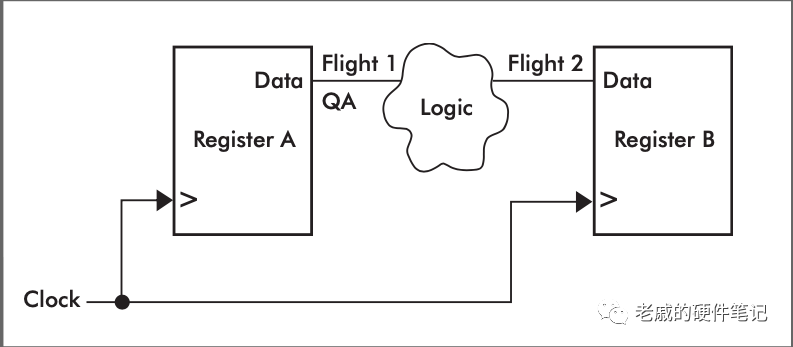

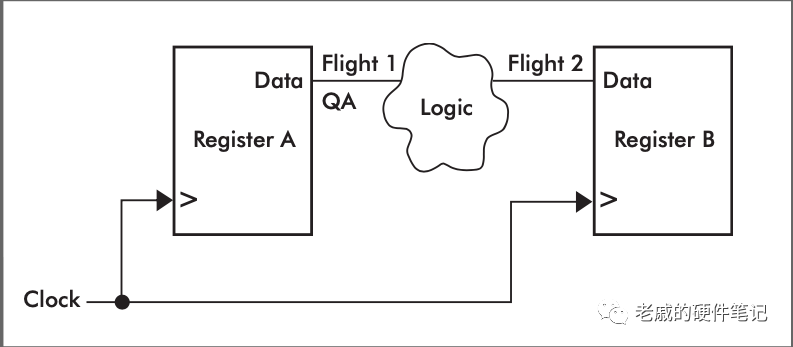

<圖1>

寄存器A在時鐘(launch clock)的上升沿打出數(shù)據(jù),經(jīng)過兩段飛行時間(傳輸延時)和組合邏輯電路延時之后,在下一個時鐘沿(capture clock)被寄存器B抓取,這里假設(shè)A、B的時鐘完全相同 - 頻率相同相位相同。在兩個時鐘上升沿之間,按照時間順序,發(fā)生了下列事件:

寄存器A打出輸出(QA)。QA在上升沿之后一段時間才能有效(valid),這個時間是tco(clock to output);

傳輸延時tflight1,組合邏輯電路引起的延時tlogic,傳輸延時tflight2;

寄存器B抓取輸入。輸入在時鐘上升沿之前必須提前穩(wěn)定(建立時間tsetup),在時鐘上升沿之后保持一段時間(保持時間thold)。假如不滿足建立、保持時間的要求,那么B的輸出可能會非0非1的亞穩(wěn)態(tài)(Metastability)。

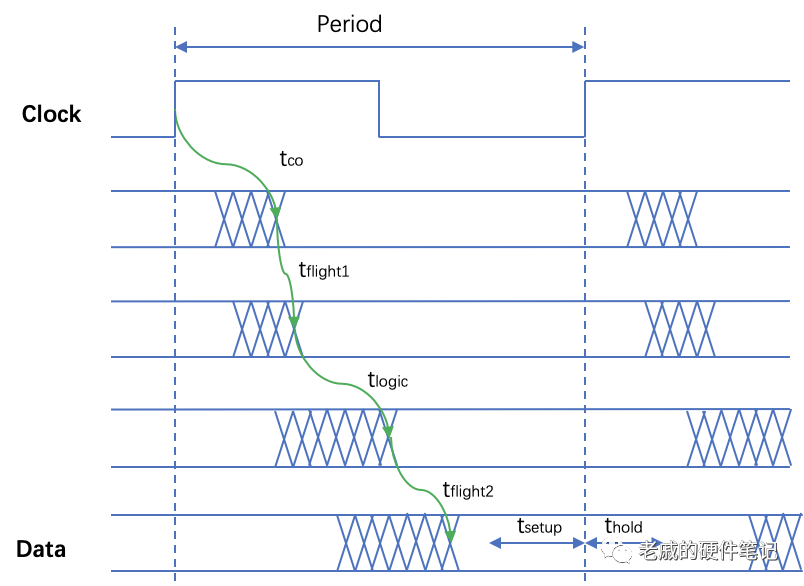

<圖2>

把這些事件銜接在一起,形成了時序預(yù)算(timing budget)分配圖。注意,‘X’表示不確定區(qū)間,通常是由PVT(制程電壓溫度)效應(yīng)引起的偏差。

tsetup_margin = Period - tco(max)- tflight1 - tlogic(max) - tflight2 - tsetup

thold_margin = tco(min) + tflight1 + tlogic(min) + tflight2 - thold

tsetup_margin和thold_margin為 時序裕量 (margin),它**>=0代表滿足建立保持時間**要求。

2. 共同時鐘(common clock)系統(tǒng)總線

共同時鐘系統(tǒng)其實可以借用<圖1>,只需要把寄存器換成芯片(系統(tǒng))。

共同時鐘系統(tǒng)只有一個時鐘(域),無論發(fā)送端還是接收端。

回到時序計算公式,要使tsetup_margin >=0,可以得到:

Period >= tco(max) + tflight1 + tlogic(max) + tflight2 + tsetup

右邊這些參數(shù)代表了真實的物理局限,它們決定了時鐘可以跑多快(時鐘周期最小是多少)。

tflight1、tflight2來自于PCB走線,連接器,芯片封裝等等。

tco、tsetup、tlogic代表芯片的 物理特性參數(shù) 。不同的芯片在不同的溫度/電壓下由于PVT效應(yīng)表現(xiàn)會有變化,形成了時序圖上的 不確定區(qū)間 。我們必須計算最惡劣(worst case)的情況,這會吃掉時序裕量。

而且,我們也做不到理想的單一同步時鐘。出于信號質(zhì)量的考量,時鐘信號通常是點對點(point to point)的連接。不同模塊的時鐘,通常是連接同一個時鐘buffer的不同扇出(fanout)。在工程實踐上,理想的同步很難做到,只能把相位偏差(skew)控制在一定范圍內(nèi)。

所有這些,都限制了時鐘速度或者數(shù)據(jù)吞吐量的提升,而優(yōu)化參數(shù)常常意味著成本的抬升。老戚看到的共同時鐘系統(tǒng)的時鐘沒有超過100MHz的。實現(xiàn)更高速總線的解決辦法是源同步時鐘方案。

3. 源同步(source synchronous)系統(tǒng)

源同步在芯片(系統(tǒng))接口上 同時輸出數(shù)據(jù)和(接口)時鐘 ,數(shù)據(jù)和時鐘采用完全相同的IO結(jié)構(gòu),從而最大程度的抵消tco,tflight等等。通常認為,同一個芯片上的PVT效應(yīng)也是一致的。

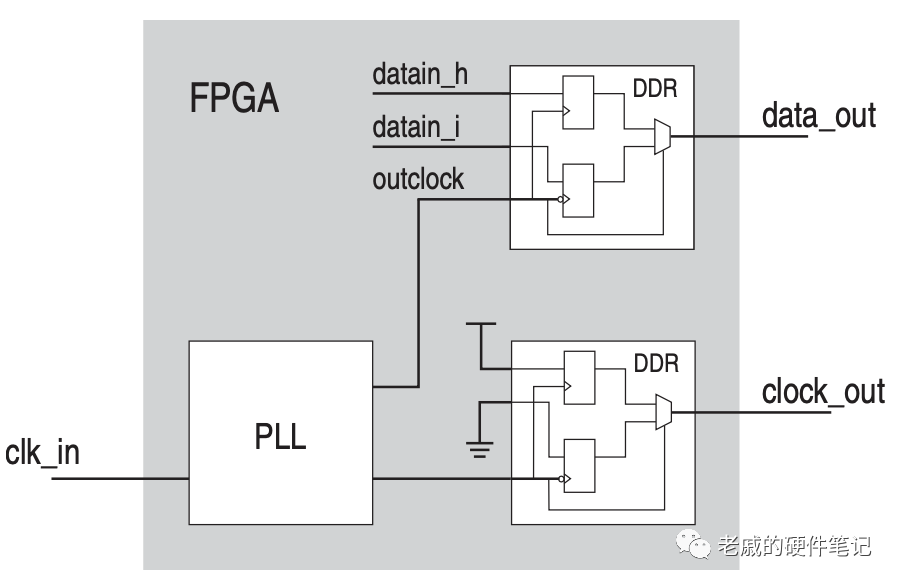

<圖3>

<圖3>是典型的中心對齊(center aligned)的源同步DDR輸出。內(nèi)部PLL的輸出兩路相位相差90度的時鐘,經(jīng)過同等的傳輸延時,到達接收端的時候,時鐘剛好處在數(shù)據(jù)的中心(假定接收端建立保持時間的要求也是對等的)。接收端使用接口時鐘clock_out抓取數(shù)據(jù)data_out,緊接著把數(shù)據(jù)同步到本地時鐘。 接口時鐘和本地時鐘并不一致 ,屬于 不同的時鐘域 。

現(xiàn)有的高速并行接口無一例外都是源同步,最典型的當(dāng)然是內(nèi)存接口。以DDR4為例,地址/命令/片選信號和主時鐘形成了一組源同步總線,內(nèi)存數(shù)據(jù)DQ每8位就會有一個DQS信號作為接口時鐘,形成源同步的數(shù)據(jù)時鐘總線。在接收端,數(shù)據(jù)會先被抓取到相應(yīng)DQS的時鐘域,然后同步到主時鐘。

源同步很好的解決了接口總線的速度問題,卻也引入了不同的時鐘域, 增加了收發(fā)接口設(shè)計的復(fù)雜度 。

- 跨時鐘域(clock domain crossing)

實現(xiàn)跨時鐘域的信號傳遞要回到時鐘域C0的輸出到時鐘域C1的輸入的建立保持時間的基本問題。

假如時鐘C0/C1 同源 (不同頻,例如分頻/倍頻關(guān)系)而且相位差固定的 可以直接用本地時鐘抓取 ;同頻(源)但是不知道相位關(guān)系不確定的可以以FIFO的方式解決;有頻差的也可以用 FIFO解決 ,但要防止溢出(overrun,underrun)。

還是以DDR4內(nèi)存接口為例,假設(shè)主時鐘是1600MHz,那么DQS則是倍頻 --- 3200MHz。由于時鐘(包括地址/命令/片選)信號的fly-by拓撲,時鐘到達不同內(nèi)存顆粒存在先后順序。對于寫操作(write),控制器通過write leveling偵測到未經(jīng)調(diào)整的DQS和主時鐘的相位關(guān)系,相應(yīng)的調(diào)整輸出DQS的相位,保證內(nèi)存顆粒接收的DQS和主時鐘保持 特定的相位關(guān)系 ,從而在顆粒內(nèi)部能夠以最簡單的方式(同時延時latency最小)完成跨時鐘域。對于讀操作,似乎有read leveling來實現(xiàn)相似的功能(這方面資料不詳)。有趣的是,在DDR4內(nèi)存接口,控制器(通常邏輯更為復(fù)雜)承擔(dān)了所有時序調(diào)整的責(zé)任,內(nèi)存(存儲廠商的邏輯設(shè)計能力要差一些)接口則以最簡化的方式工作。

在以太網(wǎng)領(lǐng)域,處理跨時鐘域更常用的方法是FIFO(First In First Out)。FIFO不僅能夠處理同頻時鐘的跨時鐘域數(shù)據(jù)轉(zhuǎn)換,也能處理不同頻率(有限頻差)的跨時鐘域處理,從而獲得了廣泛的應(yīng)用。PCIe協(xié)議和以太網(wǎng)協(xié)議都運用基于FIFO的 彈性緩沖 (elastic buffer)來處理系統(tǒng)時鐘的PPM偏差問題。

-

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124427 -

連接器

+關(guān)注

關(guān)注

99文章

15378瀏覽量

140435 -

同步電路

+關(guān)注

關(guān)注

1文章

60瀏覽量

13536 -

FIFO存儲

+關(guān)注

關(guān)注

0文章

103瀏覽量

6188 -

PCB走線

+關(guān)注

關(guān)注

3文章

135瀏覽量

14297

發(fā)布評論請先 登錄

兩種典型的電池供電電路的設(shè)計方案

SOPC設(shè)計中的兩種片上總線分析

基于FPGA的時鐘恢復(fù)以及系統(tǒng)同步方案設(shè)計

兩種不同結(jié)構(gòu)的永磁同步電機特點說明

基于FFT的兩種偽碼快速捕獲方案

兩種總線數(shù)據(jù)兩種傳遞形式:PIO、DMA介紹資料下載

探討兩種時鐘同步的總線電路方案

探討兩種時鐘同步的總線電路方案

評論