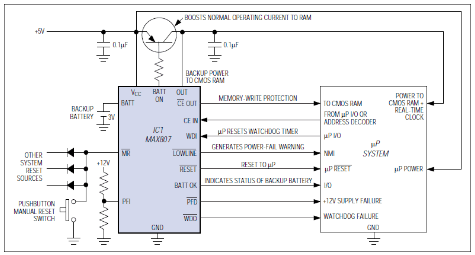

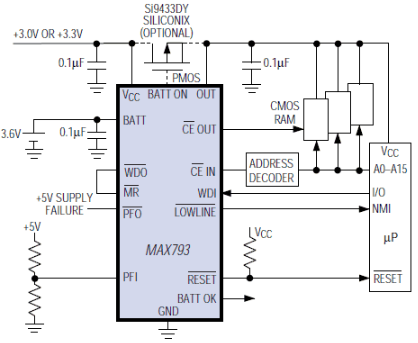

為確保正確運行,大多數(shù)基于微處理器的系統(tǒng)都需要在上電和關(guān)斷期間以及進(jìn)入或退出關(guān)斷或休眠模式時進(jìn)行監(jiān)控。監(jiān)控器可能僅提供上電復(fù)位,也可能提供附加功能,例如備用電池管理、存儲器寫入保護(hù)、低線預(yù)警或軟件看門狗(圖1)。

圖1.功能豐富的μP監(jiān)控器(IC1)借助μP本身,在這個典型的應(yīng)用電路中執(zhí)行各種功能。

通過選擇眾多可用的微處理器 (μP) 監(jiān)控器 IC(也稱為上電復(fù)位、電源良好電路、復(fù)位電路等)之一,可以同時或以各種組合方式獲得這些功能。以下討論可幫助您選擇最適合您應(yīng)用的方法,并為許多常見的μP監(jiān)督問題提供解決方案。

首先,確定Vcc將發(fā)出復(fù)位的閾值電壓。(RESET的置位在電源電壓超出容差時阻止μP操作。典型的上電復(fù)位電路由基準(zhǔn)電壓源、比較器和定時器組成。比較基準(zhǔn)電壓與上升的V電壓抄送(通過分壓器)使比較器能夠在 V 時進(jìn)行輸出轉(zhuǎn)換抄送超過閾值 (VRST) 由分隔線設(shè)置。此轉(zhuǎn)換會觸發(fā)定時器,定時器根據(jù)需要保持復(fù)位,以防止軟件執(zhí)行,直到系統(tǒng)振蕩器啟動并穩(wěn)定下來。

當(dāng) VCC 低于 VRST 時,只要 VCC 保持在 VRST 以下,管理引擎就會再次發(fā)出復(fù)位并保持重置。對于某些微控制器(μC),建議使用簡單的RC電路來定時此上電復(fù)位;其他器件在μC芯片上提供復(fù)位電路。然而,這些方法假設(shè)電源電壓行為是可預(yù)測的。它們不能防止由于掉電而可能發(fā)生的代碼執(zhí)行錯誤,或者更重要的是,在“掉電”期間,VCC可能會在較長時間內(nèi)略微脫離監(jiān)管。監(jiān)控IC對于這些關(guān)斷和掉電條件最有價值。

影響閾值的因素包括VCC容差、系統(tǒng)IC允許的最小和最大電源電壓,以及可能需要為這些變量的最壞情況組合指定設(shè)計。對于許多系統(tǒng),復(fù)位功能并非旨在涵蓋所有可能的條件,包括溫度范圍內(nèi)的最壞情況組合。例如,系統(tǒng)可能包括僅指定為4.75V(最小值)的IC,但取決于最小/最大跳閘門限為4.5V/4.75V的監(jiān)控器。在這種情況下,監(jiān)控器僅在VCC降至IC工作保證的最小電壓以下后斷位復(fù)位。

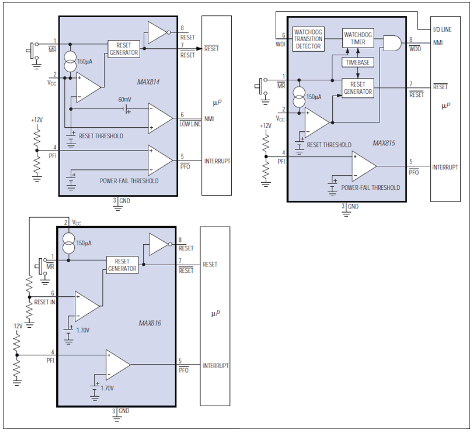

另一種方法是在4.75V和(可能)4.85V之間選擇一個復(fù)位門限。但是,這些值可能允許在需要之前進(jìn)行重置。通常,您必須決定是否可以容忍較低的閾值,以便在較低電壓下獲得工作時間;或者與更高閾值相關(guān)的額外費用和減少的運行時間是否是為了提高準(zhǔn)確性而進(jìn)行的公平交易。監(jiān)控器IC現(xiàn)在的復(fù)位閾值容差高達(dá)±1%(圖2)。

圖2.這三款I(lǐng)C提供不同的監(jiān)控功能組合,但每款I(lǐng)C都監(jiān)控V抄送準(zhǔn)確率為 ±1%。

監(jiān)控多個電源

許多應(yīng)用需要5V和3.3V電源,如果其中任何一個失去穩(wěn)壓,通常必須復(fù)位整個系統(tǒng)。您還需要適當(dāng)?shù)纳想姀?fù)位持續(xù)時間,以確保在上電期間正常運行。具有電源故障比較器和手動復(fù)位輸入(/MR)的監(jiān)控IC為這些問題提供了經(jīng)濟(jì)高效的解決方案。

如果選擇內(nèi)部門限設(shè)置為監(jiān)控 3.3V 的監(jiān)控 IC,則可以使用非專用電源故障比較器來監(jiān)控 5V 電源:只需將電源失效比較器輸出 (PFO) 路由回/MR 輸入(圖 3)。當(dāng)任一電源失去穩(wěn)壓時,這些連接使IC置位/復(fù)位。IC由3.3V供電,因此/RESET輸出在工作時擺幅為3.3V。該電平滿足大多數(shù)5V處理器的VIH要求,因此/RESET輸出通常可以驅(qū)動3V和5V處理器。如有必要,您可以通過二極管OR連接將其他系統(tǒng)復(fù)位信號路由到/MR輸入。(即使沒有這些連接,也需要從/MR輸入到PFO輸出的二極管。

圖3.如圖所示配置,該監(jiān)控IC可監(jiān)視3.3V和5V電源。

停機例程預(yù)警

關(guān)鍵系統(tǒng)通常需要在電源電壓(V抄送) 開始下降。該警告允許μP有時間存儲重要數(shù)據(jù),并在V下降之前執(zhí)行“內(nèi)務(wù)”工作抄送導(dǎo)致管理引擎發(fā)出硬重置。如果原始直流輸入電壓可訪問,則可以使用欠壓或電源故障比較器對其進(jìn)行監(jiān)視,該比較器反過來置位處理器中斷以指示未穩(wěn)壓電源何時崩潰。

如果您無法訪問此原始輸入電壓,則必須在監(jiān)視同一穩(wěn)壓電源的同時生成預(yù)警和復(fù)位信號。您可以對低線信號使用單個閾值檢波器,對復(fù)位信號使用延遲定時器,也可以使用兩個不同的比較器,一個用于低線一個用于 tRST.無論哪種方式,您都必須確保 V抄送保持足夠長的有效期,以完成低線信號中斷后的關(guān)斷例程。

完成關(guān)機/備份例程所需的時間因應(yīng)用而異,V 的下降率也是如此抄送.因此,您必須根據(jù)應(yīng)用將延遲從低線調(diào)整為復(fù)位。雙閾值方法比延時復(fù)位方法更靈活。通過將低線閾值調(diào)整到復(fù)位閾值以上數(shù)十毫伏并調(diào)整V抄送下降速率 為了符合關(guān)斷例程的時間要求,可以使一個IC服務(wù)于許多不同的應(yīng)用。

在大多數(shù)電池供電的便攜式系統(tǒng)中,電池中的備用能量提供了充足的時間,以便在低線警告和復(fù)位之間的時間間隔內(nèi)完成關(guān)斷程序。如果 V抄送下降時間很快,如正常工作時打開高邊開關(guān)時,在開關(guān)負(fù)載側(cè)增加電容以減緩V的下降抄送并提供執(zhí)行關(guān)機例程的時間。例如,在MAX814監(jiān)控器中,電源故障比較器的延遲(小于50μs)可能會影響也可能不會影響您的應(yīng)用。

首先,計算關(guān)斷例程所需的最壞情況時間。使用此值,最差情況下的負(fù)載電流和最小低線至復(fù)位閾值差(VLR(分鐘)),計算復(fù)位發(fā)生前完成關(guān)斷例程所需的電容:

我在哪里負(fù)荷是從電容器中排出的電流,VLR(分鐘)是低線閾值和復(fù)位閾值之間的最小差值,并且SHDN是有序關(guān)斷所需的時間,包括復(fù)位比較器的傳播延遲。

將低線閾值置于復(fù)位閾值以上可能會因噪聲而產(chǎn)生錯誤的低線觸發(fā)。為了克服這個問題,通過適當(dāng)?shù)呐月窞V除噪聲,并在關(guān)斷程序完成后使用軟件監(jiān)控低線中斷。當(dāng)處理器從低壓線比較器接收到中斷時,它會完成備份/關(guān)斷例程,然后返回監(jiān)視中斷。如果線路或負(fù)載瞬態(tài)導(dǎo)致低壓線路相對較快地返回高電平,則軟件會通過重新加載存儲的參數(shù)來啟動“熱”啟動。如果發(fā)生電源故障,低線信號后跟復(fù)位信號,并開始正常的備用電池工作模式。

DC-DC 升壓電路延長關(guān)斷時間

如果備份/關(guān)斷例程需要的時間超過存儲電容器的合理時間,則可以使用 DC-DC 轉(zhuǎn)換器來維持 V抄送當(dāng)關(guān)機例程正在進(jìn)行時。備份完成后,μP 可以關(guān)斷 DC-DC 轉(zhuǎn)換器。

例如,在圖4中,IC2是一個升壓轉(zhuǎn)換器,當(dāng)5V主電源發(fā)生故障時,它為系統(tǒng)和μP監(jiān)控器(IC3)提供5V電壓。在這種電源故障開始時,當(dāng)主電源降至4.65V以下時,IC1關(guān)斷Q1,使IC2退出關(guān)斷狀態(tài),并中斷μP。未達(dá)到復(fù)位閾值,因此不會發(fā)出對μP的復(fù)位。當(dāng)μP完成其關(guān)斷程序時,只需將IC2再次拉入關(guān)斷狀態(tài),系統(tǒng)進(jìn)入正常的電池備份模式。

圖4.VCC損耗的威脅會導(dǎo)致升壓轉(zhuǎn)換器(IC3)導(dǎo)通并將VCC恢復(fù)到其標(biāo)稱電平。

升壓轉(zhuǎn)換器可提供高達(dá) 100mA 的電流,同時由已耗盡至 2.5V 的鋰電池供電。如果需要,您可以為 RAM 備份和升壓轉(zhuǎn)換器提供單獨的電池。

防止錯誤重置

監(jiān)控電路不得響應(yīng)系統(tǒng)噪聲或VCC負(fù)載瞬變而發(fā)出復(fù)位。數(shù)字電源線上大約50mV的噪聲很常見。模塊、外設(shè)和其他子系統(tǒng)打開或關(guān)閉時發(fā)生的負(fù)載瞬變,如果復(fù)位比較器的傳播延遲太短,可能會導(dǎo)致嚴(yán)重問題。

通過選擇復(fù)位比較器傳播延遲為10μs至30μs的監(jiān)控電路,可以避免錯誤復(fù)位。較短的傳播延遲(幾百納秒)對VCC瞬變反應(yīng)迅速,因此可能會產(chǎn)生錯誤的復(fù)位。另一方面,在處理器復(fù)位之前,長時間延遲會使VCC遠(yuǎn)遠(yuǎn)超出系統(tǒng)IC的工作范圍。大多數(shù) 5V 應(yīng)用都包含足夠的電容來降低 VCC 下降速率,以便在 VCC 降至 IC 電氣特性中規(guī)定的最低電平之前進(jìn)行復(fù)位。

備用電池

對于需要非易失性存儲器的關(guān)鍵系統(tǒng),設(shè)計人員可以選擇可擦除/可編程存儲器或帶備用電池的CMOS RAM。EEPROM和閃存的額定值不僅包括存儲器容量,還取決于它們可以經(jīng)歷的寫入周期數(shù)。最常見的非易失性存儲器包括一個開關(guān),用于將CMOS RAM連接到鋰備用電池或VCC,以較高者為準(zhǔn)。

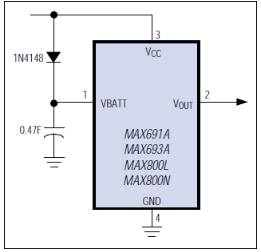

大電容器(約0.5F)提供了一種提供短期內(nèi)存?zhèn)浞莸某S梅椒ā7Q為超級電容?或最大電容?,這些電容器從 V 充電抄送正常工作期間通過二極管(圖5)。充電電流受電容器內(nèi)部串聯(lián)電阻的限制,該電阻相對較高。內(nèi)存從 V 切換抄送到電容器時 V抄送折疊到IC的復(fù)位閾值以下。可用的備份時間取決于進(jìn)入RAM和監(jiān)控器IC的靜態(tài)電流水平,以及電容器本身的自放電泄漏。對于許多在備份模式下僅消耗數(shù)十微安電流的系統(tǒng),這種備份電容器可以保持?jǐn)?shù)小時的內(nèi)存內(nèi)容。例如,Maxim監(jiān)控器的1μA靜態(tài)電流通常微不足道。

圖5.一個非常大的電容器(在本例中為0.47F)可以用作低靜態(tài)電流系統(tǒng)中的備用電池。

3V 應(yīng)用中的備用電池切換帶來了挑戰(zhàn):如何確定何時在 3.3V VCC 和 3.6V 鋰備份電池之間切換?一種方法是定義一個高于CMOS RAM最小待機電壓的接地參考電壓。因此,VCC 為 RAM 供電,直到它降至略高于 2V 的電壓;然后將RAM切換到備用電池(圖6)。

圖6.當(dāng) Vcc吸收至略高于 2V 的電壓,該系統(tǒng)將 CMOS RAM 從 V 切換抄送到備用電池。

特殊情況

為了節(jié)省電池能量,電池供電便攜式設(shè)備的設(shè)計人員通常使用80CL51 μC的省電模式。如果CMOS存儲器內(nèi)容的保存至關(guān)重要,IC1的/低線輸出(圖6)會產(chǎn)生中斷。當(dāng)主電池電壓低到足以導(dǎo)致V時,此中斷信號可以觸發(fā)關(guān)斷程序抄送失落于容忍度。RAM 內(nèi)容物通過電池中剩余的任何能量保持活力。

當(dāng)μC處于省電模式且監(jiān)控器的RESET直接連接到μC的RST端子時,VCC降至復(fù)位門限以下將導(dǎo)致RESET變?yōu)楦唠娖健_@反過來又喚醒μC并將其置于運行模式,將其靜態(tài)電流從大約100μA增加到6mA。電池電壓繼續(xù)下降,VCC保持在閾值以下,因此6mA將耗盡電池電量,大大縮短可用的備份時間。

只需將/低線和復(fù)位與AND門相結(jié)合(圖7),即可確保IC3的RST僅在復(fù)位超時周期內(nèi)(而不是在VCC下降時)被驅(qū)動為高電平。換句話說,在VCC恢復(fù)(通過為電池充電或安裝新電池)并重新越過低線閾值后,RST會變高。因此,AND門允許休眠控制器保持休眠狀態(tài)。

圖7.AND 柵極通過防止微控制器操作中不必要的轉(zhuǎn)換(從睡眠模式到更高電流的空閑模式)來節(jié)省電池能量。

當(dāng)VCC處于正常工作范圍內(nèi)時,RESET為低電平,/低電平有效為高電平。當(dāng)VCC降至低線門限以下(通常比復(fù)位門限高45mV)時,/LOWLINE變?yōu)榈碗娖剑?0CL51發(fā)出關(guān)斷程序信號。當(dāng)VCC遇到復(fù)位門限時,RESET置位,但/低電平有效迫使AND柵極輸出保持低電平。

上電時,/LOWLINE保持低電平,因此RST保持低電平,直到VCC超過低電平門限。然后,RESET在重置超時周期內(nèi)傳播到RST終端。因此,80CL51 僅在 VCC 有效時退出其睡眠模式。

在此應(yīng)用中,還希望能夠檢測電池在睡眠期間的任何時間是否已放電到安全RAM備份電壓以下。使用此信息,系統(tǒng)決定是根據(jù) RAM 的內(nèi)容執(zhí)行“熱啟動”,還是從頭開始執(zhí)行“冷啟動”,因為低電池電壓可能已損壞 RAM 數(shù)據(jù)。IC1的BATT端子(引腳16)告訴μC哪種導(dǎo)體合適。

IC1有一個低電池電量比較器,通常指示連接到其BATT端子的備用電池的狀態(tài)。此比較器輸出(BATT OK)未鎖存。圖 7 中的應(yīng)用沒有備用電池,因此您可以使用 BATT 鎖存 BATT OK 的狀態(tài)。 只需將 BATT 連接到 80CL51 上的可用 I/O 引腳,并通過 10kΩ 電阻連接到 BATT OK 端子。

為了設(shè)置為正常工作,μC將I/O線路脈沖至高電平約30μs,然后將線路配置為高阻抗輸入。IC1中的比較器將BATT OK驅(qū)動為高電平,從而將BATT拉高并在該條件下鎖定。比較器由VCC供電,因此其在高電平狀態(tài)下的輸出接近VCC。如果VCC在休眠期間的任何時候低至2.25V,則比較器輸出捕捉到低電平并將BATT拉低,從而將其鎖存到低電平。VCC 恢復(fù)后(通過為主電池充電或更換主電池),μC 在繼續(xù)之前輪詢 BATT:高表示熱啟動,低表示冷啟動。

摩托羅拉 68HC11 等 μC 具有雙向復(fù)位引腳,可能會與監(jiān)控 IC 的/復(fù)位有效抗?fàn)帯@纾绻O(jiān)控器復(fù)位為高電平,而μC試圖將其拉低,則結(jié)果可能是不確定的邏輯電平。圖8的連接允許監(jiān)控器和μC對系統(tǒng)進(jìn)行有效的復(fù)位,并確保復(fù)位脈沖有足夠的持續(xù)時間(μC復(fù)位對于系統(tǒng)中的某些器件來說可能太短)。

圖8.這些連接允許對緩沖復(fù)位線路進(jìn)行雙重控制,并延長μP發(fā)出的復(fù)位持續(xù)時間。

該電容支持從監(jiān)控器和μC復(fù)位,以將/MR拉低電平。/MR變?yōu)榈碗娖皆诒O(jiān)控器內(nèi)啟動200ms超時,在其/RESET端子(引腳200)上產(chǎn)生2ms最小脈沖,該脈沖覆蓋μC/RESET,并通過緩沖器驅(qū)動系統(tǒng)復(fù)位線路。當(dāng)電容充電時,/MR返回高電平。當(dāng)μC/RESET在超時延遲后解除置位時,電容通過/MR上拉電阻和一個內(nèi)部ESD保護(hù)二極管放電。

審核編輯:郭婷

-

電池管理

+關(guān)注

關(guān)注

27文章

566瀏覽量

43665 -

存儲器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166416 -

微處理器

+關(guān)注

關(guān)注

11文章

2371瀏覽量

83854

發(fā)布評論請先 登錄

是否存在真正的無毛刺電壓監(jiān)控器IC?

無線監(jiān)控器

無線監(jiān)控器

【FireBLE申請】學(xué)生寫字坐姿監(jiān)控器

可用于電池充電和監(jiān)控 PC 的監(jiān)控器PMP5214技術(shù)參考資料及物料清單下載

電源IC 電流和電力監(jiān)控器、調(diào)節(jié)器

如何選擇合適的電壓檢測器、監(jiān)控器和復(fù)位IC?

電壓檢測器和監(jiān)控器和復(fù)位IC怎么選擇

微控制器監(jiān)控器集成電路中的故障保護(hù)分析

帶有圖表和電池監(jiān)控器的溫度和濕度監(jiān)控器

監(jiān)控器IC監(jiān)控電池供電設(shè)備

如何提高電壓監(jiān)控器IC的性能

是否存在真正的無毛刺電壓監(jiān)控器IC?

TI電池監(jiān)控器IC的高級電量監(jiān)測器固件流程圖

TI電池監(jiān)控器IC的HDQ通信基礎(chǔ)知識

監(jiān)控器IC監(jiān)控電池供電設(shè)備

監(jiān)控器IC監(jiān)控電池供電設(shè)備

評論