LPDDR是什么?

LPDDR(Low Power Double Data Rate SDRAM)低功耗雙倍速率動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器,是DDR SDRAM的一種,是JEDEC固態(tài)技術(shù)協(xié)會(huì)(JEDEC Solid State Technology Association)面向低功耗內(nèi)存而制定的通信標(biāo)準(zhǔn),以低功耗著稱,主要針對(duì)于移動(dòng)端電子產(chǎn)品。相比于DDR來說,LPDDR最大的特點(diǎn)就是功耗更低。

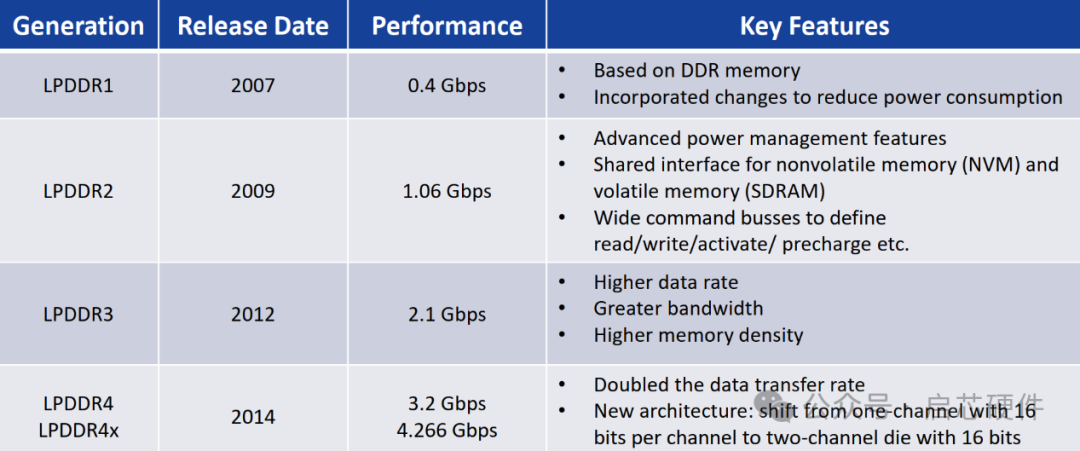

LPDDR也分為MDDR、LPDDR2、LPDDR3、LPDDR4、LPDDR4X、LPDDR5和LPDDR5X,和DDR一樣,數(shù)據(jù)處理速度和節(jié)能性隨著代數(shù)的增加而提高。

LPDDR2

第二代低功耗內(nèi)存技術(shù)LPDDR2的標(biāo)準(zhǔn)規(guī)范于2010年12月由JEDEC固態(tài)技術(shù)協(xié)會(huì)正式發(fā)布。LPDDR2的標(biāo)準(zhǔn)規(guī)范在移動(dòng)產(chǎn)品中實(shí)現(xiàn)更高的內(nèi)存性能、更低的功耗和SDRAMNVM接口兼容性。接口電壓1.2V,工作頻率范圍從100MHz到533MHz。

LPDDR3

第三代低功耗內(nèi)存技術(shù)LPDDR3的標(biāo)準(zhǔn)規(guī)范于2012年5月由JEDEC固態(tài)技術(shù)協(xié)會(huì)正式發(fā)布。

LPDDR3的標(biāo)準(zhǔn)規(guī)范可提供更高的數(shù)據(jù)速率、改進(jìn)的帶寬和電源效率以及更高的內(nèi)存密度。LPDDR3支持PoP堆疊封裝和獨(dú)立封裝,以滿足不同類型移動(dòng)設(shè)備的需要。

LPDDR3重點(diǎn)加入了新技術(shù),增加新功能實(shí)現(xiàn)了1600Mbps的數(shù)據(jù)速率,包括Write-Levelingand CATraining,On Die Termination (ODT) 和Low I/O capacitance。

Write-Leveling and CA Training(寫入均衡與指令地址調(diào)馴):可讓內(nèi)存控制器補(bǔ)償信號(hào)偏差,確保內(nèi)存運(yùn)行于業(yè)內(nèi)最快輸入總線速度的同時(shí),維持數(shù)據(jù)輸入設(shè)定、指令與地址輸入時(shí)序均滿足需求。

On Die Termination(片內(nèi)終結(jié)器/ODT):可選技術(shù),為L(zhǎng)PDDR3數(shù)據(jù)平面增加一個(gè)輕量級(jí)終結(jié)器,改進(jìn)高速信號(hào)傳輸,并盡可能降低對(duì)功耗、系統(tǒng)操作和針腳計(jì)數(shù)的影響。

LPDDR4

由于輸入/輸出接口數(shù)據(jù)傳輸速度最高可達(dá)3200Mbps,是通常使用的DDR3DRAM的兩倍,8GbLPDDR4內(nèi)存可以支持超高清影像的拍攝和播放,并能持續(xù)拍攝2000萬像素的高清照片。

與LPDDR3內(nèi)存芯片相比,LPDDR4的運(yùn)行電壓降為1.1伏,堪稱適用于大屏幕智能手機(jī)和平板電腦、高性能網(wǎng)絡(luò)系統(tǒng)的最低功耗存儲(chǔ)解決方案。以2GB內(nèi)存封裝為例,比起基于4Gb LPDDR3芯片的2GB內(nèi)存封裝,基于8Gb LPDDR4芯片的2GB內(nèi)存封裝因運(yùn)行電壓的降低和處理速度的提升,最大可節(jié)省40%的耗電量。若輸入/輸出信號(hào)傳輸采用低電壓擺幅終端邏輯(LVSTL, Low Voltage Swing Terminated Logic),不僅進(jìn)一步降低了LPDDR4芯片的耗電量,并使芯片能在低電壓下進(jìn)行高頻率運(yùn)轉(zhuǎn),實(shí)現(xiàn)了電源使用效率的最優(yōu)化。

LPDDR4X

LPDDR4X并非是LPDDR4的下一代版本內(nèi)存,可以看作是LPDDR4的省電優(yōu)化版本。相比于LPDDR4,LPDDR4X優(yōu)化了內(nèi)存的功耗,將 I/O 電壓降低了 50% (1.12 V至 0.61v),提高了內(nèi)存速度。在大容量加持下,存儲(chǔ)速度上更具有優(yōu)勢(shì),在運(yùn)行超大游戲,或是錄制4K視頻的時(shí)候作用非常明顯,功耗更低,運(yùn)行更快也更省電。

LPDDR5

2019年2月20日,JEDEC(固態(tài)存儲(chǔ)協(xié)會(huì))正式發(fā)布了JESD209-5,即Low Power Double Data Rate 5 (LPDDR5)全新低功耗內(nèi)存標(biāo)準(zhǔn)。

相較于2014年發(fā)布的第一代LPDDR4標(biāo)準(zhǔn),LPDDR5的I/O速度從3200Mbps翻番提升到6400Mbps,與LPDDR4X的4266Mbps相比也快了近30%。

如果匹配高端智能機(jī)常見的64bit bus,每秒可以傳送51.2GB數(shù)據(jù);要是PC的128bit BUS,每秒破100GB無壓力。

固態(tài)協(xié)會(huì)認(rèn)為,LPDDR5有望對(duì)下一代便攜電子設(shè)備(手機(jī)、平板)的性能產(chǎn)生巨大提升,為了實(shí)現(xiàn)這一改進(jìn),標(biāo)準(zhǔn)對(duì)LPDDR5體系結(jié)構(gòu)進(jìn)行了重新設(shè)計(jì),轉(zhuǎn)向最高16 Banks可編程和多時(shí)鐘體系結(jié)構(gòu)。

同時(shí),還引入了數(shù)據(jù)復(fù)制(Data-Copy)和寫X(Write-X)兩個(gè)減少數(shù)據(jù)傳輸操作的命令來降低整體系統(tǒng)功耗,前者可以將單個(gè)陣腳的數(shù)據(jù)直接復(fù)制到其它針腳,后者則減少了SoC和RAM傳遞數(shù)據(jù)時(shí)的耗電。

另外,LPDDR5還引入了鏈路ECC糾錯(cuò),信號(hào)電壓250mV,LPDDR5的電壓和LPDDR4X一樣是1.1V,不過閑置狀態(tài)下電流將降低40%,可大幅降低功耗。

LPDDR主要應(yīng)用于智能手機(jī)、平板電腦、超輕薄型電腦、智能穿戴等,隨著LPDDR技術(shù)升級(jí)迭代和人工智能、物聯(lián)網(wǎng)等技術(shù)的發(fā)展,LPDDR也將應(yīng)用于更多新的領(lǐng)域,如智能后視鏡、VR、商顯、POS機(jī)、智能家居等。

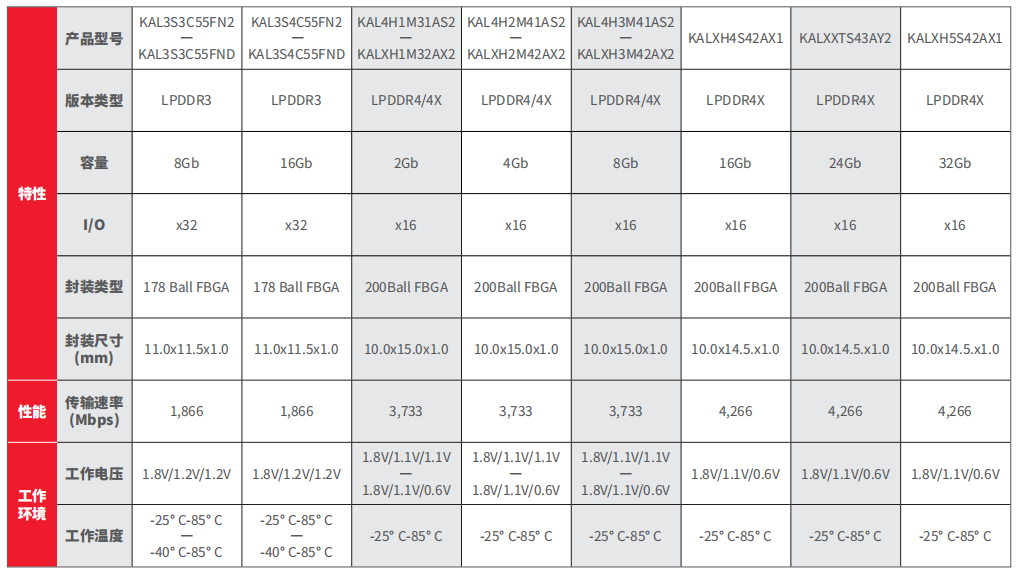

KOWIN LPDDR移動(dòng)終端隨芯小精靈產(chǎn)品參數(shù)

往期存儲(chǔ)知識(shí)回顧:

芯科普 | 一文了解存儲(chǔ)主流配置nMCP

芯科普 | 一文了解存儲(chǔ)主流配置ePOP

芯科普 | 一文了解存儲(chǔ)主流配置eMCP

存儲(chǔ)主流配置之DRAM篇

存儲(chǔ)主流配置之eMMC篇

原文標(biāo)題:芯科普 | 一文讀懂存儲(chǔ)主流配置LPDDR

文章出處:【微信公眾號(hào):KOWIN康盈半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

存儲(chǔ)

+關(guān)注

關(guān)注

13文章

4499瀏覽量

87045

原文標(biāo)題:芯科普 | 一文讀懂存儲(chǔ)主流配置LPDDR

文章出處:【微信號(hào):康盈半導(dǎo)體科技,微信公眾號(hào):KOWIN康盈半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

燦芯半導(dǎo)體推出DDR3/4和LPDDR3/4 Combo IP

一文了解LPDDR5X的核心需求和設(shè)計(jì)

一文讀懂:LED 驅(qū)動(dòng)電路二極管挑選要點(diǎn)

一文讀懂什么是「雷電4」

一文解析DDR和LPDDR的演進(jìn)與應(yīng)用

佰維存儲(chǔ)發(fā)布新一代LPDDR5X內(nèi)存

科技少年夢(mèng) 科普粵海行|芯海科技科普基地啟迪智慧未來

新品迅為RK3588-LPDDR5核心板_LPDDR4x與LPDDR5的區(qū)別

一文讀懂常見存儲(chǔ)器類型

云存儲(chǔ)服務(wù)器怎么配置

科普EEPROM 科普 EVASH Ultra EEPROM?科普存儲(chǔ)芯片

【古瑞瓦特光伏逆變器品牌】一文讀懂PCS儲(chǔ)能變流器

芯科普 | 一文讀懂存儲(chǔ)主流配置LPDDR

芯科普 | 一文讀懂存儲(chǔ)主流配置LPDDR

評(píng)論