前言

首先我們必須明確原理圖評審的目的:提前發(fā)現(xiàn)問題,改進(jìn)產(chǎn)品設(shè)計。

因此評審之前我們要結(jié)合產(chǎn)品設(shè)計經(jīng)驗將可能出現(xiàn)的問題點羅列出來,做到針對性的審查。過程中實事求是,評審人員多角度去參評設(shè)計。原理圖評審主要涉及到硬件工程師(兼采購工程師)、嵌入式軟件工程師。

一、圖面檢查

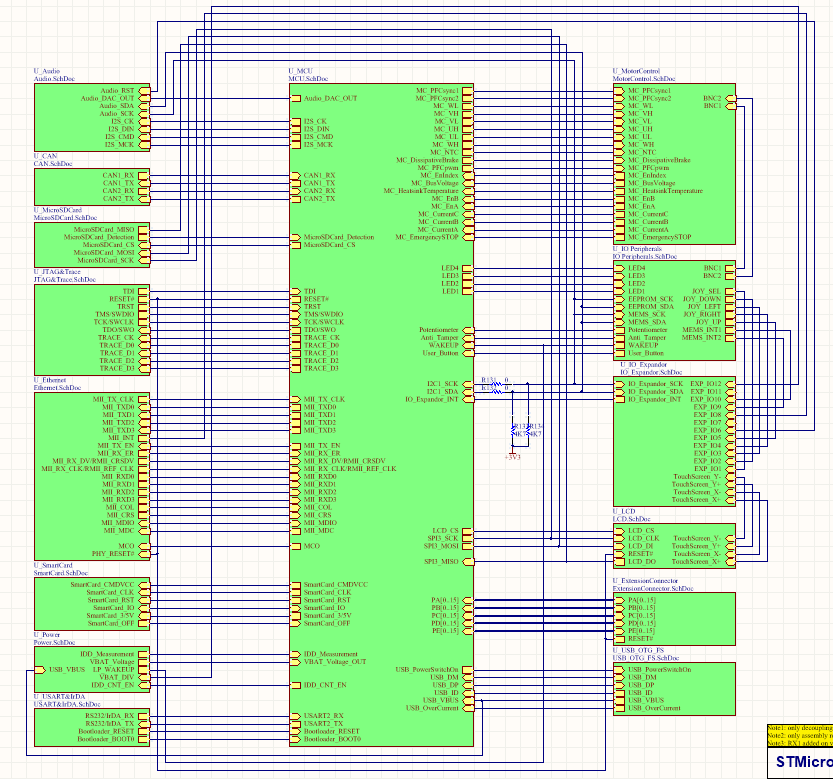

● 原理圖建議采用模塊化設(shè)計,首頁有總圖,描述各個模塊之間的關(guān)系,邏輯清晰;

●各個模塊標(biāo)注相關(guān)電源功耗計算,標(biāo)注關(guān)鍵元器參數(shù),電源部分注明輸入輸出,EMC測試標(biāo)準(zhǔn);

●模塊之間邏輯清晰,信號流向順暢,網(wǎng)絡(luò)標(biāo)識易懂。

二、元器件檢查

●原理圖中各個元器件選型應(yīng)滿足通用降額標(biāo)準(zhǔn);

●原理圖中元器件規(guī)格型號標(biāo)注清楚,封裝信息填寫清晰(eg:AD軟件可以填寫在Parameters中);

●元器件優(yōu)先選用相應(yīng)公司常備物料,避免增加公司物料采購壓力;

●在滿足產(chǎn)品開發(fā)需求的前提下,關(guān)鍵元器件首推國產(chǎn)品牌,如非要采用國外品牌,要考慮元器件的供貨風(fēng)險;

三、規(guī)則檢查

根據(jù)繪圖軟件統(tǒng)一設(shè)置查錯規(guī)則,這一步尤為重要。

四、電源檢查

●與結(jié)構(gòu)確認(rèn)產(chǎn)品安裝方式,確認(rèn)產(chǎn)品是否需要接大地;

●電源接口加防護(hù),依照產(chǎn)品應(yīng)測試標(biāo)準(zhǔn)針對性設(shè)計,避免照搬照用,不走心設(shè)計開發(fā);

●電源設(shè)計基本的防反接、過壓過載、短路等防護(hù),插件接口考慮防呆設(shè)計;

●數(shù)字電路與模擬/敏感電路模塊電源之間隔離分開,獨立接地處理;

●電源芯片輸入端放置去耦電容,重負(fù)載模塊的供電附近放置續(xù)流大電容;

●評估各個模塊之間電流,確保供電模塊1.5倍于負(fù)載最大值。

五、MCU及外設(shè)IC部分

● MCU時鐘電路確保安全可靠,必要時做包地處理;

● MCU燒錄口采用統(tǒng)一接口,避免后期因燒錄口線序不對造成的額外工作;

●單片機復(fù)位電路阻容選擇,查看單片機復(fù)位時間要求,選擇合適的容值;

● MCU及外設(shè)IC未使用引腳的處理問題,接地、拉高or懸空?查閱參考手冊或詢問芯片廠家;

● MCU與外設(shè)之間涉及到通訊問題時,要注意通訊電平之間匹配的問題,并評估常用的電平轉(zhuǎn)換方式。

六、PCBLayout

● Layout結(jié)束之后,可將布局好的Layout導(dǎo)出3D格式文件發(fā)給結(jié)構(gòu)工程師評估是否存在干涉問題;

●板子布局要考慮EMC設(shè)計、產(chǎn)品可靠性設(shè)計中重要的EMC問題一半是原理圖設(shè)計出來,一半是Layout與結(jié)構(gòu)設(shè)計出來的,要注意插件位置、線束走線與結(jié)構(gòu)出線口之間的位置設(shè)計,都會影響共模干擾電流的走向,進(jìn)而決定產(chǎn)品EMC設(shè)計的成敗;

● PCB也需要展開針對性的評審,涉及人員主要有硬件工程師、PCB Layout工程師、結(jié)構(gòu)工程師、電子工藝工程師;

七、PCB評審工具

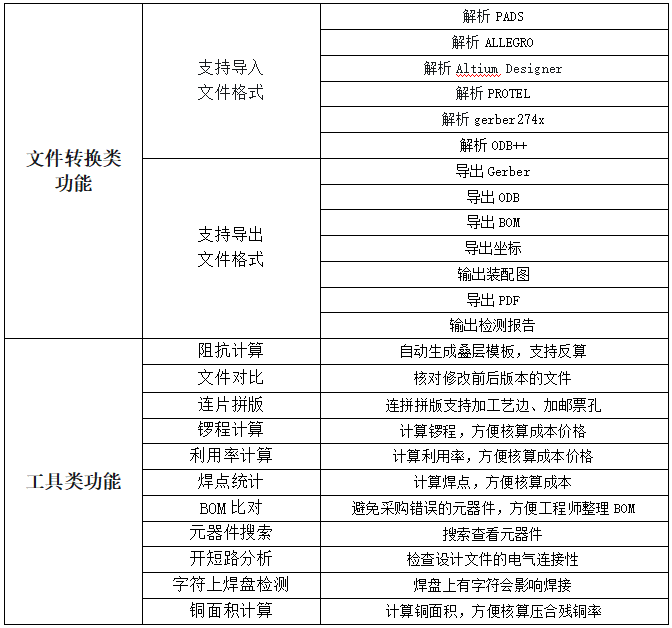

PCB 評審環(huán)節(jié)推薦大家使用華秋DFM!它全功能免費開放使用,并且能滿足工程師個人、公司的PCB DFM評審要求,支持一鍵DFM分析,導(dǎo)入PCB或者Gerber文件后就可以自動分析!

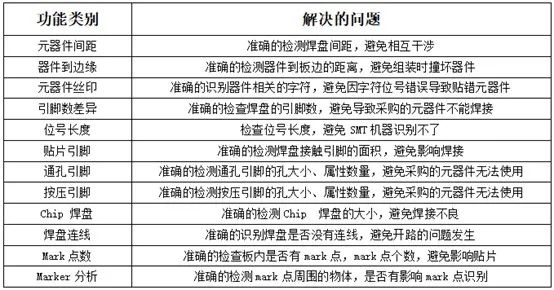

它具有10大項、234細(xì)項檢查規(guī)則,涵蓋所有可能發(fā)生的組裝性問題,比如器件分析,引腳分析,焊盤分析等,可解決多種工程師無法提前預(yù)料的生產(chǎn)情況。

工具是全中文界面,上手基本沒有任何難度。如果在使用中有什么不明白的地方,添加他們的在線客服,還可以實時答疑!簡直不要太方便!

工具下載地址(請復(fù)制到電腦端瀏覽器下載):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqdl_wz.zip

-

原理圖

+關(guān)注

關(guān)注

1322文章

6412瀏覽量

239245 -

pcb

+關(guān)注

關(guān)注

4354文章

23423瀏覽量

406899

發(fā)布評論請先 登錄

如何優(yōu)化您的PCB設(shè)計評審流程

ReviewHub:實現(xiàn)Booster與設(shè)計工具端無縫鏈接的評審協(xié)作平臺

Altium 365高效設(shè)計評審全攻略

西安 5月23-24日《PCB板電磁兼容設(shè)計與評審方法》公開課報名中!

【重磅喜訊】再獲國家認(rèn)可!賽盛檢測通過CNAS復(fù)評審

設(shè)計評審利器——在線評審工具ReviewHub

如何通過高效工程評審EQ流程,實現(xiàn)PCB零缺陷制造?

貝思科爾推出創(chuàng)新工具,限時免費試用

貝思科爾ReviewHub在線評審工具開放限時免費試用名額,快速領(lǐng)取!

貝思科爾DX-BST原理圖智能工具,限時免費試用開啟,不容錯過!

射頻電路分析 仿真 號完整性分析和自動控制理論

射頻電路工程師與模擬電路工程師 的技術(shù)要求

ad怎么實現(xiàn)原理圖與pcb元件對應(yīng)

Allegro X 23.11 版本更新 I PCB 設(shè)計:一鍵移除評審內(nèi)容 &amp; 導(dǎo)入ODB++

【經(jīng)驗分享】如何規(guī)劃原理圖設(shè)計評審(附PCB評審工具)

【經(jīng)驗分享】如何規(guī)劃原理圖設(shè)計評審(附PCB評審工具)

評論