聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

pcb

+關(guān)注

關(guān)注

4365文章

23481瀏覽量

409264

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

解鎖多軸直線電機(jī)模組的高效搭接方法

的應(yīng)用無處不在。而多軸直線模組的搭接方式,直接影響設(shè)備的運(yùn)行精度、穩(wěn)定性和使用壽命。掌握科學(xué)合理的搭接方法,是保障自動(dòng)化設(shè)備高效穩(wěn)定運(yùn)行的關(guān)鍵。多軸直線模組的常見

PCB插損和阻抗測(cè)試方案

邁進(jìn),通道配置從x1擴(kuò)展至x32,通過倍增頻率和通道數(shù)量實(shí)現(xiàn)大帶寬傳輸,然而,更高的信號(hào)頻率導(dǎo)致插入損耗呈指數(shù)級(jí)上升,引起信號(hào)幅度降低和失真,同時(shí),PCB走線中的阻抗不連續(xù)性會(huì)引發(fā)信號(hào)反射和時(shí)序抖動(dòng),它們共同造成信號(hào)完整性的問題

揭秘PCB阻抗控制:如何影響你的電子設(shè)備性能?

PCB貼片加工廠家今天為大家講講什么是PCB阻抗控制?PCB阻抗控制對(duì)電路性能和穩(wěn)定性的影響。在高頻、高速電子

精準(zhǔn)計(jì)算工具與干擾預(yù)判系統(tǒng)——賽盛計(jì)算工具介紹

SESSaishengOnline賽盛在線學(xué)習(xí)及工具應(yīng)用平臺(tái)平臺(tái)核心基于賽盛技術(shù)20年EMC工程經(jīng)驗(yàn),打造集學(xué)習(xí)、工具、案例與智能一體的綜合賦能平臺(tái)。專為解決電磁兼容領(lǐng)域的設(shè)計(jì)、

降銀的網(wǎng)版印刷技術(shù):無網(wǎng)結(jié)搭接對(duì)銀漿印刷形貌的影響與優(yōu)化

隨著全球能源需求的增長(zhǎng),太陽能電池技術(shù)迅速發(fā)展,成為可再生能源的重要組成部分。預(yù)計(jì)到2029年,太陽能電池板市場(chǎng)規(guī)模將突破700GW。本文探討了網(wǎng)版印刷技術(shù)對(duì)銀漿印刷形貌的影響,特別是網(wǎng)結(jié)搭接

2025賽盛技術(shù)培訓(xùn)事業(yè)全景規(guī)劃發(fā)布

2025新啟程在即將到來的2025年,賽盛將繼續(xù)致力于提升每一位電磁兼容工程師的專業(yè)技能,幫助大家更好地應(yīng)對(duì)日新月異的行業(yè)變化與不斷升級(jí)的職業(yè)挑戰(zhàn)。本期放送的培訓(xùn)課程,涵蓋行業(yè)前沿的技術(shù)知識(shí)和實(shí)戰(zhàn)

知識(shí)共享與案例管理——賽盛知識(shí)案例寶庫介紹

賽盛在線平臺(tái)SaishengOnline賽盛技術(shù)傾心打造的“賽盛在線學(xué)習(xí)及工具應(yīng)用”平臺(tái),核心理念是將學(xué)習(xí)與實(shí)踐緊密結(jié)合,打造一個(gè)互動(dòng)性強(qiáng)、

ISO3082DE和RE短接,為低電平時(shí),PC對(duì)其發(fā)數(shù)據(jù),無法接收,為什么?怎么解決?

ISO3082DE和RE短接,為高電平時(shí),對(duì)PC發(fā)送數(shù)據(jù),能正常接收。

但是DE和RE短接,為低電平時(shí),PC對(duì)其發(fā)數(shù)據(jù),無法接收。

單獨(dú)測(cè)試

發(fā)表于 12-03 07:31

影響PCB阻抗的三大因素

影響PCB阻抗的三大因素主要包括:介質(zhì)厚度、導(dǎo)線寬度和介電常數(shù)。 以下是詳細(xì)解釋: 1、介質(zhì)厚度(H): 介質(zhì)厚度與阻抗成正比,即介質(zhì)越厚,阻抗越大;介質(zhì)越薄,

精準(zhǔn)選型,高效設(shè)計(jì) —— 賽盛LC濾波工具介紹

,分別用于允許或阻止特定頻段的信號(hào)通過。如何使用賽盛在線平臺(tái)的“設(shè)計(jì)工具”模塊?以上展示均源自賽盛技術(shù)最新發(fā)布的賽盛在線學(xué)習(xí)及工具應(yīng)用平臺(tái)“

使用OPA547F搭的功率運(yùn)放,實(shí)際在空載下測(cè)試功能正常,但是芯片很燙怎么解決?

使用OPA547F搭的功率運(yùn)放,電路圖如下,輸出電流限制的100mA,實(shí)際在空載下測(cè)試功能正常,但是芯片很燙。

PCB中覆銅面積不是很大,想請(qǐng)問下:

1.這種狀態(tài)正常嗎?

2.什么原因導(dǎo)致

發(fā)表于 08-16 08:38

【電磁兼容技術(shù)案例分享】某產(chǎn)品因LVDS導(dǎo)致靜電放電測(cè)試FAIL整改案例

【電磁兼容技術(shù)案例分享】某產(chǎn)品因LVDS導(dǎo)致靜電放電測(cè)試FAIL整改案例

賽盛集團(tuán)電磁兼容工程技術(shù)中心落成慶典圓滿舉行

發(fā)展上的堅(jiān)定步伐。慶典活動(dòng)從領(lǐng)導(dǎo)致辭開始,賽盛集團(tuán)電磁兼容總工程師石光其向到場(chǎng)的嘉賓們介紹了工程技術(shù)中心的重要意義及其未來發(fā)展規(guī)劃。緊接著是隆重的揭幕儀式和剪彩儀式

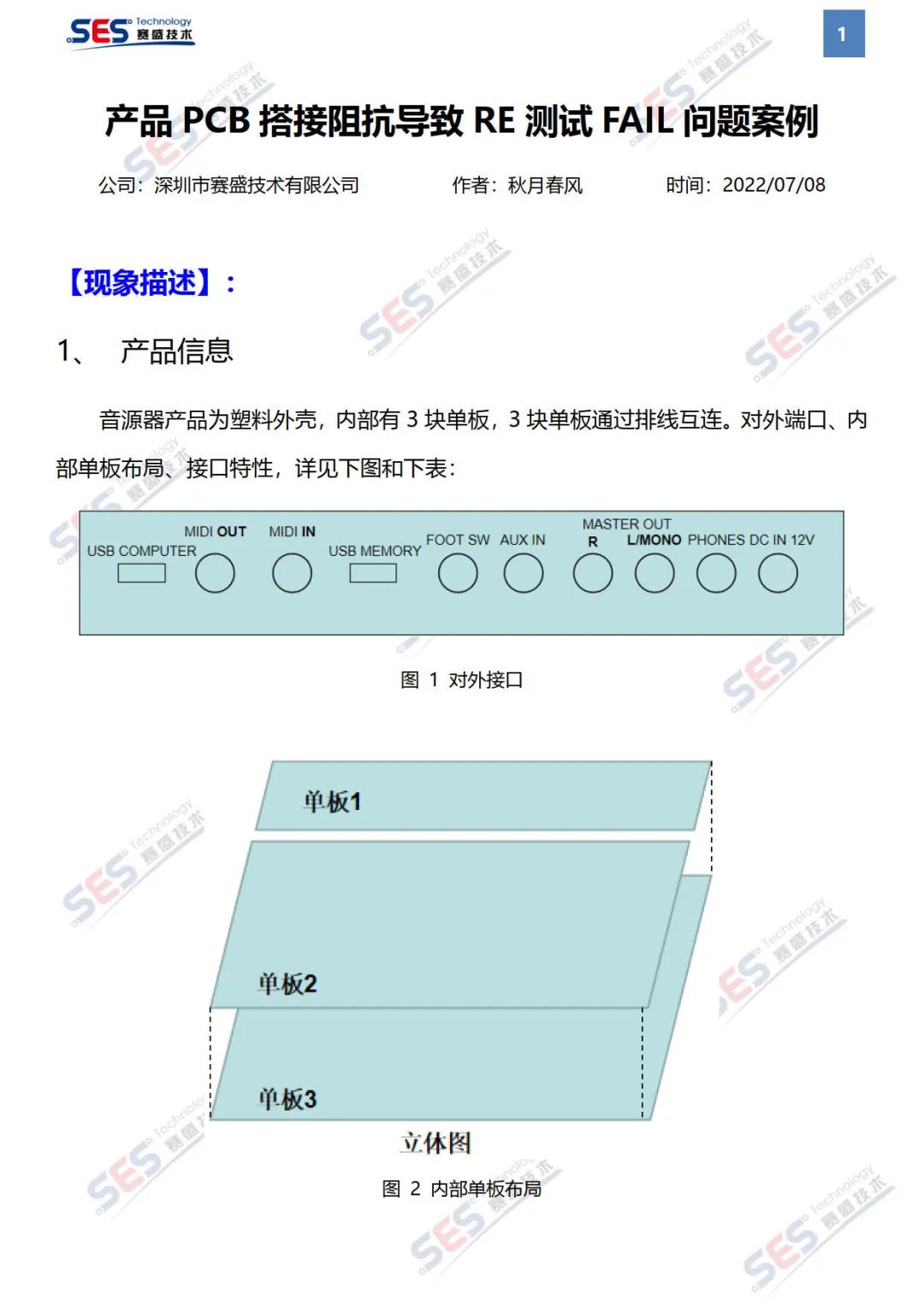

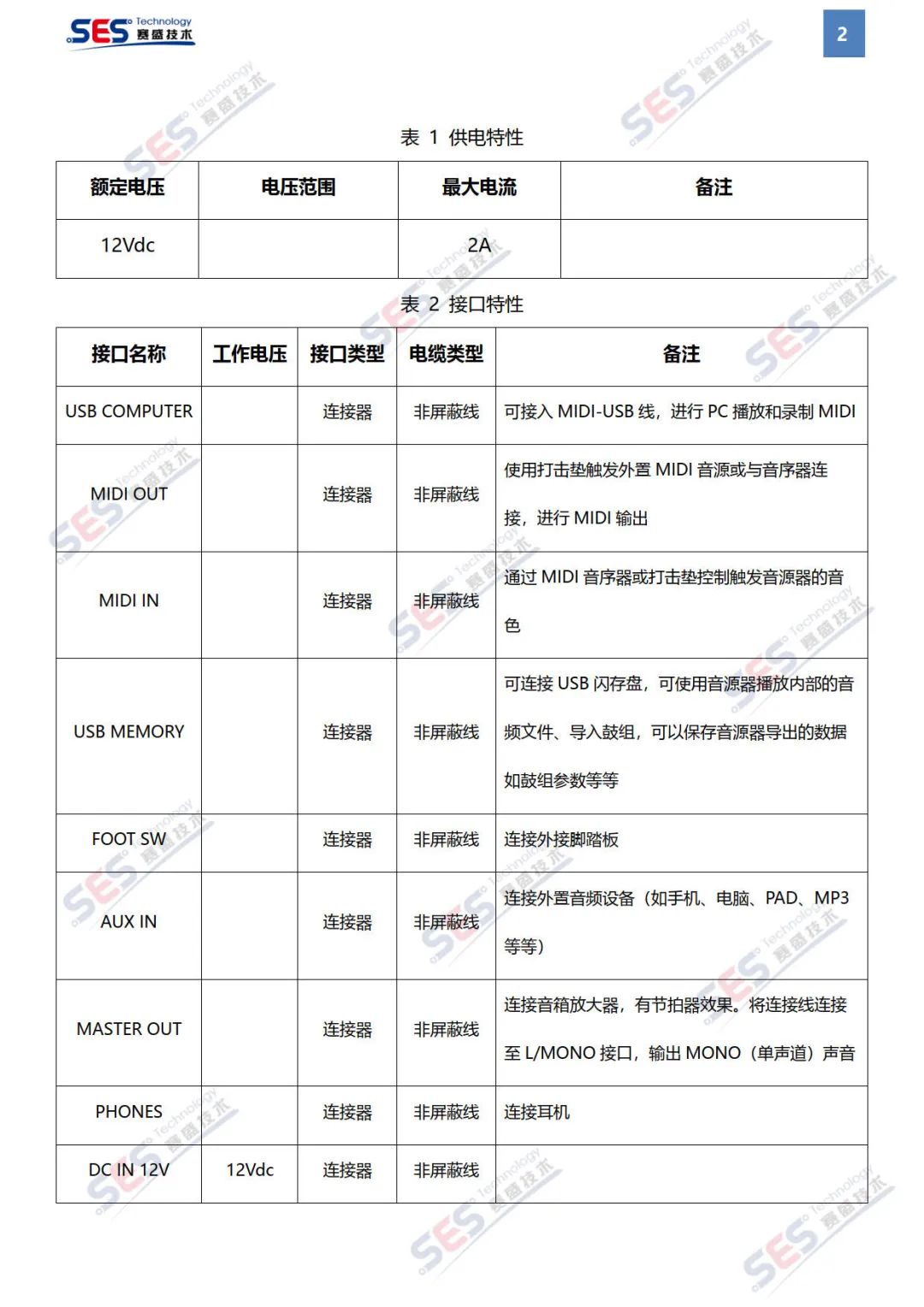

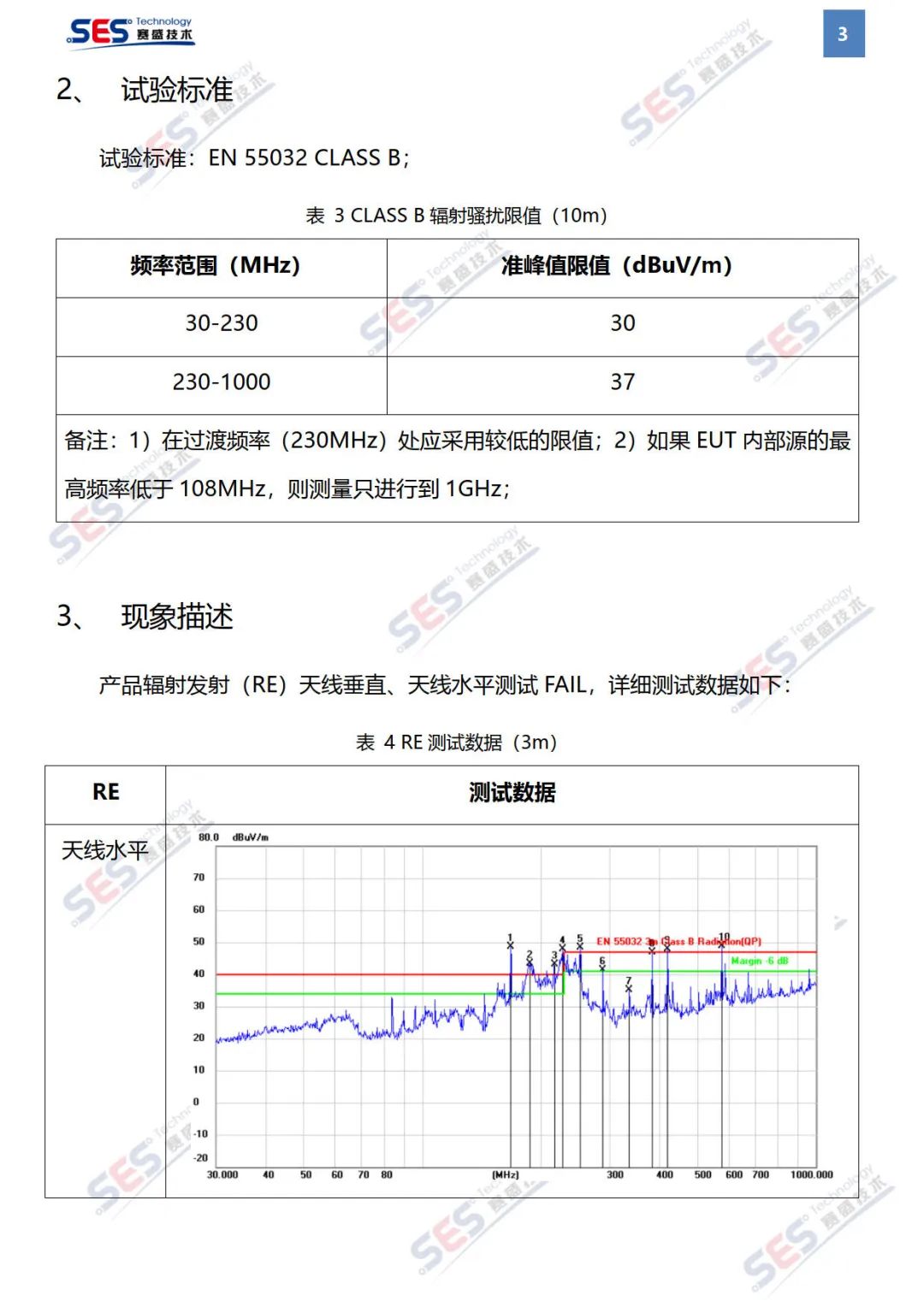

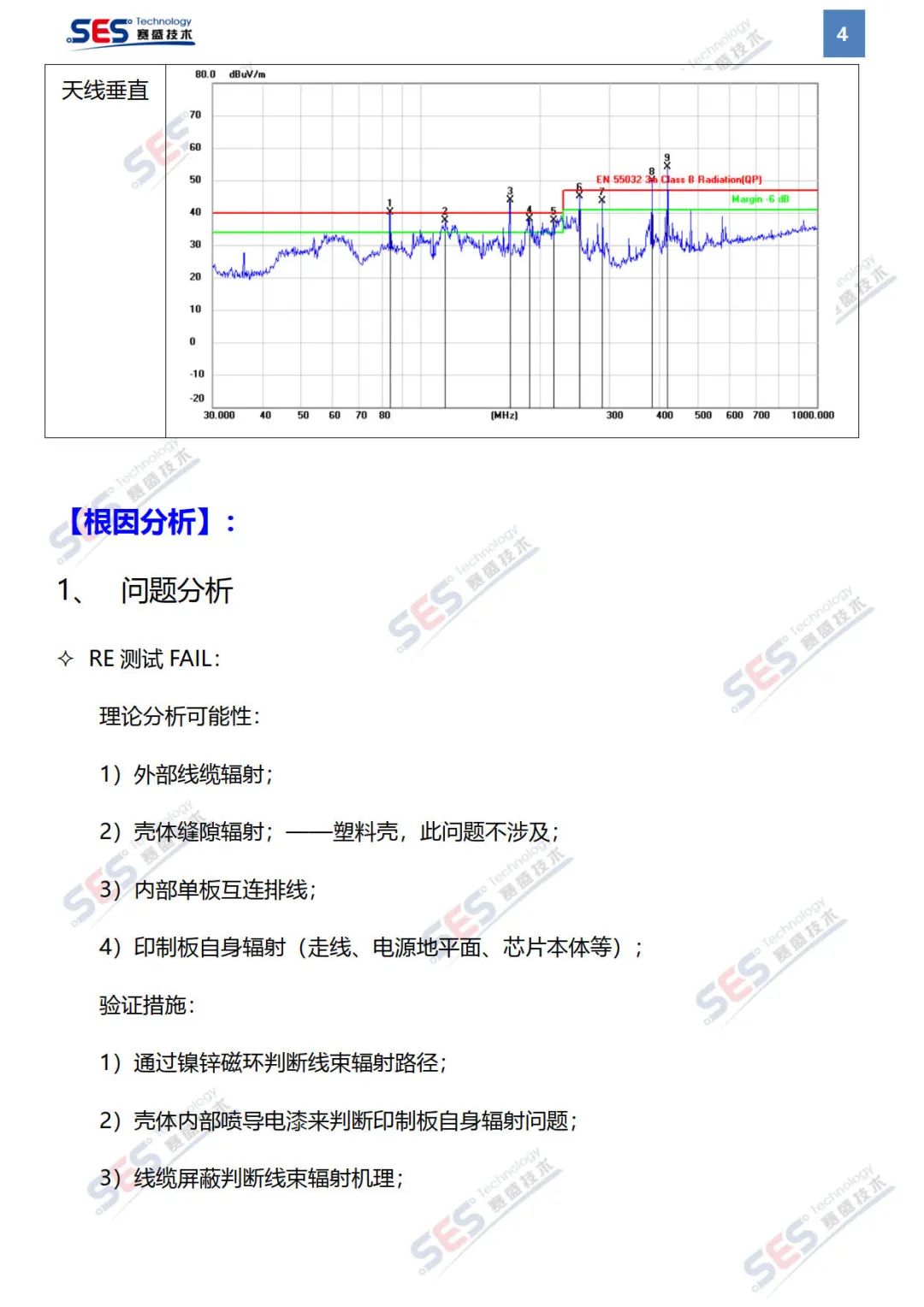

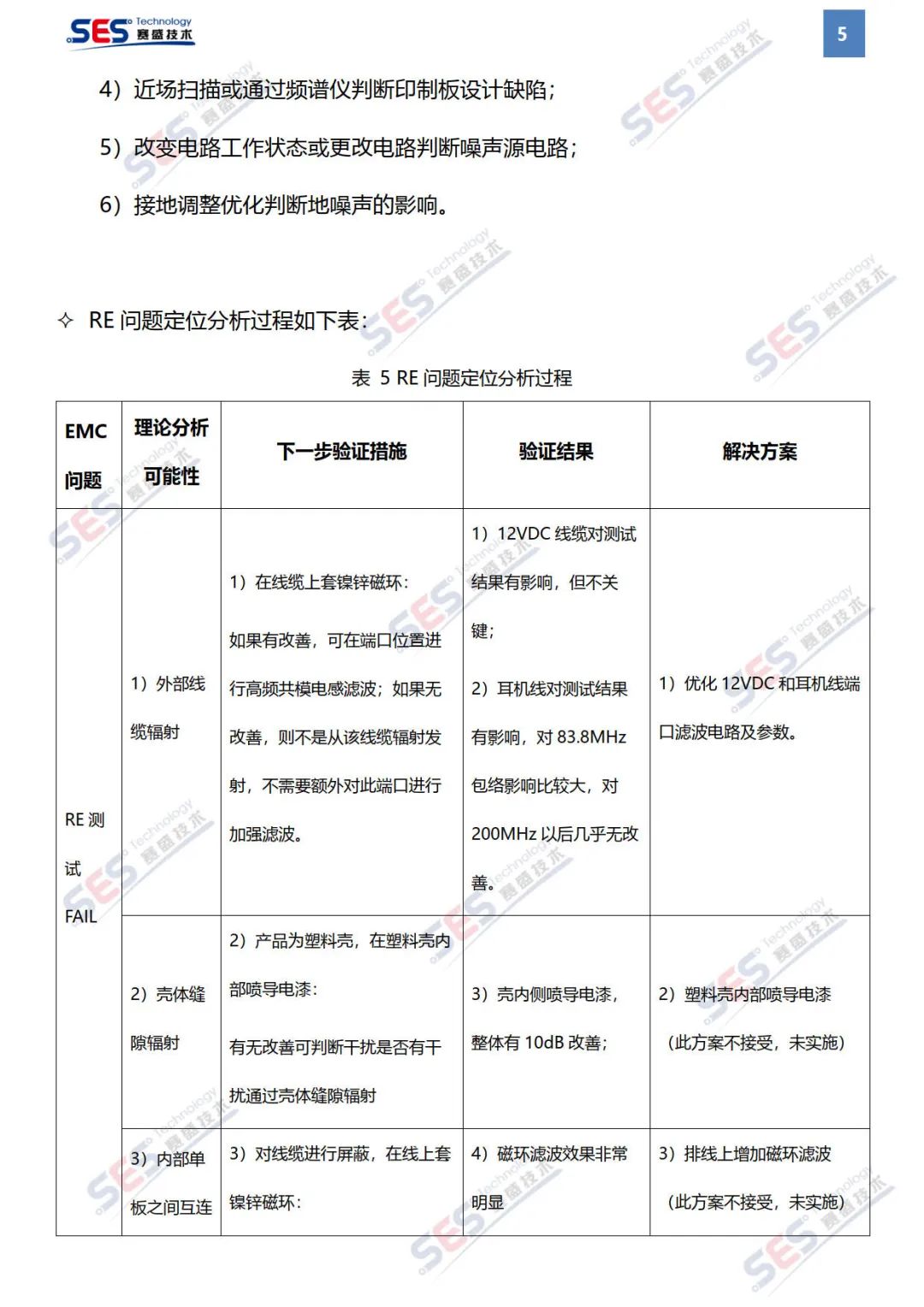

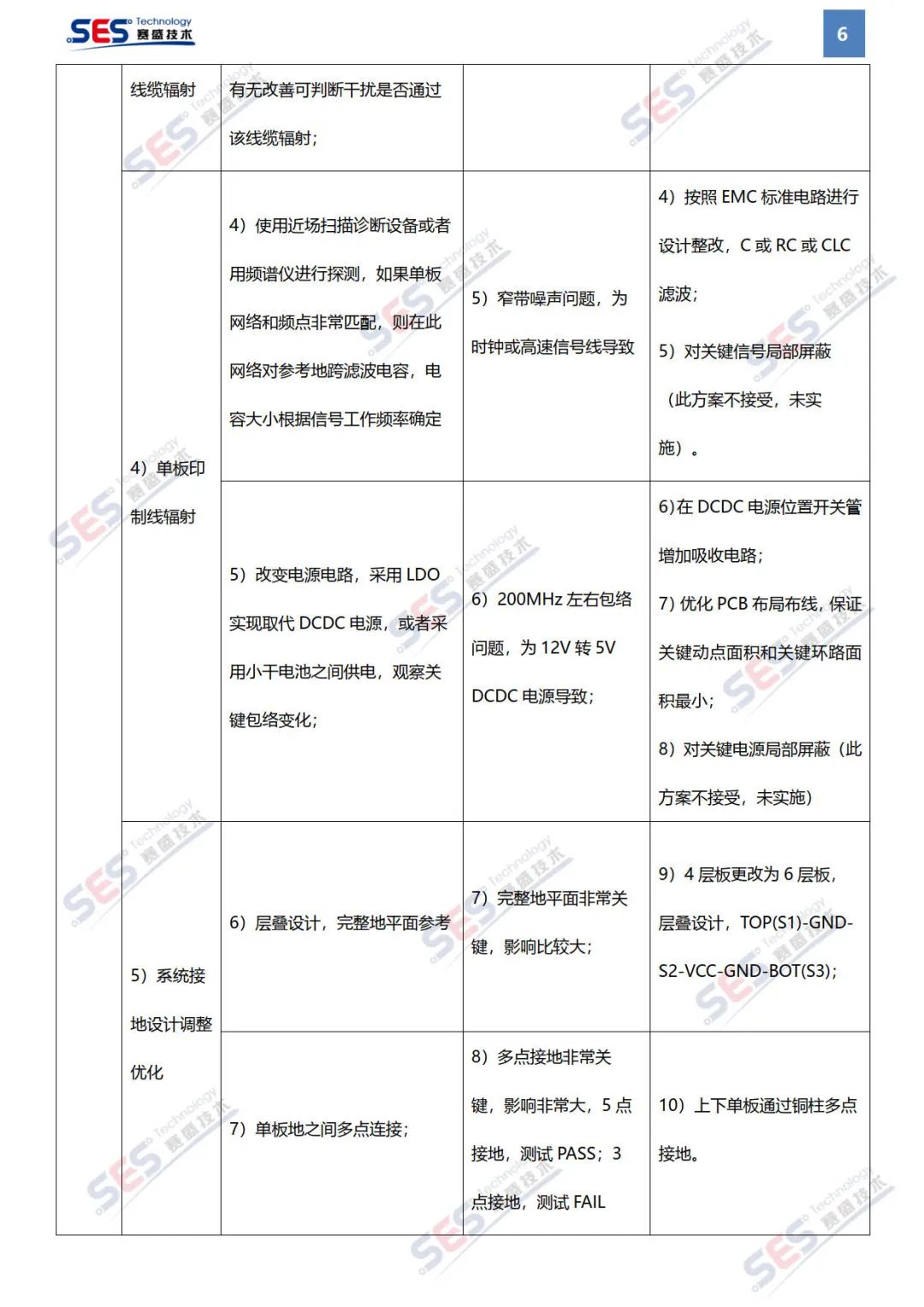

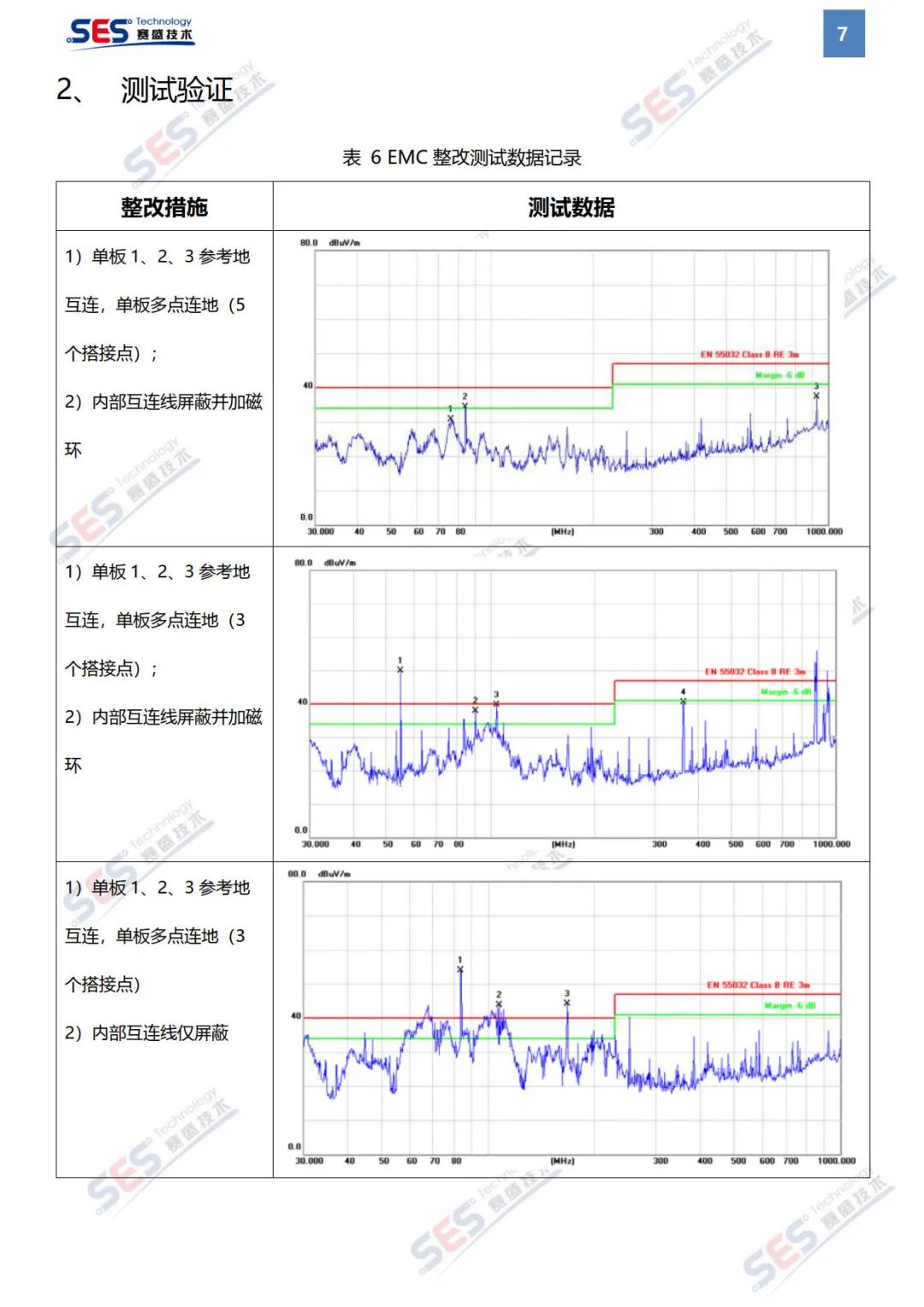

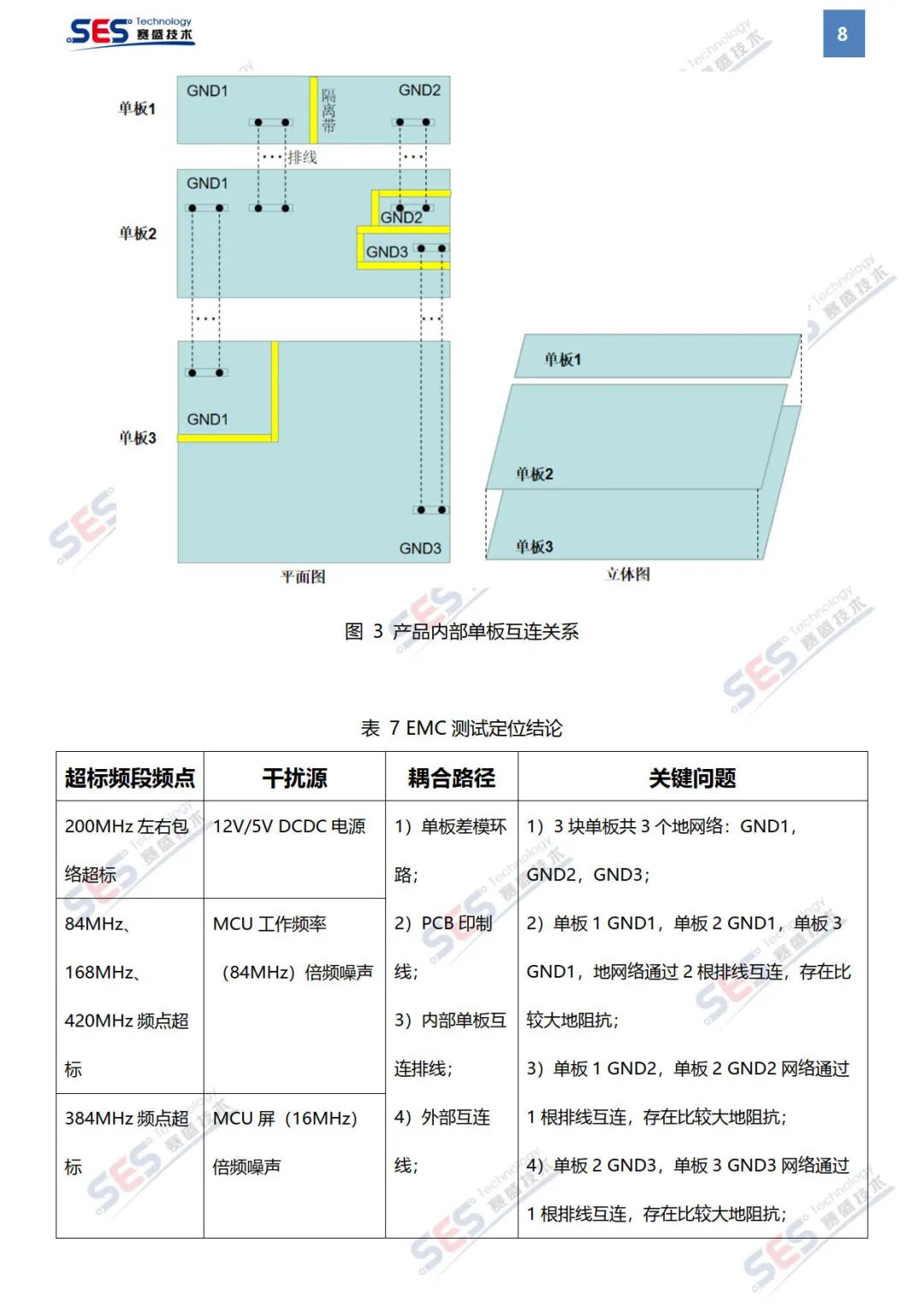

【賽盛技術(shù)案例分享】產(chǎn)品PCB搭接阻抗導(dǎo)致RE測(cè)試FAIL問題案例

【賽盛技術(shù)案例分享】產(chǎn)品PCB搭接阻抗導(dǎo)致RE測(cè)試FAIL問題案例

評(píng)論