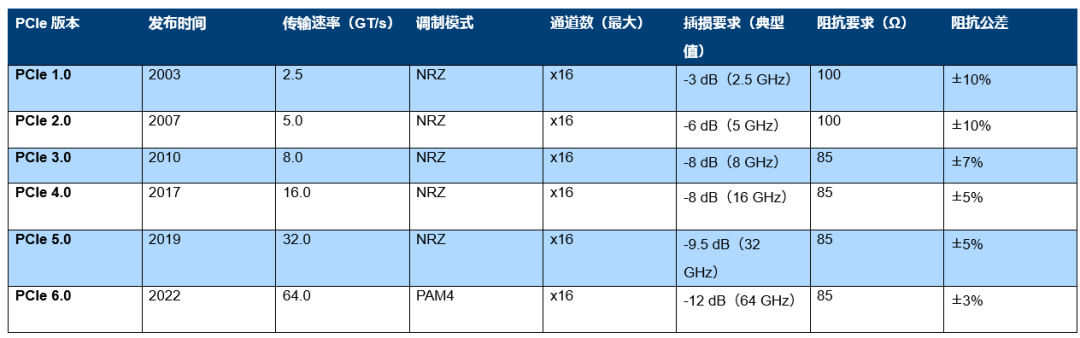

隨著AI技術(shù)的快速興起,服務器及計算設備對數(shù)據(jù)總線的吞吐量需求呈現(xiàn)指數(shù)級增長,以PCIe標準為例,為適應AI算力需求,其協(xié)議已升級至PCIe 5.0/6.0,信號頻率突破32GT/s并向64GT/s邁進,通道配置從x1擴展至x32,通過倍增頻率和通道數(shù)量實現(xiàn)大帶寬傳輸,然而,更高的信號頻率導致插入損耗呈指數(shù)級上升,引起信號幅度降低和失真,同時,PCB走線中的阻抗不連續(xù)性會引發(fā)信號反射和時序抖動,它們共同造成信號完整性的問題。

表1:PCIe總線圖表

為應對這些挑戰(zhàn), PCIe阻抗測試需嚴格控制100Ω±10%的差分阻抗(PCB走線),并通過預加重、均衡技術(shù)補償損耗,插入損耗達-12dB@9GHz時,需+6dB的均衡增益才能恢復有效信號。此外,PCIe 5.0要求使用超低損耗(Df≤0.002)覆銅板,并增加板層數(shù)以優(yōu)化布線,但這也使阻抗控制成為核心難點。因此,從設計仿真到量產(chǎn)測試,阻抗一致性和損耗補償能力已成為保障PCIe高帶寬穩(wěn)定傳輸?shù)年P鍵技術(shù),準確、高效且便捷地測試插入損耗和阻抗成為市場的緊迫需求。

本文主要概述PCB插損和阻抗的基本認知,測試方法和介紹羅德與施瓦茨公司對應的測試方案。

01.插損與阻抗的定義及影響

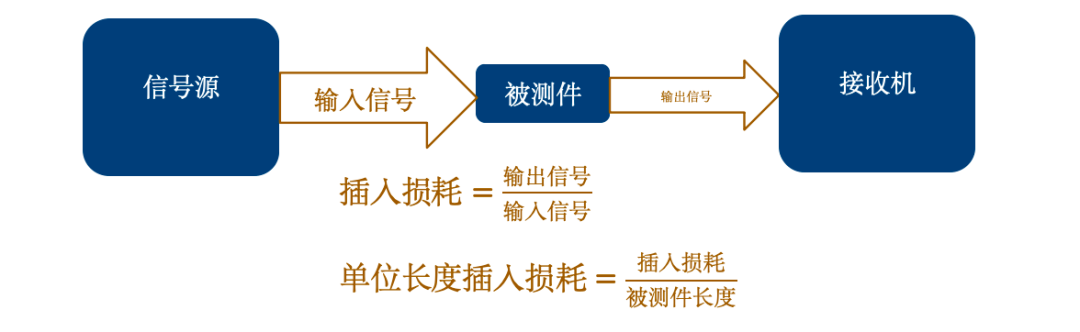

1插入損耗(Insertion Loss)

指信號通過PCB傳輸線時因?qū)w損耗、介質(zhì)損耗等因素導致的功率衰減,通常以分貝(dB)表示。例如,PCIe 5.0要求每英寸插損不超過0.6 dB@16 GHz。

圖1:信號與插入損耗的關系

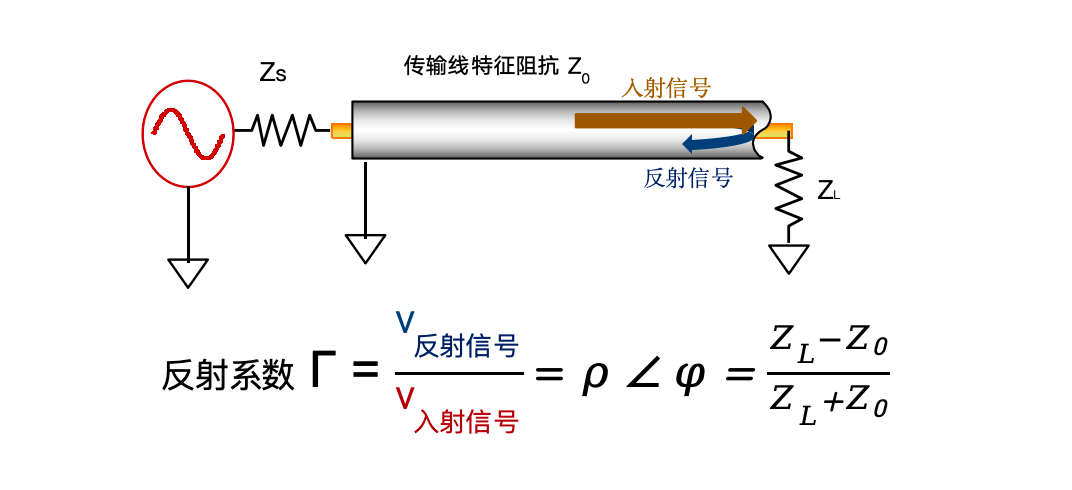

2特征阻抗(Characteristic Impedance)

特征阻抗由傳輸線的幾何結(jié)構(gòu)和材料特性決定,通常推薦值為50Ω或100Ω(差分)。阻抗突變會引發(fā)信號反射,導致回波損耗(Return Loss)惡化,影響信號完整性。

圖2:阻抗失配與信號反射系數(shù)的關系

02.測試方法

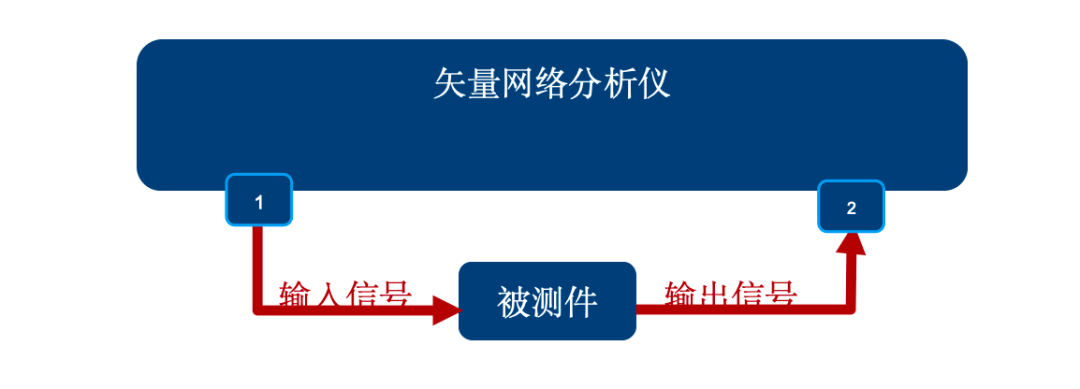

1插入損耗的測量

矢量網(wǎng)絡分析儀(VNA)是測量插入損耗最便捷的儀表,它的每個端口內(nèi)部包含有信號源和接收機,我們可以通過端口1的信號源發(fā)出信號給被測件,再由端口2的接收機測量經(jīng)由被測件處理后的輸出信號,矢網(wǎng)可以直接比較和顯示輸出信號和輸入信號的差異,即為直接測量S21參數(shù)(正向傳輸系數(shù)),從而直觀的反映信號從輸入到輸出的損耗。

圖3:插損測量

單位長度的插入損耗是PCB設計和信號完整性分析中一個非常重要的指標。它不僅可以幫助我們評估傳輸線的性能,還可以為電路設計提供更準確的數(shù)據(jù)支持,從而提高產(chǎn)品的可靠性和性能

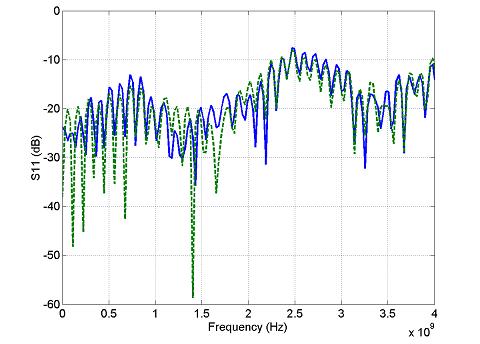

圖4:Delta L 結(jié)果顯示

單位長度插入損耗直觀上可以用直接除法,即插入損耗除以被測件長度,然而,如圖4藍色測試結(jié)果所示,高頻下被測件阻抗不匹配導致的多重反射引發(fā)測試結(jié)果在不同頻率之間存在波動,影響測試精度和穩(wěn)定性。

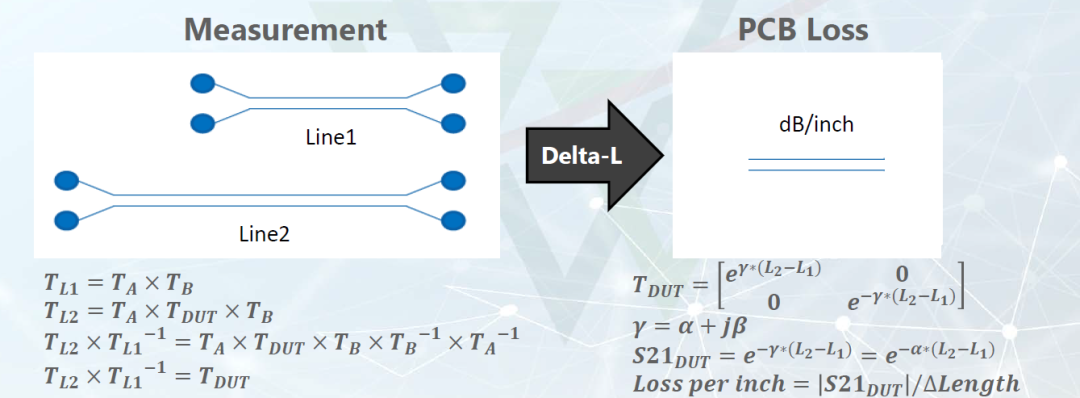

Delta-L方法是Intel開發(fā)的,通過設計兩條不同長度的傳輸線,測試它們的S參數(shù)后進行擬合運算和差值,從而得到單位長度的插入損耗。相比直接除法,Delta L在計算差值時自動抵消了夾具(如探針、焊盤和過孔)的影響,擬合算法移除了阻抗不匹配導致的多重反射,使得其尤其在高速、高頻場景下顯著提升了精度和穩(wěn)定性,從而成為當前PCB量產(chǎn)測試的主流方法。

圖5:Delta L 差值算法

2阻抗測試

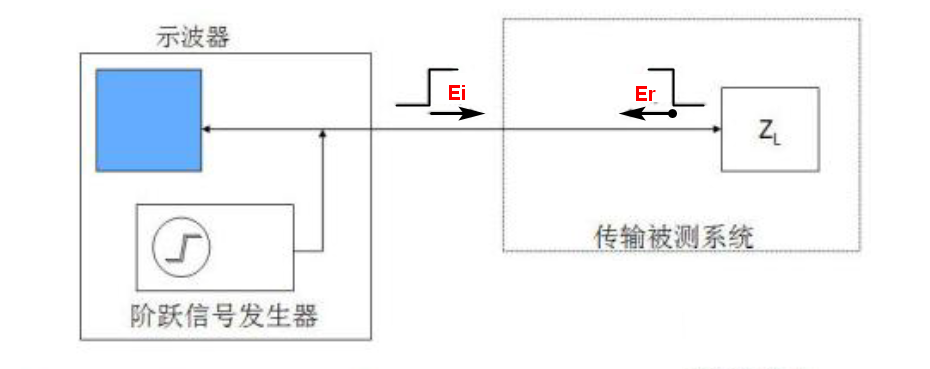

傳統(tǒng)阻抗測試是基于示波器時域反射計(TDR),信號發(fā)生器產(chǎn)生階躍激勵或者脈沖激勵,示波器對入射信號和反射信號采樣,計算出時域數(shù)據(jù)。

圖6:傳統(tǒng)TDR阻抗測試計

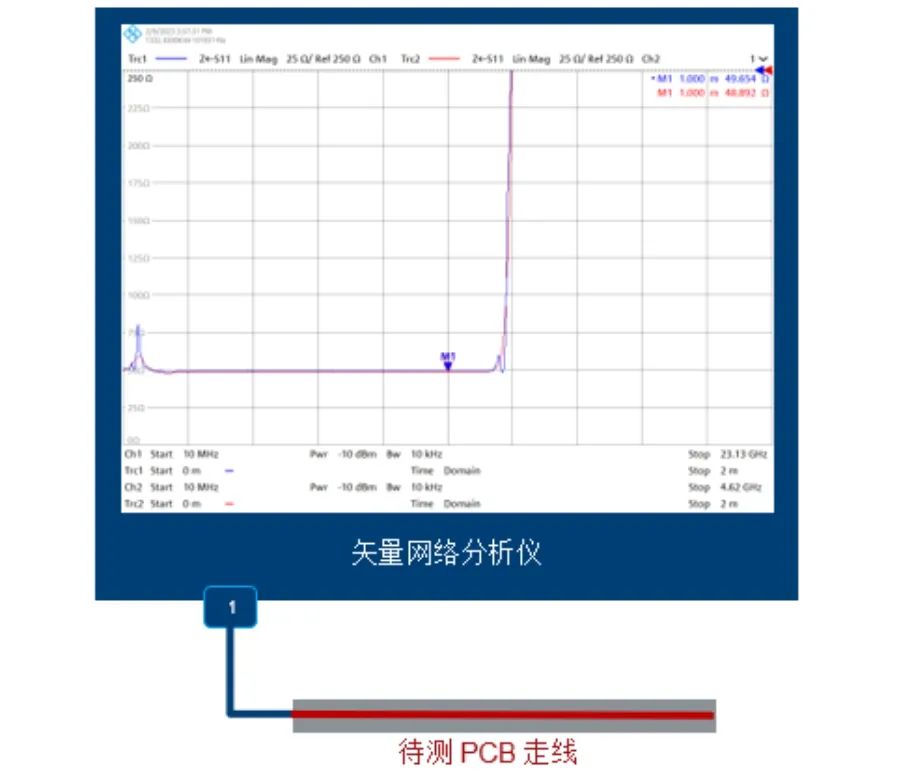

相比示波器受限于噪聲,動態(tài)范圍和帶寬等,矢量網(wǎng)絡分析儀因其更高的精度、測試速度以及ESD魯棒性,隨著工作頻率升高,基于矢量網(wǎng)絡分析儀的TDR阻抗測試儀成為主流;矢量網(wǎng)絡分析儀同樣采用TDR時域反射法,不同于傳導的TDR阻抗分析儀以高壓脈沖為激勵信號,它是通過發(fā)射掃頻連續(xù)波,再接收源信號與散射信號并進行比值,然后將測得的頻域數(shù)據(jù)進行時域變換,得到時域阻抗結(jié)果。

圖7:基于矢網(wǎng)的TDR阻抗測試

03.羅德與施瓦茨的測試解決方案

羅德與施瓦茨(Rohde & Schwarz)作為全球測試測量領域的領導者,其矢量網(wǎng)絡分析儀產(chǎn)線覆蓋全面,滿足從基礎研發(fā)到高端應用的多樣化需求。產(chǎn)品包括R&SZNA、R&SZNB、R&SZNBT 和 R&SZNL等多個系列,頻率范圍涵蓋9kHz至110GHz。

1插損測試

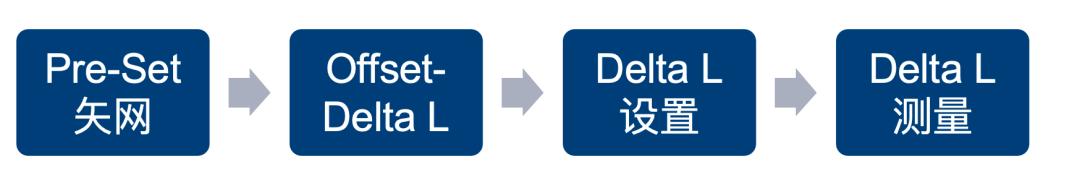

羅德矢網(wǎng)內(nèi)嵌Detal-L功能件,無需外部電腦,通過簡易幾步即可完成插入損耗測試。

圖8:Delta-L 測試流程

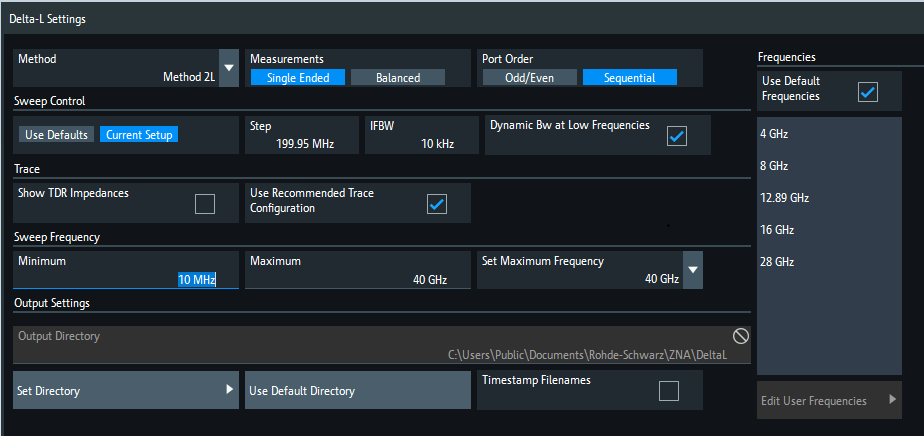

其中Delta L 設置中,可以完成矢網(wǎng)的基本設置如掃描帶寬,步進等,除Delta L算法標準設定外,羅德矢網(wǎng)支持用戶可以自定義測量方法,任意設定最高工作頻率(最高受限于矢網(wǎng)自身最高工作頻率)和定點的頻率用于結(jié)果顯示。

圖9:Delta L 設置界面

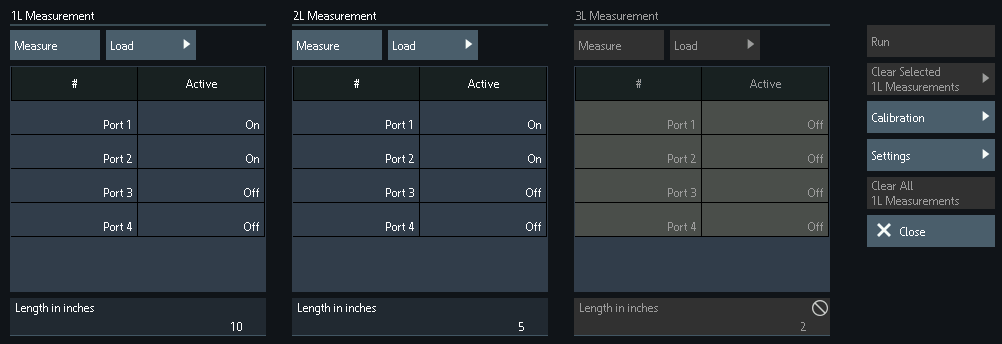

Delta L測量設置中內(nèi)嵌校準,配屬羅德自動校準件可以輕松快捷完成矢網(wǎng)自身誤差和用于連接的線纜的誤差校準,且除Delta L算法標準設定被測件長度外,羅德矢網(wǎng)支持用戶靈活配置被測件長度。

圖10:Delta L 測量設置

2阻抗測試

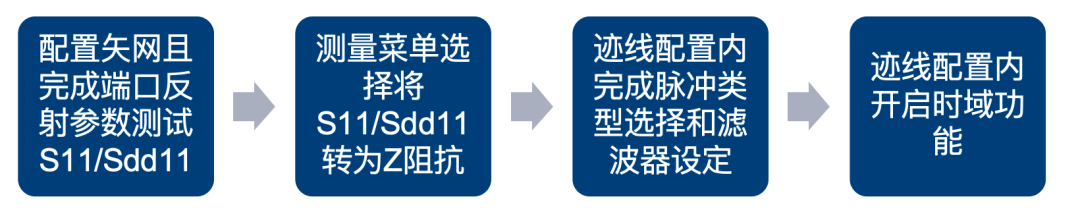

羅德矢網(wǎng)內(nèi)嵌TDR功能件,無需外部電腦,通過簡易幾步即可完成阻抗測試。

圖11:矢網(wǎng)TDR測試流程

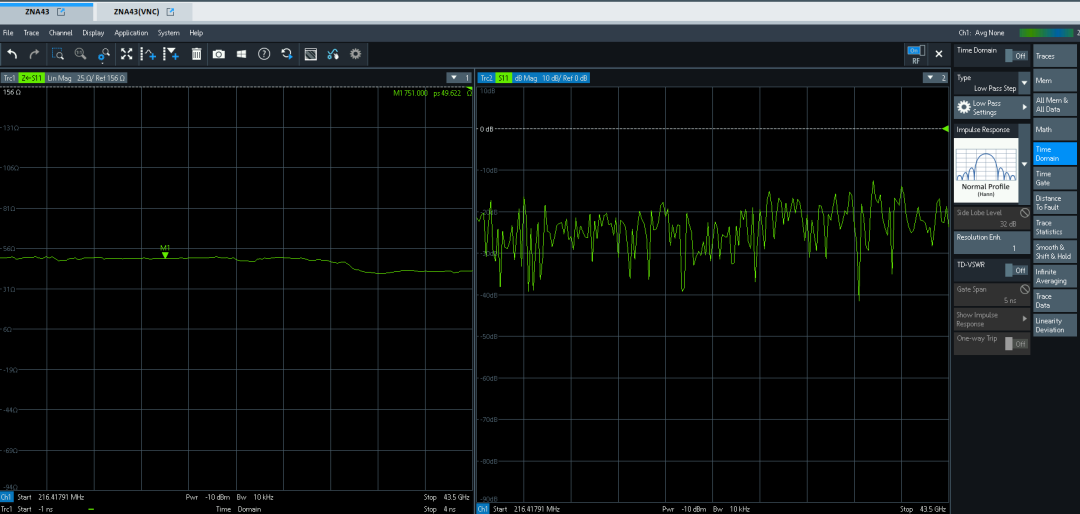

羅德矢網(wǎng)TDR支持多種窗函數(shù)和時域精度增強算法,同時顯示阻抗和頻域的S參數(shù)信息,方便用戶對比時頻域信息和問題診斷。

圖12:矢網(wǎng)TDR阻抗結(jié)果顯示

羅德與施瓦茨矢量網(wǎng)絡分析儀還可以搭配第三方測試軟件進行自動化測試,軟件可按照用戶定義好的測試內(nèi)容執(zhí)行測試,比如信號完整性要求的測試項:插入損耗、回波損耗、遠近端串擾、TDR、Skew、Delta-L等,用戶一鍵式執(zhí)行測試,最后生產(chǎn)完整測試報告,非常高效。

總 結(jié)

羅德與施瓦茨的ZNA/ZNB/ZNL系列配屬有電子校準件,內(nèi)置阻抗測試功能和Delta L 測量選件,以自動化、高精度重新定義了PCB插損與阻抗測試的標桿。面對未來6G通信與AI服務器的更高需求,該方案通過軟硬件協(xié)同創(chuàng)新,為行業(yè)提供了從研發(fā)到量產(chǎn)的完整閉環(huán)工具。

羅德與施瓦茨業(yè)務涵蓋測試測量、技術(shù)系統(tǒng)、網(wǎng)絡與網(wǎng)絡安全,致力于打造一個更加安全、互聯(lián)的世界。成立90 年來,羅德與施瓦茨作為全球科技集團,通過發(fā)展尖端技術(shù),不斷突破技術(shù)界限。公司領先的產(chǎn)品和解決方案賦能眾多行業(yè)客戶,助其獲得數(shù)字技術(shù)領導力。羅德與施瓦茨總部位于德國慕尼黑,作為一家私有企業(yè),公司在全球范圍內(nèi)獨立、長期、可持續(xù)地開展業(yè)務。

-

pcb

+關注

關注

4351文章

23405瀏覽量

406627 -

服務器

+關注

關注

12文章

9681瀏覽量

87261 -

PCIe

+關注

關注

16文章

1322瀏覽量

84658 -

差分阻抗

+關注

關注

1文章

27瀏覽量

10481 -

阻抗測試

+關注

關注

0文章

10瀏覽量

1751

原文標題:【儀測高下】PCB插損和阻抗測試方案

文章出處:【微信號:羅德與施瓦茨中國,微信公眾號:羅德與施瓦茨中國】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

USB 3.0線纜和連接器的阻抗和插損測試

USB 3.0線纜和連接器的阻抗和插損測試

PCB阻抗測試,是怎么測出來的

PCB高速信號阻抗測試技巧分享

OFDR測試光纖鏈路大插損怎么測?

昊衡科技:OFDR測試光纖鏈路大插損-怎么測?

插損,回損測量方法是什么

帶通濾波器的插損與哪些因素有關?

請問什么原因?qū)е略谄ヅ湔G闆r下,插損出現(xiàn)周期性諧振?

pcb阻抗測試方法有哪些 影響PCB阻抗的六大因素

M12航空插頭6芯插損的影響

PCB插損和阻抗測試方案

PCB插損和阻抗測試方案

評論